Mentor

Mentor/Arm攜手優化下一代IC功能驗證

Mentor近日與Arm深化合作,協助積體電路(IC)設計人員優化其基於Arm設計的功能驗證。透過此項合作,Arm設計審閱計畫(Design Reviews Program)現可向客戶提供Mentor功能驗證工具的專業知識,藉以優化基於Arm的晶片級系統(SoC)設計。

Arm與 Mentor合作推出的RTL驗證設計審閱(Verification Design Review)服務,可幫助IC設計團隊在RTL層級為其Arm IP取得品質、先進功能和成本之間的適當平衡,同時協助客戶強化一系列關鍵的設計要素,包括訊號連接性、系統一致性、正確的建置和系統效能等等。

Mentor Consulting副總裁Sam George表示,Mentor和Arm擁有良好的合作實績,很高興這一合作關係能夠繼續展開。Mentor對於 RTL設計的專業知識與Arm完備的系統設計知識相結合,能夠為雙方的共同客戶提供寶貴的知識資源。

在SoC的設計過程中,對於新IC的驗證通常會占據一半以上的用時。當下的設計團隊需要使用更複雜的設計來滿足汽車、工業設備、醫療和物聯網市場的終端應用需求,因此IC功能驗證週期的有效管理變得更加重要。Arm和Mentor的合作目的在於通過優化和縮短驗證週期來協助共同客戶克服這些挑戰。

Mentor在電子設計自動化(EDA)市場已累積了數十年的專業經驗,以其IC功能驗證的技術享譽全球,許多業内創新的成功產品都是基於Mentor技術所開發。

Arm Partner Enablement副總裁暨總經理Ciarán Dunne表示,驗證是SoC設計過程中不可忽視的關鍵環節。新的RTL驗證設計審閱服務可提供Arm和Mentor共享的見解和專業知識,使客戶進一步提高設計品質,縮短設計週期,加速產品上市時程並降低專案風險。

格羅方德/Mentor合作推出ML晶片設計驗證方案

格羅方德日前在年度全球技術大會(GTC)上發表新款可製造性設計(DFM)套件,該產品在機器學習(ML)功能的協助下,性能大幅提升。這款ML增強型DFM解決方案,由格羅方德與西門子旗下的明導(Mentor)共同開發,並透過Mentor的Calibre nmDRC平台打造,為客戶提供更有效的設計和開發體驗,以縮短交貨時間為終極目標。

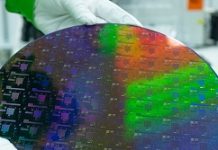

格羅方德日前在GTC上發表DFM套件 圖片來源:羅德方格

在格羅方德推出差異化的12LP+半導體解決方案後,新款ML增強型DFM套件可謂其製程設計套件(PDK)的更新版。12LP+建立在具備完整生產生態系統的平台上,針對AI培訓和推理應用進行最佳化,目前已準備在美國紐約州馬爾他的晶圓8廠(Fab 8)進入生產階段。

自2009年成立以來,格羅方德率先開發出一套名為DRC+的DFM檢查平台,該平台結合了電子設計自動化(EDA)軟體的各類模式配對工具,並搭配良率減損器模式庫(Proprietary Library of Yield Detractor Patterns)。DRC+能讓晶片設計工程師預先偵測出早期設計中的瑕疪模式或熱點,避免潛在的製造缺陷。

格羅方德與明導合作將格羅方德開發的ML模型整合到DRC+中,藉此增強DRC +的識別能力,偵測出前所未見的新熱點模式並改善產能。拜格羅方德於製造過程中所蒐集的矽數據所賜,新款ML增強型DFM套件經訓練後已通過驗證,足以讓晶片設計工程師在設計初期發現並緩解潛在問題時更加順利。對於致力成功原型設計和規模製造的設計工程師而言,在開發階段找出並解決這些熱點問題至關重要。

格羅方德的12LP+ 專為滿足快速增長的AI市場特定需求所設計,可針對性能、功率和面積效率等方面提供最佳組合。幕後新功臣則包括更新後的標準元件庫、用於2.5D封裝的中介層,以及低功耗的0.5V Vmin SRAM位單元,以支援AI處理器和記憶體之間的低延遲和低功耗數據往返。

12LP+平台以格羅方德14nm/12LP平台為基礎,目前已出貨超過一百萬片晶圓。12LP+平台的性能之所以超越12LP,在於將SoC級邏輯性能提高20%,以及邏輯區域縮放方面提高10%。而這些進步的實現,可歸功於12LP+平台的下一代標準單元庫,因其具備性能驅動的面積最佳化組件、單一Fin單元、新款低電壓SRAM位單元,以及改良後的類布局設計規則。

Mentor通過台積電3奈米製程技術認證

Mentor近期宣布旗下多項產品線和工具已獲得台積電(TSMC)最新的3奈米(N3)製程技術認證。

台積電設計建構管理處資深處長Suk Lee表示,此次認證進一步突顯了Mentor為雙方共同客戶以及台積電生態系統所創造的價值。很高興看到一系列Mentor的平台正在不斷通過台積電認證,客戶能夠以此運用最先進的製程技術,在功耗和效能方面取得大幅提升,進而實現成功的晶片設計。

目前已通過台積電N3製程認證的Mentor產品包括Analog FastSPICE平台,該平台可為奈米级類比、射頻(RF)、混合訊號、記憶體和客制化數位電路提供先進的電路驗證。

Mentor還同時擴展了其Xpedition軟體對台積電2.5/3D產品的支援,包括用於設計規劃和網表的Xpedition Substrate Integrator、和用於布局的Xpedition Package Designer,經過增强後的Xpedition Package Designer現可滿足台積電的InFO技術要求。此外,Mentor Calibre實體驗證平台中的3Dstack技術還透過對CoWoS-S的支援,擴展了對台積電「晶粒之間」(inter-die)LVS的支援。

Mentor的IC驗證平台 Calibre nmPlatform也有多項產品獲得了台積電N3和N5製程認證,其中包括Calibre nmDRC和Caliber nmLVS工具套件—用於IC實體和電路驗證sign-off。Calibre在每個新製程上持續改進和開發新功能,同時提供良好的高準確性,可擴展性和周轉時間。如Caliber PERC可靠性平台,能夠對實體布局和網表進行獨特的整合分析,可自動執行複雜的可靠性驗證檢查。同時,Mentor還與台積電合作為ESD(靜電放電)和閂鎖(Latch-Up)驗證提供更加完備的功能。

而Calibre xACT寄生參數提取解決方案—可提供三維FinFET架構所需的高準確度,並協助Mentor和台積電的客戶充分發揮台積電3奈米製程的效能優勢。

Mentor IC EDA執行副總裁Joe Sawicki表示,Mentor和台積電將繼續發揮雙方的合作優勢,為共同客戶提供良好的解決方案。台積電的3奈米製程技術是當前最先進的製程技術,它不僅僅為全球客戶提供了優異的效能和功率效率,同時也再一次向業界證明,摩爾定律迄今依然行之有效。

Mentor EDA軟體支援三星Foundry 5/4奈米製程技術

Mentor旗下的Calibre nmPlatform和Analog FastSPICE(AFS)自訂和類比/混合訊號(AMS)電路驗證平台已通過三星Foundry的最新製程技術認證。客戶現在可以在三星的5/4奈米FinFET製程上使用這些產品,為其先進的IC設計Tapeouts進行驗證和Sign-off。

三星5奈米FinFET製程具備優異的功率、效能和面積(PPA)特性,其自身的增強功能,結合更精細的5奈米幾何尺寸,能夠提供比前幾代製程節點更加突出的效能表現。而除Calibre nmDRC之外,通過三星Foundry新製程認證的Mentor工具還包括:

Calibre xACT可解決與先進奈米設計相關的技術挑戰,包括多重曝光、局部互連、高複雜度和嚴苛的約束條件等。其獨特的混合引擎可為FinFET這類細微的3D結構提供至關重要的場解算器準確度,並具備快速處理能力。

Calibre YieldEnhancer具有SmartFill和ECO Fill功能,客戶可控制設計平面度並縮短反覆設計的周轉時間,且可透過自動化PowerVia流程減少IR壓降,協助客戶提高設計可靠度。

Calibre PERC能夠對實體布局和網表進行獨特的整合分析,自動執行複雜的可靠度驗證檢查,協助客戶克服靜電放電和閂鎖(Latch-up)可靠度的相關挑戰。

Calibre nmLVS可作為三星Foundry萃取流程的前端。因應不斷增加的布局複雜度要求,以及設計團隊對先進運算的更高需求,使在驗證複雜電路的同時,仍能在預期的執行時間内達成先進製程節點的設計目標。

Calibre RealTime數位和自訂介面平台利用同樣通過三星Foundry認證予批量Calibre的設計套件,在數位和自訂設計流程中即時地實現sign-off質量的DRC檢查。在先進和成熟節點設計的DRC收斂期間,這些介面可提供顯著的生產力優勢,使客戶能快速優化其手動的DRC修正,以節省更多時間來實現PPA目標。

Mentor的AFS平台被三星Foundry的器件模型和設計套件所支援,雙方的共同客戶能够以此在驗證類比、RF、混合訊號、記憶體和自訂數位電路時,實現比傳統SPICE模擬器速度更快的奈米級SPICE準確度。

Mentor引入Calibre Recon技術簡化IC驗證過程

為了幫助集成電路(IC)設計人員更快地完成電路設計驗證,Mentor近期宣布將其Calibre Recon技術添加至Calibre nmLVS電路驗證平臺。其技術於去年推出,作為Mentor Calibre nmDRC套件的擴展,旨在幫助客戶在早期驗證設計迭代期間快速、自動和準確地分析IC設計中的錯誤,從而縮短設計週期和產品上市時間。

Calibre nmLVS-Recon解決方案幫助系統級晶片(SoC)工程師、電路設計工程師和IC電路驗證團隊在開發階段的早期識別並解决選定的系統接線錯誤,縮短電路驗證的總週期時間。這些錯誤不僅僅會消耗寶貴的計算資源,並可能產生數百萬個錯誤結果,其中許多錯誤只是因為設計狀態未完整而產生。此解決方案的早期採用者在分析前期設計時能够實現10倍以上的運行時間改善,並减少3倍的記憶體需求。

Calibre nmLVS-Recon技術基於靈活的設計架構,支持多種使用模型,使設計團隊能够選擇和分析特定類別的電路驗證問題。該工具採用自動化的智慧執行啟發方法(Intelligent Execution Heuristics),可以幫助用戶在完整的Calibre nmLVS Signoff流程與Calibre Recon選擇的電路驗證檢查之間無縫導航。運用數據分區、設計細分、數據再利用、任務分布和錯誤管理的高級選項,可按原型將Calibre nmLVS-Recon流程與任何晶圓廠/集成電路製造商(IDM)的Calibre sign-off設計套件結合使用,還可應用於任何製程節點。

早期的設計版本中通常包含許多明顯的系統違規行爲。例如電源接線短路(Shorted Net)這樣的違規會造成數百萬個錯誤,並且需要非常密集的計算。電路驗證工程師現在可以使用Calibre nmLVS-Recon短路隔離功能,以互動和迭代的管道快速有效地查找並修復這一類型的版圖布線設計錯誤造成的接線短路問題。此功能選項可實現靈活性和設計分析意圖的變化,同時保持易用性和無縫的使用轉換。

Mentor Analog FastSPICE eXTreme提升驗證效能

Mentor推出奈米級驗證Analog FastSPICE eXTreme技術,可大幅提高模擬效能,並確保奈米級類比驗證所需的晶圓廠認證準確度,該技術使其Analog FastSPICE平台再次取得重大進展。

對於寄生複雜度和接觸電阻高的類比設計來說,Analog FastSPICE eXTreme更具價值。隨著製程尺寸的持續微縮,上述兩種問題正日益嚴重,初期客戶的基準測試顯示,與Mentor上一代的Analog FastSPICE產品相比,該項新技術的模擬效能提高了10倍。

Mentor的Analog FastSPICE平台可為奈米類比、射頻(RF)、混合訊號、記憶體和自訂數位電路提供快速的電路驗證,其已通過晶圓廠5奈米製程認證,同時也是全球許多成功的類比晶片設計重要的平台。

無須額外成本,新的Analog FastSPICE eXTreme技術便可供既有的Analog FastSPICE客戶使用,為大型、布局後類比設計提供更多的效能優勢。此技術具備創新的電阻電容(RC)電路縮減演算法,可為Analog FastSPICE核心SPICE矩陣解算器帶來顯著的效能提升,以及全頻譜的元件雜訊分析功能,可實現矽晶準確模擬。

Analog FastSPICE eXTreme是MentorSymphony混合訊號平台的補充,該平台利用Analog FastSPICE電路模擬器,透過業界標準的HDL模擬器提供快速、準確的混合訊號驗證。Symphony平台具備簡易的使用模式、強大的除錯功能和配置支援,適用於複雜的奈米級混合訊號IC驗證。

Mentor偕三星Foundry 提高產品良率並簡化記憶體測試

Mentor近日宣布與三星Foundry合作開發一款新的參考設計套件,幫助雙方共同客戶簡化在製造過程中對於先進晶片上系統嵌入式記憶體的測試、診斷與修復。

三星Foundry全新的設計解決方案套件(SF-DSK)運用Mentor的Tessent MemoryBIST軟體技術,可幫助客戶簡化可測試性設計流程並提高產品良率。該套件擁有一個用戶友好的介面,將三星的efuse與Tessent MemoryBIST軟體之内建自我修復功能連接起来,藉以提高自動化程度並簡化實施過程。

三星電子設計技術團隊副總裁Sangyun Kim表示,在此之前,客戶必須使用通用的efuse介面範本來開發介面邏輯,他們需要研究三星的efuse操作,然後手動自定義介面,才能運用Tessent MemoryBIST的自我修復功能,例如壓縮修復數據和增量修復等等。現在,客戶可以輕鬆使用Tessent MemoryBIST和三星efuse進行修復,速度大大快於從前。

該套件現包含的Tessent MemoryBIST内建自我修復功能有:高效能壓縮、增量修復(例如在不同溫度環境下進行測試所需的額外修復)、自動通電傳輸功能(可在啟動期間存儲指令並在之後執行)、快速讀取/寫入功能。

Mentor生態系統助安霸AI視覺處理器符合汽車目標

Mentor近期宣布,其 Tessent軟體安全生態系統協助人工智慧視覺晶片公司安霸(Ambarella)成功達成系統內(In-system)測試要求,並該公司的CV22FS和CV2FS汽車攝影機系統單晶片(SoC)實現了ISO26262汽車安全完整性等級(ASIL)目標。

Ambarella VLSI總監Praveen Jaini表示,可測試性設計(DFT)是積體電路(IC)設計的關鍵要素,對於鎖定安全關鍵型汽車應用的先進AI元件來說更是如此。Mentor的Tessent安全生態系統為我們提供了許多強大、省時的功能,不僅協助我們快速實現設計目標,還兼顧了客戶所期望的成本效益和可靠性。由於Mentor的Tessent生態系統具高度擴展性,可為開發創新設計和新一代裝置提供最佳的靈活性。

Tessent Safety生態系統包含多項Mentor IC測試技術,是業界汽車IC測試解決方案的完整組合,並與Mentor的業界領導合作夥伴緊密連結。該生態系統可提供一系列先進的IC測試技術,包括線上(In-line)元件監測,這是一種創新方法,可把嵌入式監視器分布在每個半導體裝置中,並透過共通的基礎架構將其連接在一起,以實現快速偵測並回報系統中任何位置的隨機故障。

Mentor副總裁暨Tessent產品總經理Brady Benware表示,Tessent Safety生態系統透過可擴展的DFT架構,協助我們的客戶因應和克服挑戰,此架構是專為解決自駕車IC設計所面臨的嚴格時間、成本和品質要求所打造。

Mentor加入O-RAN聯盟 滿足5G網路晶片互操作性要求

隨著全球公共5G無線網路建設的繼續,以及對私有5G無線網路關注度的增加,這些網路的部署速度和營運越來越依賴於跨多個供應商的成功互操作性。與此前的5G時代不同的是,現在的5G無線網路必須包含多個規格,每個規格都需要自己的一系列測試。

為了應對這些挑戰,幫助加速全球5G部署,並支援針對5G應用的硬體解決方案設計師,Mentor近日宣布加入O-RAN聯盟,該聯盟由眾多領先的電信服務提供者和生態系統供應商組成,致力於在5G無線接入網(RAN)架構和編排的演進中實現開放性、智慧性、靈活性與高性能。作為聯盟成員之一,Mentor將專注於基於開放標準和高度可配置的網路開發的驗證要求。

Mentor 的IC部門執行副總裁Joe Sawicki表示,構建5G網路產品會面臨諸多挑戰,而測試是取得成功的關鍵。Mentor全面的晶片驗證流程適合O-RAN聯盟及其成員,能夠助其簡化全球5G部署的互操作性驗證週期。

O-RAN聯盟鼓勵多個公司進行合作,支援其製造最佳並具成本效益的5G產品。這些產品的關鍵通常是系統單晶片(SoC),其驗證必須在它們支援的整體5G系統環境中進行。

Mentor的X-STEP矽後驗證平台是支援該項工作的科技之一,此平臺可用於混合供應商5G組件(包括SoC、基帶板和天線系統)的系統級測試。X-STEP是Mentor在2018年收購的芬蘭5G軟體公司Sarokal產品,可與Mentor的VeloceStrato硬體模擬平台相互合作,為5G網路提供獨特的驗證流程,包括矽前和矽後驗證功能。

Mentor IC設計平台通過台積電製程技術認證

Mentor近期宣布,該公司的多項IC設計工具已獲得台積電的N5和N6製程技術認證。此外,Mentor與台積電的合作關係已擴展到先進封裝技術,可進一步利用Mentor Calibre平台的3DSTACK封裝技術來支援台積電的先進封裝平台。

台積電的N5和N6製程技術可協助許多全球領先的IC設計公司提高處理器效能、縮小尺寸並降低功耗,以應對汽車、物聯網、高效能運算、5G行動/基礎設施、人工智慧等領域激烈的市場競爭。

Mentor的IC部門執行副總裁Joe Sawicki表示,Mentor與台積電長期合作並且擁有豐碩的成果,如此緊密的夥伴關係將持續協助共同客戶開發出高度創新和差異化的IC。很高興Mentor設計平台能夠獲得台積電最新的半導體製程技術認證,雙方的夥伴關係得到了更進一步擴展。

最近通過台積電N5和N6製程認證的Mentor IC設計技術包括Calibre nmPlatform,它是IC實體驗證領域的工具。Calibre可為全球成功的晶片製造商和IC設計人員提供出色的效能、準確度和可靠性驗證方案;Calibre xACT抽取工具─Calibre nmPlatform中的組成元件,可提供強大的寄生參數抽取功能和高準確度的數據,以供布局後分析和模擬之用;Mentor的Analog FastSPICE(AFS)平台─可為奈米類比、射頻(RF)、混合訊號、記憶體和客制化數位電路提供先進的電路驗證。

除了獲得這些認證,Mentor亦宣布,其AFS平台現在可支援台積電的行動裝置和高效能運算(HPC)設計平台。此認證可協助為HPC應用提供類比、混合訊號和射頻(RF)設計的Mentor客戶,使用台積電的最新製程技術充滿信心地進行晶片驗證。Mentor還同時宣布將與台積電合作,進一步利用Calibre的3DSTACK封裝工具來支援台積電的CoWoS封裝技術。該技術採用矽中介層作為晶粒間端口連接檢查的解決方案,Calibre xACT可用來提供寄生參數抽取。

台積電設計建構行銷事業處資深處長Suk Lee表示,作爲台積電重要的合作夥伴,Mentor持續提供豐富多樣的設計工具和平台,以支援台積電最先進的製程技術。期待與Mentor繼續共同努力,透過電子設計自動化 (EDA) 工具協助雙方的共同客戶運用5奈米製程這樣的TSMC領先技術提升晶片功率和效能,運用先進的EDA工具成功實現晶片設計。