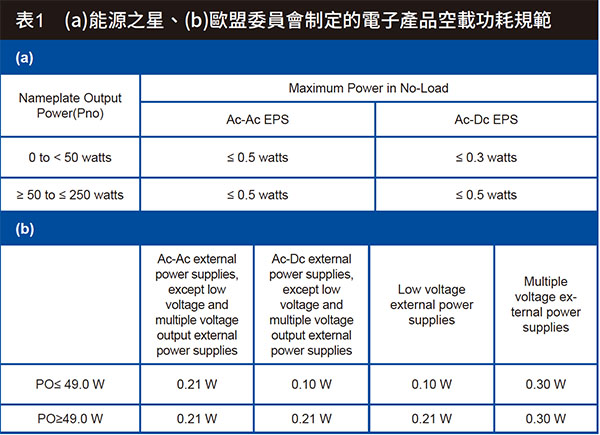

隨著全球暖化日益嚴重與節能減碳呼聲高漲之際,人們也從開發新能源以及提高能源使用效率方面來著手因應,相關之節能法規也應運而生,例如能源之星認證項目、歐盟節能化設計指令,制定各式產品能源效率標準,表1為歐盟委員會所制定在不同輸出功率與方式之空載功率損耗規範。電子設備製造商發展的節能產品,必須遵循國際認證標準,促使電子產品朝向更節能的方向發展,如此也是提高能源利用效率的有效途徑。

對於電子產品電源設計的要求,除了滿足符合各個額定負載效率標準之外,空載與待機功耗也顯得益發重要,因為許多的用電設備大部分時間都工作在極輕載或待機狀態,例如:電視、個人電腦及螢幕等應用,若是每一個電子裝置的待機功率可以省下0.1~0.5W,這些閒置裝置就可以省下相當於數十個發電廠的每年發電量。

本文將探討如何降低切換式電源(Switching Mode Power Supply)的待機功耗,最後並舉一實際設計案例解說。

如何降低待機功耗

所謂待機功耗是指電子裝置在關閉時或處於待機模式時消耗的電能,或是處於最低功率模式下所使用的功率。一般電子裝置的輔助電源最常用的是返馳式拓樸架構,如何降低電子裝置的待機功耗,最有效的方式就是減少其在待機時的導通與切換損失。

在導通損失方面:

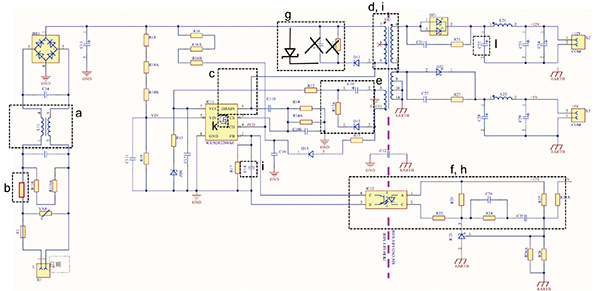

1.適當設計輸入端的共模電感的線徑與匝數,在抑制共模雜訊時,可以同時兼顧到將共模電感的導通損失降到最低。

2.選擇適當熱敏電阻的阻值,以避免其內阻的導通損耗。

3.於設計規格中的啟動時間之內,選擇合適的啟動電阻值,或者是選用內建啟動單元的IC。

4.有些控制器雖然在待機時降低切換頻率,來減少切換損耗,但是變壓器線組的導通損耗仍然不可忽視,線圈的圈數與線徑之適當選擇,對於線圈的線阻損失可以有效降低。

5.一次側Vcc輔助繞組的圈數與線路,適當地設計於各種負載條件之下,除了提供穩定正常工作的Vcc,並且能夠將Vcc輔助繞組線路的導通損耗降至最低,若是Vcc不足時,IC會進入反覆啟動狀態,頻繁的需要高壓給Vcc電容充電,造成啟動電路損耗。

6.其次,二次側回授控制線路TL431周遭的電阻,適當地設計在使整個控制線路正常工作之下,將偏壓與分壓線路的電流損失降低,並且選擇高CTR的光耦合器。

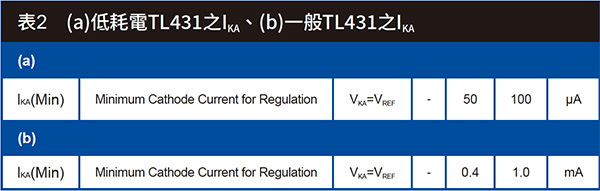

7.選擇低耗電TL431其typical IKA為50uA如表2(a)所示,與一般TL431其typical IAK為0.4mA如表2(b)所示,兩者的耗電就差了8倍,藉由使用低耗電之TL431,將圖1之R23電阻放大可以減少二次側TL431損耗。

8.在切換損失方面,RCD在緩衝(Snubber)電路中,可以使用齊納二極體來取代RC。

8.在切換損失方面,RCD在緩衝(Snubber)電路中,可以使用齊納二極體來取代RC。

9.變壓器的層間雜散電容會造成額外的切換損失,可以在層與層之間加絕緣膠帶來降低層間的電容效應。

10.減少一次側回授訊號腳位的並聯電容值。

11.選擇使用雜散電容與Qg較小的MOSFET。

12.加大輸出電容以增加維持時間,拉大叢發模式(Burst Mode)的週期時間,以減少叢發的切換次數,以上所建議的方法總結於圖1所示。

除了外部零件值的調整之外,在控制器本身方面,對於降低輕載功耗,常見的方法為降低切換頻率、關斷時間調制(Off Time Modulation),以及叢發模式。另外,盡量選擇靜態電流較小的IC,因為這對於大多數時間處於休眠模式或低功耗模式的應用尤其重要。

電源設計範例解說

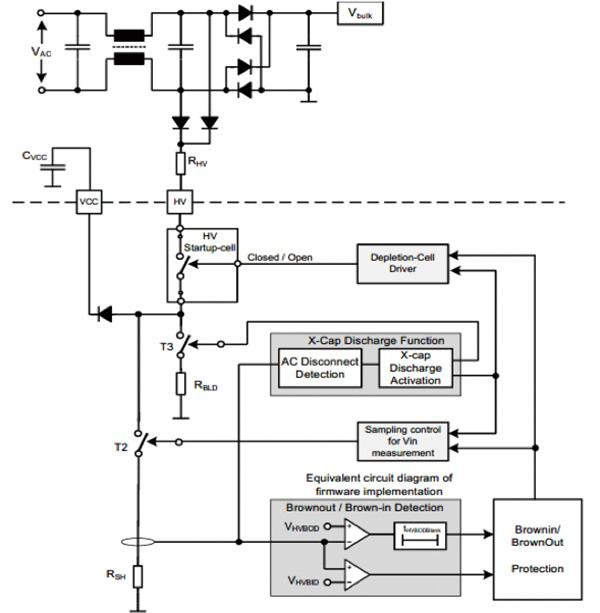

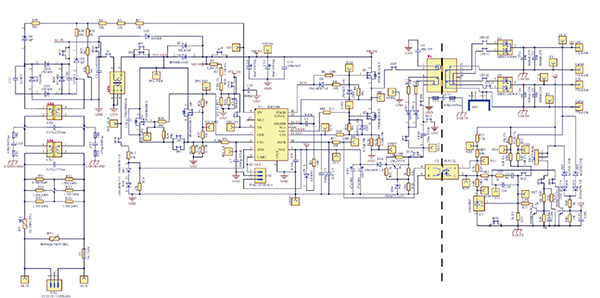

本文以一個120W電視電源演示板為設計範例解說,電路板之主要控制IC為IDP2308,此IC為一結合PFC與LLC的整合式數位控制器,具有內建的啟動單元 (600V Start Up Cell),當Vcc電壓建立到一定的準位後,此一啟動單元會關斷啟動迴路,避免啟動電阻的導通損耗,此外,啟動單元迴路兼具X-cap放電功能,以省掉外接型IC的功率損耗,如圖2所示。

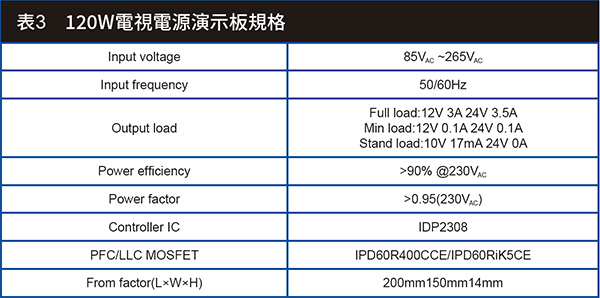

另外,在輕或空載時,控制器會進入叢發模式,以降低切換損失,由於IDP2308是數位IC,具有提供使用者彈性設計的便利性,使用者可以經由參數的調整來優化整體電路的行為,達到所需要符合的規範,演示板線路如圖3所示;演示板規格如下表3所示:

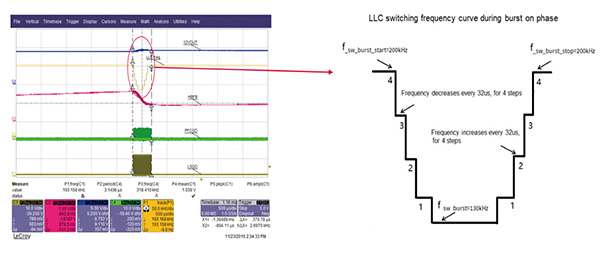

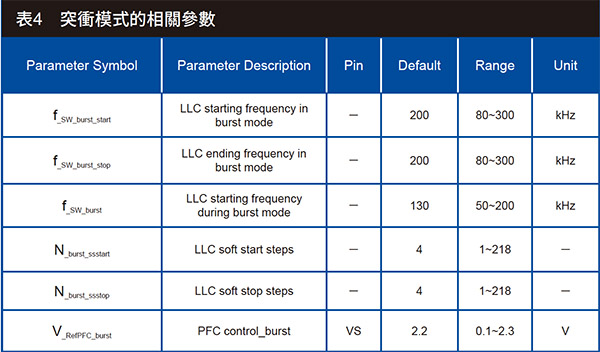

如圖4所示,以下詳細解說IDP2308在叢發模式時的動作行為,當進入待機模式時,主要監控HBFB腳位的電壓準位,來決定叢發模式的運作,當HBFB的電壓上升至Vburst_on,IC會被喚醒而啟動叢發的切換,在LLC完成一個完整的叢發切換,IC就會停止切換然後進入睡眠模式以節省功率損耗。影響待機功耗的主要參數列於表4,其中有叢發模式中的啟動頻率、切換頻率、結束頻率、PFC Bulk電壓以及軟啟動與軟結束的階數多寡。

使用者可以自行調整在LLC之叢發模式中的三個部份:

1.設定較高的啟動切換頻率,預設值為200KHz,軟啟動設定為4階,每32us降一階,目的是減少每一叢發模式控制的啟動突衝電流,降低功率損耗,同時可以抑制異音雜訊。

2.其次設定一較低的切換頻率,預設值為130KHz,以達到最低待機功率與維持二次側輸出電壓的穩定。

3.最後再採用較高的結束切換頻率,預設值為200KHz,軟結束設定為4階,每32us升一階,用於達到抑制異音雜訊。在PFC方面,可以經由參數設定降低PFC bulk的工作電壓準位,來減少切換損耗。

除了參數的設定之外,外部零件值的調整,例如:LLC變壓器的主感Lp、LLC Bootstrap電容及諧振電容的材料,也會對異音與待機功耗有所影響。

經由以上的參數設定與外部零件調整,可以降低叢發模式時LLC的諧振電流,如圖5所示,最後的實驗結果,除了能夠符合小於0.3W待機功耗規範,並且達到極低異音的要求標準,以及維持系統輸出電壓穩定的設計目標。

數位控制器提高操作效率

本文介紹了電子設備電源的待機功耗及其規範,詳細剖析建議的解決設計方案,並且探討實際設計案例,除了一般使用者常用的對策,例如外部零件的調整與選用等方式之外,藉由數位控制器的參數設定調整也是解決之道之一。

一個好的電源設計,除了提供基本電子設備正常的運作之外,也可以減少系統的功率損耗,提高整體操作效率,另外,透過採用合適的數位控制器來做設計,進而減少外部元件的使用數量,節省整體系統的物料成本。

(本文作者為台灣英飛凌科技首席工程師)