MOSFET

電源供應市場帶頭衝 GaN功率IC商機超展開

氮化鎵(GaN)功率半導體可望大發利市。5G、AIoT時代來臨,許多創新技術應用如自駕車、電動車、無線充電、擴增實境(AR)、工業智動化、無人機,甚至5G基地台,對於能源效率的要求將顯著增加。可較現今矽(Si)功率元件實現更高轉換效率的GaN技術,遂成為各界關注焦點,並吸引許多半導體業者爭相投入布局。

根據市場研究機構Yole Développement指出,與矽功率半導體328億美元的產值相比,GaN功率市場規模仍相當小,但該技術已開始滲透至各種應用領域,其中,又以電源供應為主要應用,如手機的快速充電器。

據了解,Anker可以說是目前市場上導入GaN功率技術最積極的行動週邊裝置製造商,其行動充電器PowerPort Atom PD第一代至第三代,以及PowerPort系列部分產品,和另一個PowerCore Fusion產品,都已開始導入GaN技術。另外,Aukey、RavPower、Mu One等廠商也有採用。

行動週邊裝置品牌廠Anker自2018下半年起,已開始導入GaN功率元件,打造兼具輕巧、高功率密度的充電器。(圖片來源:Anker)

除了行動充電器外,自駕車光達(LiDAR)、資料中心伺服器、電動車,以及無線充電,亦是GaN功率半導體極具成長性的應用。Yole認為,GaN功率半導體能帶來更高的節能效益,因此相關技術研發能量不斷增加,商用產品也開始問世,整體GaN功率元件市場規模自2016年起已逐步放量;若情況樂觀,預估2017~2023年的複合成長率(CAGR)可高達93%,達到4.23億美元規模。

Yole Développement預估,在最佳狀況下,2017~2023年GaN功率半導體市場將可達到93%的年複合成長率。(資料來源:Yole Développement)

大廠加入量產行列 GaN發展更入佳境

2018年6月,功率半導體大廠英飛凌(Infineon)正式宣布於年底開始量產CoolGaN 400 V及600 V e-mode高電子遷移率電晶體(HEMT),為GaN功率技術的發展打了一劑強心針。

Yole技術與市場分析師Ezgi Dogmus認為,這家電源解決方案的領導廠商開始量產GaN的宣布,對GaN功率元件市場來說是一個重要的象徵。目前英飛凌已經擁有許多客戶在使用他們的矽解決方案,而未來這些客戶都有機會能轉移到GaN技術。

英飛凌高電壓轉換部門資深協理Steffen Metzger表示,GaN市場已經獲得強大動能,在特定應用中採用此項技術帶來大幅優勢。從降低營運支出及資本支出,提升功率密度實現更精巧輕盈的設計,乃至於減少整體系統成本,產生的效益相當具有說服力。英飛凌深信,GaN是電源管理的下一個明日之星。該公司已經做好所有準備,以達成在GaN電源方面成為客戶首選的目標。

就在英飛凌發布GaN量產消息後沒多久,意法半導體(ST)也宣布要由原本碳化矽(SiC)的發展,擴大延伸到GaN技術領域,將和法國技術研究機構CEA-Leti合作研發GaN-on-si技術,利用Leti的8吋研發產線進行二極體和電晶體開發。雙方預期在2019年完成驗證工程樣品。同時,意法半導體也預計2020年將在該公司位於法國圖爾市的前段晶圓廠中,建造完全符合規範的生產線(包含GaN-on-Si異質磊晶製程),以做為初期生產之用。

除了整合元件製造商(IDM)發展力道愈來愈強,這些年來聚焦GaN功率元件開發的新創公司也不斷冒出,前面提及的EPC、Transphorm、GaN Systems是相對較早成立的,其他還有Tagore、Exagan、Navitas、VisIC、Dialog Semiconductor、GaNPower International、NEXGEN Power Systems等。

這些新創大都是無晶圓廠(Fabless)的公司,選擇以委外給晶圓廠生產的商業模式,多半使用台積電、漢磊(Episil)或X-Fab做為他們主要選擇。未來,一旦市場規模擴大,晶圓代工的商業模式將讓這些無晶圓廠新創公司有望快速成長茁壯。

顯而易見,現今的GaN功率元件市場可說是老將新秀同台較勁、競相逐鹿,使得整體市場戰火正快速升溫,為了端出更具競爭力的產品方案,許多廠商已積極投入整合型方案研發。

目前市場上的整合型GaN功率元件可概分為兩種,一種是封裝層級的整合,將GaN電晶體與驅動器整合成單一封裝,多半針對650V以上的應用;另一種是在裸晶層級上整合GaN電晶體與驅動器,也就是達到所謂的單體式整合(Monolithically Integrated),此類產品供應商以EPC和Navitas為代表,多半針對600V以下的消費性應用。

由於消費性應用如行動裝置充電器,需求規模龐大,對GaN業者而言,是滋養茁壯的重要養分,因此為了迎合市場輕巧外觀的設計要求,走向高整合設計方案將勢在必行。

imec製程技術助攻 GaN加速實現單體整合

有鑑於市場對更高整合度GaN功率元件的發展需求,奈米電子和數位科技研究與創新中心imec,利用其GaN-on-SOI和GaN-on-QST技術平台,發布一款與驅動器單體整合且功能完整的GaN半橋IC。

半橋是一種在電力系統中常見的次電路,是由離散元件所組成,特別是用在較高電壓範圍的應用。要利用GaN-on-Si技術在晶片上實現半橋電路,極具挑戰,特別是高電壓的設計,這是因為基於GaN-on-Si技術所設計的半橋電路,會產生「後閘效應(Back-gating Effect)」,進而對半橋電路的高側端開關(High-side Switch)造成負面影響,而切換雜訊也會對控制電路造成干擾,抑制整體效能表現。

imec解決方案是建立在imec的GaN-on-SOI和GaN-on-QST技術平台,透過埋入式氧化物(Buried Oxide)和氧化物填充的深溝槽隔離設計,讓功率元件、驅動器和控制邏輯能夠達到電氣隔離。這種隔離機制能減少有害的後閘效應對半橋高側端開關的負面影響,更能減少切換雜訊對控制電路的干擾。

此外,imec的技術平台也藉由整合電位轉換器(Level Shifter)(用來驅動高側開關)、停滯時間控制器(Dead-time...

ROHM開發車電超小型MOSFET RV4xxx系列

半導體製造商ROHM研發出1.6mm×1.6mm尺寸超小型MOSFET「RV4xxx 系列」,該系列產品可確保零件安裝後的可靠性,且符合車電產品可靠性標準 AEC-Q101,是確保車規級品質的高可靠性產品。此外,該系列採用了ROHM 獨創的封裝加工技術,非常有助於先進駕駛輔助系統(ADAS)相機模組等高品質車電元件的小型化。

近年來,在ADAS領域中所不可或缺的車電相機,因受到安裝空間的限制,對所配置零件的小型化要求越來越高。為滿足這些市場需求,在保持大電流的前提下,可進一步實現小型化的底部電極封裝MOSFET 因而備受矚目。

另一方面,為確保車電產品的可靠性,會在產品安裝後進行外觀檢測,但由於底部電極封裝在側面沒有充分形成穩定的焊接面,因此無法確保車電元件所需要的焊料高度,也很難確認安裝後的焊接狀態,這種情形已是長久以來存在的問題。

ROHM 一直領先業界致力於超小型MOSFET的產品研發,並創造了許多傲人佳績。本次透過ROHM獨創製程的Wettable Flank成型技術,在底面電極封裝也能形成焊接面,實現了業界首創保證封裝側面電極部分具 130μm 高度,因此可在產品安裝後的外觀檢測中充分確認焊接狀態。

利用ROHM獨創製程的Wettable Flank 成型技術,保證封裝側面電極部分具130μm 高度,Wettable Flank 成型技術是在封裝側面的引線框架部加入切割再進行電鍍的技術。然而,引線框架切割高度越高越容易產生毛邊。

為此ROHM 研發出獨創製程,在引線框架整個表面上設定了用來減少毛邊的障壁層,可以防止產品安裝時出現傾斜和焊接不良,在DFN1616 封裝產品(1.6mm×1.6mm)中,成為業界首家可保證封裝側面電極部分具有130μm 高度。

傳統ADAS 相機模組的反接保護電路主要採用蕭特基二極體(SBD)。但是,隨著相機解析度日益提高,在邁向超大電流化方向發展的車電市場,由於小型底部電極MOSFET 具有導通電阻低且可減少發熱量的特點,取代SBD 已經是大勢所趨。

例如電流2.0A、功耗0.6W 時,在車電市場被廣為使用的帶引線封裝MOSFET,與SBD 相比可減少30%的安裝面積。而底部電極封裝的MOSFET,由於散熱性更佳,不僅可實現小型化,還可實現大電流化,因此與傳統的SBD 相比,安裝面積可減少78%,與普通的MOSFET 相比,安裝面積可減少68%。

儒卓力提供英飛凌OptiMOS功率MOSFET

英飛凌的OptiMOS 3和5是同類最佳(BiC)的功率MOSFET,採用節省空間的SuperSO8封裝,與先前型號相比,具有更高的功率密度和穩健性,讓系統成本得以降低,而整體性能也得以提升。客戶可以到儒卓力電子商務平台www.rutronik24.com瞭解有關OptiMOS BiC功率MOSFET的產品資訊。

由於具有最低的導通電阻(RDS(on)),這些BiC MOSFET能夠以良好的性價比降低損耗。此外,接面至外殼(Junction to Case (RthJC))之間的低熱阻抗提供了出色的散熱行為,從而降低了滿載運作時的溫度。它提供顯著降低的電壓過衝,讓低反向恢復電荷(Qrr)可以提高系統可靠性,最大限度地減少了對緩衝電路的需求,因此工程成本得以降低,工作量也得以減少。

這些BiC MOSFET器件的額定溫度為175°,有助於在更高工作接面溫度下實現更高的功率,或者在相同的工作接面溫度下具有更長使用壽命的設計。此外,隨著額定溫度的增加,安全操作區域(SAO)亦改善了20%。

這些BiC MOSFET具有出色的性能數據,非常適合電信、伺服器、三相逆變器、低壓驅動器以及D類音訊等應用。英飛凌OptiMOS BiC功率MOSFET產品系列包括60V~250V等版本。

選用本體二極體 LLC拓撲反向恢復快又穩

LLC諧振轉換器就是一種軟開關拓撲,讓主功率開關管零電壓切換,顯著降低切換器之損耗,大幅提升電源效能。在這種拓撲中,為了達到ZVS狀態,功率切換器的寄生二極體必須反向恢復時間非常短。如果本體二極體不能恢復全部載流子,則在負載從低到高的變化過程中,可能會發生硬開關操作,並可能導致寄生雙極電晶體導通。

減少元件數量/尺寸功率滿足密度需求

在電信設備電源、大型電腦/伺服器、電焊機、鋼材切割機等消費性應用市場上,對功率密度的需求每年都在成長。要想提升功率密度,就必須減少元件數量,降低功率損耗,縮減散熱器和被動元件的尺寸。目前,硬開關半橋是這些應用的典型拓撲,而LLC諧振半橋則是新興的替代方案。LLC拓撲能確保導通前切換器的電壓為零(或者關斷期間切換器電流為零),進而消除每次切換時因電流和電壓交疊而導致的功率損耗。

在高頻應用中採用這種切換技術同樣可以降低切換器的損耗,進而有助於縮減被動元件的尺寸。顯而易見,切換功率損耗降低為在應用設計中選用尺寸更小的散熱器提供了可能。零電壓條件發生是MOSFET寄生二極體導通所致。在負載快速變化過程中,MOSFET從零電壓切換至零電流切換器,在這種情況下,高dv/dt值可使寄生雙極電晶體導通並燒毀MOSFET。

LLC拓撲簡介

LLC拓撲的基本半橋電路是由兩個切散器所組成,高邊切換器(Q1)和低邊切換器(Q2)透過電感Lr和電容Cr與變壓器相連(圖1)。切換器與寄生二極體(D1和D2)和寄生輸出電容(C1和C2)並聯,為了闡述其在全域功能中的作用,我們在圖中將它們單獨標註出來。在圖1中,我們注意到多出一個Lm電感,實際上,Lm是變壓器漏電感,其規則在LLC拓撲中非常重要。

圖1 LLC半橋電路

如果變壓器原邊電感Lm值很大,不會影響諧振網路,則圖1所示的轉換器就是一個串聯諧振轉換器。

在一個諧振單元中,當輸入訊號頻率(fi)等於諧振頻率(fr)時,即當LC阻抗為零時,增益最大。諧振轉換器工作頻率範圍是由兩個特定的諧振頻率值界定,這些頻率值與電路有關。驅動控制器設定MOSFET的開關頻率(fs)等於電路諧振頻率,以保證諧振的重要優勢。

現在我們將看到,如何透過改變負載,使諧振頻率從最小值(fr2)變為最大值(fr1):

當時,LLC就像一個串聯的RC諧振腔;這種功能出現在高負載條件下,即當Lm與低阻抗並聯時;當時,LLC類似於並聯RC諧振腔,這功能出現在低負載條件下。系統通常不在這個區域工作,因可在ZCS條件下運行。若頻率fi在fr2<fi<fr1範圍內,則兩個功能同時存在。

如果使用圖形表示諧振元件的增益,我們就得到圖2所呈現的曲線,不難看出,圖形變化與Q值相關。

圖2 諧振頻率的變化與Q值有關

LLC諧振轉換器的工作範圍受限於峰值增益。值得注意的是,峰值電壓增益既不發生在fr1處,也不出現在fr2處。峰值增益對應的峰值增益頻率是fr2與fr1之間的最大頻率。隨著Q值減小(隨著負載減小),峰值增益頻率移向fr2,並且獲得更高的峰值增益。隨著Q值增加(負載增加),峰值增益頻率移向fr1,峰值增益下降。因此,滿載應該是諧振網路設計的最差工作條件。

從MOSFET角度看,如先前所述,MOSFET的軟開關是包括LLC在內的諧振轉換器的重要優點,而對於整個系統,由於輸出電流是正弦波,因此, EMI干擾降低。圖3所示是LLC轉換器的典型波形特性。

圖3 LLC轉換器的典型波形

在圖3中我們注意到,漏極電流Ids1在變正前是在負電流區擺動。負電流值表示本體二極體導通。在此階段,由於二極體上的壓降,MOSFET漏源兩極的電壓非常小。如果MOSFET在本體二極體導通期間切換,則發生ZVS切換,切換損耗降低。該特性可以縮減散熱器尺寸,提高系統效能。

如果MOSFET切換頻率fs小於fr1,功率元件上的電流形狀會改變。事實上,如果持續時間足以在輸出二極體上產生不連續的電流,則原邊電流形狀會偏離正弦波形。

此外,如果MOSFET的寄生輸出電容C1和C2與Cr的容值相當,則諧振頻率fr也會受到元件的影響。正是因為這個原因,在設計過程中,選擇Cr值大於C1和C2,可以解決這個問題,使fr值不受所用元件影響。

續流與ZVS息息相關

分析諧振頻率的方程式就會發現,在高於峰值增益頻率時,諧振網路的輸入阻抗是感抗,諧振網路的輸入電流(Ip)滯後於諧振網路的輸入電壓(Vd)。在低於峰值增益頻率時,諧振網路的輸入阻抗變為容抗,並且Ip領先Vd。在電容區運作時,本體二極體在MOSFET切換期間執行反向恢復操作。

當系統在電容區工作時,MOSFET會面臨極大的潛在失效風險;事實上,如圖4中的圓圈所示,寄生二極體的反向恢復時間變得非常重要。

圖4 避免潛在失效,寄生二極體的反向恢復時間相當重要。

根據這一點,在負載由低變高的過程中,驅動電路應強制MOSFET進入ZVS和正關斷電流區。如果無法保證,MOSFET的工作區可能很危險。

在低負載穩態條件下,系統工作在頻率較低的諧振頻率fr2附近,然後ZVS導通,並保證正關斷漏極電流。在負載變化(從低到高)後,接換頻率應該變成新的諧振頻率。如果沒有發生這種情況,則系統狀態經過ZCS區域和ZVS導通,正關斷漏極電流不會出現。因此,當MOSFET關斷時,電流也會流過寄生體二極體。因此,寄生體二極體的性能變得非常重要。出於這個原因,新LLC設計的趨勢是使用本體二極體恢復時間非常短的功率元件。

(本文作者任職於意法半導體)

採用額外肖特基二極體 有效減少電壓干擾

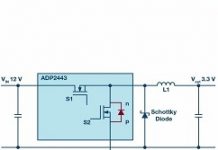

在負載點(POL)降壓轉換器領域,同步變化的高側和低側主動開關已被廣泛使用。圖1顯示了具有理想切換開關的此類電路。與使用被動肖特基二極體作為低側開關的架構相比,此類切換開關穩壓器具有多項優勢。主要優勢是電壓轉換效率更高,因為相較於採用被動二極體的情況,低側開關承載電流時的壓降更低。

圖1 用於降壓轉換、採用理想開關的同步開關穩壓器。

確保同步降壓轉換器安全 兩開關時間內須保持斷開

但是,與非同步開關穩壓器相比,同步降壓轉換器會產生更大的干擾。如果圖1中的兩個理想開關同時導通,即使時間很短,也會發生從輸入電壓對地的短路。這會損壞切換開關,因此,必須確保兩個開關永遠不會同時導通。因此,出於安全考慮,須要在一定時間內保持兩個開關都斷開。

這個時間稱為開關穩壓器的死區時間。但是,從開關節點到輸出電壓連接了一個載流電感(L1)。通過電感的電流永遠不會發生瞬間變化。電流會連續增加和減少,但它永遠不會跳變。因此,在死區時間內會產生問題。所有電流路徑在開關節點側中斷。採用圖1所示的理想開關,在死區時間內會在開關節點處產生負無窮大的電壓。在實際開關中,電壓負值將變得越來越大,直到兩個開關中的一個被擊穿並允許電流通過。

使用MOSFET作為主動開關 有效控制節點電壓

大多數切換開關穩壓器使用N通道MOSFET作為主動開關。這些開關針對上述情況具有非常有優勢的特性。除了具有本身的開關功能外,MOSFET還具有所謂的體二極體。半導體的源極和漏極之間存在一個P-N結。在圖2中,插入了具有相應P-N結的MOSFET。由此,即使在死區時間內,開關節點的電壓也不會下降到負無窮大,而是通過低側MOSFET中的P-N結(如紅色所示)承載電流,直到死區時間結束並且低側MOSFET導通為止。

圖2 用於降壓轉換的同步開關穩壓器,採用 N通道 MOSFET和額外的肖特基二極體,可最大限度地減少干擾。

相應MOSFET中的體二極體有一個主要缺點。由於反向恢復現象,其開關速度非常低。在反向恢復時間內,電感(L1)導致開關節點處的電壓下降到比地電壓低幾伏。開關節點處這些陡峭的負電壓峰值會導致干擾,此干擾會被容性耦合到其他電路段。透過插入額外的肖特基二極體可以最大限度地減少這種干擾,如圖2所示。與低側MOSFET中的體二極體不同,它不會產生反向恢復時間,並且在死區時間開始時能非常快速地吸收電流。這可減緩開關節點處的電壓陡降。可減少由於耦合效應而產生並分佈到電路上的干擾。

肖特基二極體可以設計得非常精小,因為它僅在死區時間內短時間承載電流。因此,其溫升不會過高,可以放置在小尺寸、低成本的產品外殼中

(本文作者為ADI歐洲分公司電源管理技術專家)

PI公布整合有900 V MOSFET的全系列切換開關IC

Power Integrations(PI)宣佈推出整合了900 V一次側MOSFET的離線式切換開關IC系列。最新推出的裝置包括適用於高效率、隔離返馳式電源供應器和簡易非隔離降壓式轉換器的IC。應用包括高達480 VAC的三相工業電源供應器和高品質消費性產品,這些要在主電源電網不穩定的區域、頻繁發生雷擊的熱帶區域或高能量振盪波和突波非常普遍的任何區域使用。

新產品包括適用於簡易非隔離降壓式轉換器的LinkSwitch-TN2 IC 900 V版本和旗艦InnoSwitch3-EP IC系列的三個新成員,這些支援高達35 W的極高效率隔離返馳式。900 V產品系列的所有成員均配備最佳化的內部控制引擎,在整個負載範圍內都具有高效率,使設計輕鬆符合能源相關產品(ErP)限制和各種線電壓和負載保護機制,以進一步提高系統穩定性和可靠性。

900 V LinkSwitch-TN2 IC為降壓式轉換器提供所需元件最少的切換開關解決方案。裝置具備可選限電流和完全整合式自動重新啟動功能,可提供短路和開迴路保護。使用頻率抖動功能可將電磁干擾(EMI)降至最低,並且裝置可輕鬆滿足PCB和封裝上的汲極與所有其他接腳之間的高壓安規距離和間隔要求。

900 V InnoSwitch3-EP返馳式切換開關IC提供無功損線電壓OVP感應,當線電壓超過所選的臨界值時自動中斷切換,可在發生嚴重線電壓過壓的情況下,防止對電源供應器造成損壞。在線電壓和負載條件內,裝置能夠提供高達90%的行業領先的效率,可減少電源供應器損失,實現擁有最高35 W功率但無需散熱器的小尺寸電源供應器。900 V InnoSwitch3-EP IC採用Power Integrations創新的隔離式數位通訊技術FluxLink,加上同步整流(SR)、QR切換和精確的二次側回授感測及控制電路。如此可在不需要不可靠光耦合器的情況下打造出高效率、精準、可靠的電源供應器電路。

資深產品行銷經理Silvestro Fimiani表示,這些切換式功率IC讓三相電表、馬達、工業備用電源供應器、家電,甚至手機充電器的設計人員能夠實現真正的一體式電源供應器,從而滿足任何地方的使用者的可靠性預期。例如,為解決印度高品質消費性產品迅速發展的市場而產生的OEM面臨著源源不斷的電子損坏和退貨產品,必須予以維修或更換。900 V切換開關IC提供有效且低成本的防護,並且運作和產品支援成本大幅減少。

推升大功率電源轉換器能效 新GaN功率開關鋒芒畢露

能源的議題是一直以來被討論的話題,在現今節能減碳的需求下,提高轉換效率是新電源轉換器努力的方向。以往所使用的矽功率開關元件;在以矽為材料所開發的金屬氧化物半導體場效應電晶體(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET),其發展已接近物理極限,期待以矽材料的功率晶體來進行電源轉換器的效率改善效果有限,而寬能隙材料所開發的新型功率晶體,如氮化鎵(GaN)高速電子遷移率場效電晶體(High Electron Mobility Transistor, HEMT)可以讓電源轉換器達到更高的效率及更高功率密度。

對矽功率開關元件而言,設計人員對其應用和驅動已經相當熟悉,但對於GaN HEMT的應用和驅動方式的資訊相對比較少,本文針對GaN HEMT的應用和驅動方式作介紹,提供設計人員在使用GaN HEMT上的參考。

氮化鎵功率元件應用要點

如圖1所示,粗略將幾種材料如矽、碳化矽及氮化鎵等功率開關的適用範圍依功率及切換頻率進行劃分,矽功率開關涵蓋目前大部分的應用,適用於切換頻率在500kHz以下的中小功率應用或低頻的大功率應用;大功率的應用且操作於略高的切換頻率的電源轉換系統會選擇SiC MOSFET;而中低功率需要更高切換頻率如200kHz以上,GaN HEMT會是合適的功率開關元件,目前適合GaN HEMT的應用條件在10kW以下,高於250kHz以上的切換頻率,但實際應用還是以設計者的需求為主,可以選擇GaN HEMT取代MOSFET以相同的切換頻率達到較高的效率,或增加切換頻率來達到較高的功率密度需求。

圖1 不同材料功率晶體開關的應用範圍

目前GaN HEMT的應用領域在電信和資料中心使用的伺服器電源是主要目標市場,採用超高效率電源可以降低能源成本而產生回報。於伺服器電源的電路中,目前發展相對成熟的電路之一為無橋式PFC,採用無橋式PFC可以改善傳統升壓型PFC的效率,現在更可以透過GaN HEMT的特性搭配圖騰柱(Totem Pole)PFC電路來進一步提升效率。

一般電源轉換器的功率因數校正(PFC)線路採用升壓型轉換器架構,如圖2所示。輸入電壓範圍從AC 85V~265V,超過三倍的電壓變化,因此電流也是超過三倍的變化,在相同負載條件下,導通損失有十倍的差異,在這麼大的變化下,要最佳化MOSFET和Diode是一個挑戰。操作頻率一般是低於70kHz,使得兩倍頻限制在低於150kHz,因為頻率的增加會增加切換損失且主頻會落入EMI的測試範圍內,控制模式採用連續傳導模式(CCM)可以減少漣波電流、導通損耗和切換損耗。操作在不連續導通模式(DCM)或是邊界模式(CRM)會有較高的漣波電流,但可以達到ZCS導通,因此可以降低切換損失,無論採用哪一種控制模式,橋式整流器占了一定比例的損耗,約占全機1~2%的效率損失,即使PFC開關採用理想的零切換損耗技術也無法彌補橋式整流器的損耗。

圖2 標準升壓型轉換器架構

PFC電路開關降低損耗

將PFC電路中進行功率損耗分析如圖3所示,可以明顯發現橋式整流器所占的功率損耗最大,其中在輸入電壓為85Vac時占總功率損耗的34%,而在輸入電壓為230Vac時占總功率損耗的37%。正因如此,許多無橋式線路被採用在電源轉換器上來改善效率,但整體線路卻變得複雜許多。另一種降低橋式整流器損耗的選擇是採用主動式橋式整流器(Active Bridge),將較低導通電阻RDS(on)的MOSFET並聯在原有的橋式二極體上,利用Irsm2 X RDS(on)降低原本的Iavg X Vf損耗,保留原本的橋式整流器是需要其協助旁路衝擊電流,避免在異常操作時損壞並聯在橋式整流器上的MOSFET。

圖3 升壓型PFC功率損耗分析

在眾多無橋式PFC的電路架構中,Totem...

ROHM推出內建1700V SiC MOSFET AC/DC轉換IC

半導體製造商ROHM針對大功率通用變流器、AC伺服器、工業用空調、街燈等工控裝置,研發出內建1700V耐壓SiC MOSFET的AC/DC轉換器ICBM2SCQ12xT-LBZ。

BM2SCQ12xT-LBZ是世界首款內建高度節能性的SiC MOSFET AC/DC轉換IC,克服了離散式結構所帶來的設計課題,因此可輕易地研發出節能型AC/DC轉換器。透過專為工控裝置輔助電源設計的最佳化控制電路和SiC MOSFET一體化封裝,使得新產品與普通產品相比具有諸多優勢,像是大幅減少零件數量(將12種產品和散熱板縮減為1個產品),降低零件故障風險,縮短導入SiC MOSFET的開發週期等,一舉解決了諸多課題。與ROHM傳統產品相比,功率轉換效率提高達5%(相當於功率損耗減少28%)。因此,本產品非常有助於工控裝置的小型化和節能化,有效提升可靠性。

近年來隨著節能意識的提高,在交流400V工控裝置領域,與現有的Si功率半導體相比,可支援更高電壓、更節能、更小型化的SiC功率半導體的應用越來越廣泛。另一方面,在工控裝置中除了主電源電路之外,還內建為各種控制系統提供電源電壓的輔助電源,輔助電源中廣泛採用了耐壓較低的Si-MOSFET和損耗較大的IGBT,在節能方面存在著很大的課題。

ROHM針對這些挑戰,於2015年推出了全球首款用來驅動高耐壓、低損耗SiC MOSFET的AC/DC轉換器控制IC,並一直致力於研發可充分發揮SiC功率半導體性能的IC,在業界中一直處於領先地位。此次又研發出全球首款內建SiC

MOSFET的AC/DC轉換IC,將加速SiC MOSFET AC/DC轉換器在工業領域的普及。

BM2SCQ12xT-LBZ採用了專為內建SiC MOSFET而研發的專用封裝,內建專為工控裝置輔助電源最佳化的SiC MOSFET驅動用閘極驅動電路等控制電路,以及1700V耐壓SiC MOSFET。作為全球首創的內建1700V耐壓SiC MOSFET的AC/DC轉換IC,本產品具有以下特點,有助於AC400V級工控裝置的小型化、節能化以及實現更高可靠性,從而提昇SiC MOSFET的AC/DC轉換器的普及。

英飛凌推出全新OptiMOS 6系列具備優異切換效能

英飛凌科技推出全新OptiMOS 6系列,為分立式功率MOSFET技術奠定新技術標準。新產品系列採用英飛凌薄晶圓技術,提供顯著的效能優勢,並涵蓋寬廣的電壓範圍。全新40 V MOSFET系列已針對SMPS的同步整流進行最佳化,適用於伺服器、桌上型電腦、無線充電器、快速充電器及ORing電路。

相較於前一代產品,新款OptiMOS 6 40 V的導通電阻降低了30%,具備更佳的優質係數(Qg x RDS(on)降低29%、Qgd x RDS(on)降低 46%)。因此新款裝置在SMPS應用中成為在寬廣輸出功率範圍內進行效率最佳化的理想選擇,避免在低負載和高負載狀況之間進行取捨。

其效率曲線明確顯示 OptiMOS 6在低輸出功率位準表現上優於前代產品,這歸功於其優異的切換效率。即使RDS(on)損耗較大時,但仍可在較高的輸出功率上維持上述優點。因此,可簡化散熱設計並減少並聯數量,進而降低系統成本。

ROHM推出600V耐壓超接合面MOSFET PrestoMOS

ROHM推出600V耐壓超接合面MOSFET「PrestoMOS」系列產品,在保持業界最快反向恢復時間的同時,提高設計靈活度,非常適用於空調、冰箱等生活家電的馬達驅動以及EV充電樁,而該「R60xxJNx系列」產品群於近期又新增共30種機型。

此次研發的新系列產品與傳統產品同樣利用了ROHM獨有的LifeTime控制技術,實現了業界最快的反向恢復時間。與IGBT相比,輕負載時的功耗成功減少了58%左右。另外,透過提高導通MOSFET所需要的電壓基準,可以避免發生造成損耗增加原因之一的誤開啟(Self Turn-on)。不僅如此,還透過最佳化內建二極體的特性,改善了超接合面 MOSFET 特有的軟恢復指數,可減少引發誤動作的雜訊干擾。透過減少這些阻礙使用者實行最佳化電路時的障礙,以提高設計靈活度。

據瞭解,在全球的功率需求中,近50%用於馬達驅動,隨著生活家電在新興國家的普及,馬達驅動帶來的功率消耗量預計會逐年增加。一般來說,包括空調和冰箱在內,生活家電多使用變頻電路進行馬達驅動,而變頻電路的開關元件通常會使用IGBT。然而,近年來在節能性能需求高漲的大趨勢下,可有效降低裝置穩定運行時功耗的MOSFET 正在逐步取代IGBT。

在這種背景下,ROHM於2012年成為第一家開始量產以業界最快反向恢復特性為特點的功率MOSFET PrestoMOS,且由於該系列產品可大大降低應用的功耗,因此受到市場的高度好評。

本系列產品透過最佳化MOSFET結構上存在的寄生電容,將開關時的額外閘極電壓降低了20%。另外,使MOSFET導通所需的閾值電壓(Vth)增加了約1.5倍,是“不易產生誤開啟現象的設計”。因此,擴大了用戶透過閘極電阻來進行損耗調節的範圍。

一般來說,超接合面 MOSFET 的內建二極體的恢復特性為硬恢復。然而,ROHM的R60xxJNx系列,透過最佳化結構,與傳統產品相比,新產品的軟恢復指數改善了 30%,不僅保持了業界最快的反向恢復時間(trr),還成功減少了雜訊干擾。因此,用戶可更輕易地透過閘極電阻來調節雜訊干擾。