GLOBALFOUNDRIES

戴樂格將非揮發性ReRAM技術授權與格羅方德平台

戴樂格半導體(Dialog)日前與半導體代工廠格羅方德(GLOBALFOUNDRIES)聯合宣布,已就Dialog向格羅方德授權導電橋接RAM(CBRAM)技術達成協議。該電阻式RAM(ReRAM)技術由Dialog半導體公司於2020年收購的Adesto Technologies首創。格羅方德首先將在其22FDX平台上以嵌入式非揮發性記憶體(NVM)選項提供Dialog的CBRAM,後續計畫將該技術拓展到其他平台。

Dialog獨有的且經過生產驗證的CBRAM技術是一項低功耗的NVM解決方案,專為物聯網(IoT)、5G連接、人工智慧(AI)等一系列應用而設計。低功耗、高讀/寫速度、更低的製造成本,對惡劣環境的耐受能力,使CBRAM特別適合消費、醫療和和特定的工業及汽車等應用。此外,CBRAM技術為這些市場中的產品所需的先進技術節點提供了具成本效益的嵌入式NVM。

Dialog半導體公司企業發展資深副總裁暨工業混合訊號業務部門總經理Mark Tyndall表示,CBRAM是Adesto傑出的標誌性儲存技術之一,該技術加入到Dialog產品組合中具有重要的戰略意義。此次與格羅方德的授權合作恰好證明Dialog和Adesto融合後開展業務的速度。展望未來,對我們和格羅方德牢固的合作關係非常有信心。此次授權協議不僅為行業提供了技術,也為Dialog在下一代系統級晶片(SoC)中採用先進CBRAM技術提供了機遇。

格羅方德資深副總裁暨汽車、工業和多市場業務部門總經理Mike Hogan表示,與Dialog的合作彰顯了格羅方德在為客戶進一步提供差異化優勢和增值的領域加大投資的承諾。Dialog的ReRAM技術是對eNVM解決方案系列非常好的補充。該記憶體解決方案結合FDX平台,將協助客戶進一步突破技術邊界,提供新一代安全的IoT和邊緣AI應用。

Dialog的CBRAM技術克服了ReRAM常見的整合和可靠性挑戰,提供了可靠且低成本的嵌入式記憶體,同時保留了ReRAM的低電壓運行能力。這意謂著可以實現比標準嵌入式快閃記憶體更低功耗的讀寫操作。

CBRAM將於2022年在22FDX平台上以嵌入式NVM選項向格羅方德的客戶提供。透過IP訂製,客戶可以修改CBRAM單元以優化其SoC設計,提升安全性,或將單元調整成適合新的應用。此外,CBRAM作為一種「後段製程」技術,可以相對容易地整合到其他製程節點中。

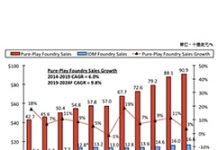

5G需求超有力 2020年純晶圓代工業者營收大增近2成

IC Insights發表最新修正的預估數據,在5G所帶來的行動裝置、電信設備需求刺激下,2020年全球純晶圓代工業者的營收,可望比2019年大幅成長19%。如果純晶圓代工業者真能繳出如此亮麗的成績,2020年將是純晶圓代工業者有史以來營運成長幅度最高的一年。根據IC Insights的定義,純晶圓代工廠是指專注晶圓代工服務,本身不設計晶片的公司。這類公司包含台積電、格羅方德(GlobalFoundries)、聯電與中芯國際。

相較之下,同樣提供晶圓代工服務的整合元件製造商(IDM),2020年相關業務的表現恐將比2019年衰退。IC Insights預期,2020年IDM業者的晶圓代工服務營收,將僅達128億美元,比2019年的130億美元衰退2億美元。事實上,除了2017年將三星電子(Samsung Electronics)的晶圓代工業績改歸列為IDM業者,導致IDM晶圓代工業績明顯成長外,IDM廠在晶圓代工領域的營收表現並不亮眼,未來的成長速度也相對平緩。

格羅方德購紐約州馬爾他土地 定位先進晶圓廠

格羅方德(GlobalFoundries)於日前宣布,取得一份購買選擇權協議,能購得位於紐約州馬爾他鎮約66英畝的未開發土地,相鄰格羅方德最先進的Fab 8,同時也在路德森林科技園區(LFTC)附近。

這塊土地位於紐約州能源研究暨發展局(NYSERDA)薩拉托加科技能源園區(STEP)的東南端,近Fab 8和Hermes路間的Stonebreak路延伸段,土地以公平市場價格售出,而購買價格則由獨立評估師進行鑑定。格羅方德已行使選擇權協議購買土地,並著手擴建Fab 8,以期能合乎分區法規與客戶要求。

格羅方德美國晶圓廠資深副總裁兼總經理Ron Sampson表示,隨著我國對半導體製造的投資共識日益成長,得以在位於美國格羅方德最先進的製造工廠中,快速實施我們的成長計畫,這點對我們來說至關重要。有了這份選擇權協議,格羅方德將擁有更多空間擴展我們的領域,並將Fab 8定位為帶動薩拉托加郡和紐約州未來的經濟成長,同時加強美國在半導體製造業中的領導地位。

格羅方德在位於上紐約州的最先進製造廠–Fab 8投資了超過130億美元,聘有近3000名員工。經宣布,將推動此廠符合美國國際武器貿易條例(ITAR)標準,以及出口管制條例(EAR)下嚴格限制的出口管制分類編碼(ECCN)。

聚焦AI加速器需求 格羅方德12LP+ FinFET製程準備量產

格羅方德(Globalfoundries)日前宣布,旗下最先進的FinFET解決方案「12LP+」已通過技術驗證,準備投入生產。

格羅方德的差異化「12LP+」解決方案主要針對AI訓練以及推論應用進行優化。本解決方案建立於驗證過的平台上,具有強大的製造生態系統,可為晶片設計師帶來高效能的開發體驗,及快速的上市時間。

為達到性能、功耗和面積的無懈組合,12LP+導入了若干新功能,包含更新後的標準元件庫、用於2.5D封裝的中介板,與一個低功耗的0.5V Vmin SRAM記憶單元,以支援AI處理器與記憶體之間的低延遲和低功耗數據往複,得到專為符合快速增長之AI市場的特定需所制定的半導體解決方案。

格羅方德資深副總裁兼運算暨有線基礎架構部總經理Amir Faintuch表示,AI會成為我們有生之年最具顛覆性的技術。越發明顯的是,AI系統的效能,特別是能運用一瓦的功率執行多少次運作,成為企業決定投資數據中心或頂尖AI應用的關鍵因素之一。我們的全新12LP+解決方案能夠直接處理這項挑戰,而AI正是本解決方案在進行設計以及優化時,不變的初衷。

12LP+建立在格羅方德14nm/12LP平台基礎上,早已出貨超過100萬個晶圓。許多公司包含Enflame和Tenstorrent等,都將格羅方德的12LP用於AI加速器相關應用。藉由與AI客戶緊密合作並互相學習,格羅方德開發出12LP+解決方案,為AI產業中的設計師提供更大的差異性以及更高的價值,並將開發及生產成本降至最低。

12LP+性能得以增強的特點包括:與12LP相比,將SoC級的邏輯性能提高20%,而在邏輯晶片尺寸方面則縮小10%。這些進階功能是透過12LP+的新一代標準元件庫加以達成,其中包含性能驅動的面積優化組件、單一Fin單元、新的低壓SRAM記憶單元以及改良版類比佈局設計規則。

格羅方德的AI設計參考套件及其協同開發、封裝和晶圓生產後續統包服務,增強了格羅方德12LP+專業應用解決方案的能力。在設計低功耗、經濟實惠且針對AI應用進行優化的電路時,更共同提供絕佳的整體體驗。格羅方德與生態系統夥伴間的緊密合作,亦造就了符合成本效益的開發費用,並縮短了上市時間。

除了12LP現有的IP產品組合之外,格羅方德亦將擴展12LP+的驗證範圍,藉此將PCIe 3/4/5和USB 2/3併進主機處理器。此外,也將HBM2/2e、DDR/LPDDR4/4x和GDDR6納入外部記憶體和晶片間互連技術,使設計師和客戶往小晶片架構發展。

格羅方德的12LP+解決方案已通過技術驗證,目前已準備在紐約州馬爾他的Fab 8進行生產,預計在2020下半年進行試產。格羅方德先前已宣布,將使Fab 8符合美國國際武器貿易條例(ITAR)標準和出口管制條例(EAR)於今年底生效的管制措施,透過這項舉措為Fab 8所生產的國防相關應用、裝置或組件提供機密性和完整保護。

格羅方德之德勒斯登晶圓廠獲頒安全產品製造認證

德國聯邦資訊安全局(BSI)已根據最新版「資訊技術安全評估共同準則」(國際共同準則ISO 15408,CC認證3.1版),認證格羅方德(GLOBALFOUNDRIES)德勒斯登廠的產品安全等級。在4月27日當天的「虛擬頒獎典禮」上,由格羅方德資深副總裁暨德勒斯登廠總經理Thomas Morgenstern博士代表受獎,德國聯邦資訊安全局局長Arne Schönbohm,以及薩克森邦部長暨總理府秘書長Oliver Schenk則擔任頒獎人。

格羅方德德勒斯登廠總經理Thomas Morgenstern表示,BSI已證明,公司所有系統及製程均符合國際共同準則ISO規範的最高標準。這是德勒斯登廠重要的里程碑,因為這讓格羅方德得以進軍要求很高的新市場。隨著晶片在日常生活及經濟體系中的普及化,大眾將在未來的日子裡,更需要安全及值得信賴的晶片解決方案。對於格羅方德在德勒斯登廠能為硬體安全做出進一步貢獻的新契機,該公司深感雀躍。格羅方德將持續致力於成為客戶眼中最值得信賴、也是最安全的晶圓代工夥伴。

榮獲安全證書後,其德勒斯登廠所生產的晶片不但可供金融交易服務、智慧卡及數位ID及其他產品使用,還可應用於公共部門或是在生產過程中需要高度安全性及完整性的產業。兩年來,格羅方德在德勒斯登廠已投入數百萬歐元資金,將廠內安全及資訊科技系統提至最高等級。荷蘭半導體公司恩智浦(NXP)則是格羅方德德國廠通過認證的關鍵推手。為了格羅方德的Shield計畫,德勒斯登廠亦加入新加坡廠及美國各單位的行列,在安全製造上獲得了產業、客戶及政府的最高認可。

安謀(ARM)連接技術部門副總裁暨總經理Vincent Korstanje表示,若想成功擴大經營規模,從晶片的設計到部署,安全是蜂巢式物聯網供應鏈在每個階段的關鍵。這項認證讓格羅方德的22FDX技術,有能力以符合經濟效益的方式,製造出安全連網的產品。當使用這項製程技術時,格羅方德為需要迅速發展新應用的夥伴們,提供了最高階的資訊安全。

薩克森邦部長暨總理府秘書長Oliver Schenk更指出,格羅方德成功獲得BSI認證,進一步證明德勒斯登在微電子這個領域可提供多元的服務範疇。不只其客戶受惠於這項新的安全認證,連『薩克森矽谷』(Silicon Saxony)數位生態系統也因此壯大。深感歐洲的科技獨立主權日益重要的同時,對於位在遠端供應商的依賴程度也必須要同步減低。本人為薩克森的企業感到開心,隨著BSI在德勒斯登鄰近的弗賴塔爾(Freital)成立新辦事處,BSI也將直接成為薩克森自由邦的夥伴。

半導體先進製程超限戰 5nm成下一個金雞母

半導體先進製程已經與晶片效能畫上等號,因此,除了品牌與功能之外,對於晶片商來說,採用先進製程也是技術行銷的一大重點,晶片的成功與擴散很大程度上取決於IC製造商能否繼續提供更多的性能和功能。隨著主流CMOS製程達到其理論、實用和經濟極限,降低IC成本不可避免地與不斷成長的技術和晶圓廠製造能力相提並論。台積電已經正式量產的5奈米(nm)製程將成為下一個製程爭奪重點,並為該公司創造更多營收。

2015~2021年主要晶圓廠製程發展進度 資料來源:IC Insights(2/2020)

根據產業研究機構IC Insights最新研究指出,許多IC公司現在正在設計10nm和7nm製程的高階微處理器、應用處理器和其他高級邏輯設備。在半導體製造領域,採用先進製程具有明顯的優勢。在2019年,台積電是唯一使用7奈米製程技術的晶圓代工廠,也成為各家晶片廠商的「名牌」,台積電的先進製程創造大量營收,7奈米製程也出現排隊狀況,一線大廠才能優先取得產能,搶先量產產品,並為廠商拿來作為產品行銷的重點技術。

也由於IC設計廠商排隊採用7奈米製程製造最新設計,推升台積電單片晶圓總收入。台積電2019年每片晶圓收入高於2014年13%,也是全球唯一一家達成此目標的晶圓廠。相較之下,GlobalFoundries、聨電UMC和中芯國際(SMIC)2019年每片晶圓收入,與2014年相較分別下降了2%、14%和19%,這三家廠商的最先進製程約在12/14奈米。

除了代工和邏輯IC製造外,三星、美光、SK Hynix和Kioxia/WD等記憶體供應商都在使用先進製程來製造其DRAM和快閃記憶體(Flash)元件。無論設備類型如何,IC產業都已經發展到只有極少數的公司可以開發前瞻製程技術並製造前瞻IC的地步。日益成長的設計和製造挑戰以及成本已經將積體電路領域門檻變的越來越高。

台積/格芯訴訟戰爭閃電落幕 雙方專利將交互授權

格芯(GlobalFoundries)和台積電(TSMC)宣布撤銷雙方之間及其客戶的訴訟。兩家公司已經達成全球專利交互授權協議,隨著雙方不斷在半導體研發上有龐大的投資,故範圍涵蓋雙方全球現有及未來十年內申請的半導體專利。

格芯在2019年8月時在美國和德國提起了多個法律訴訟,指控台積電所使用的半導體製造技術侵犯16項格芯專利。這些訴訟分別向美國國際貿易委員會(ITC)、美國聯邦法院德拉瓦分院和德州西區分院以及德國杜塞爾多夫地區法院和曼海姆地區法院提交。

在提起法律訴訟的同時,格芯還申請了法院禁制令,以阻止總部位於台灣、在半導體生產領域處於壟斷地位的台積電使用侵權技術生產的產品進口至美國與德國。這些法律訴訟要求格芯指名台積電的主要客戶以及下游電子公司,後者在大多數情況下才會包含了台積電侵權技術產品的實際進口。格芯還基於台積電使用格芯專有技術而產生的數百億美元的銷售額而向台積電提出了巨額的損害賠償請求。

而在格芯提出訴訟不久後,台積電也隨即做出反擊,於2019年9月在美國、德國及新加坡三地對格芯提出多項法律訴訟,控告格芯侵犯台積公司40奈米、28奈米、22奈米、14奈米以及12奈米等製程之25項專利。台積公司在此訴訟之中要求法院核發禁制令,禁止格羅方德生產及銷售侵權之半導體產品,亦對非法使用台積公司半導體專利技術與銷售侵權產品之格羅方德尋求實質性的損害賠償。

訴訟中的25項台積公司專利涉及多種技術,包括FinFET設計、淺溝槽隔離技術、雙重曝光方法、先進密封環及閘極結構、以及創新的接觸蝕刻停止層設計,這些特定技術涵蓋了成熟及先進半導體製程技術的核心功能。

然而,就在雙方交鋒不久後,這場專利戰爭就在近日閃電落幕。雙方宣布撤銷雙方之間及其客戶的訴訟,且已達成全球專利交互授權協議,範圍涵蓋雙方全球現有及未來十年內申請的半導體專利;同時,該協議也保證格芯和台積電有營運自由,而雙方的客戶也確保可繼續獲得完整技術和服務支援。

台積電與格芯訴訟戰閃電和解。

台積電副總經理暨法務長方淑華表示,半導體產業的競爭一直以來都相當激烈,驅使業者追求技術創新,此次決議是相當正面的發展,使我們持續致力於滿足客戶的技術需求,維持創新活力,並使整個半導體產業更加蓬勃昌盛。

格羅方德執行長Thomas Caulfield則指出,此項協議認可了雙方智慧財產的實力,使兩家公司能夠聚焦於創新,並為雙方各自的全球客戶提供更好的服務。同時,該協議也確保了格羅方德持續成長的能力。

台積電和格芯透過全球專利交互授權全面解決雙方爭訟

台灣積體電路製造股份有限公司(TSMC)與格芯(GlobalFoundries)今(29)日宣布撤銷雙方之間及與其客戶相關的所有法律訴訟。隨著台積公司和格芯持續大幅投資半導體研究與開發,兩家公司已就其現有及未來十年將申請之半導體技術專利達成全球專利交互授權協議。

此項協議將確保台積公司及格芯的營運不受限制,雙方客戶並可持續獲得兩家公司各自完整的技術及服務。

格芯執行長Thomas Caulfield表示,很高興能夠很快地和台積電達成協議,此項協議認可了雙方智慧財產的實力,使兩家公司能夠聚焦於創新,並為雙方各自的全球客戶提供更好的服務。同時,該協議也確保了格芯持續成長的能力,對於身為全球經濟核心的半導體業而言,也有利整個產業的成功發展。

台積公司副總經理暨法務長方淑華表示,半導體產業的競爭一直以來都相當激烈,驅使業者追求技術創新,以豐富全球數百萬人的生活。台積公司已投入數百億美元資金進行技術創新,以達今日的領導地位。此項協議是相當樂見的正面發展,使我們持續致力於滿足客戶的技術需求,維持創新活力,並使整個半導體產業更加蓬勃昌盛。

滿足分眾市場 IC異質整合技術百花齊放

人工智慧(AI)、車聯網、5G等應用相繼興起,且皆須使用到高速運算、高速傳輸、低延遲、低耗能的先進功能晶片,在製程微縮技術只有少數幾家晶圓代工、IC製造業者可發展的情況下,異質整合(Heterogeneous Integration Design Architecture System, HIDAS)成為IC晶片的創新動能。同時,隨著應用市場更加的多元,每項產品的成本、性能和目標族群都不同,因此所需的異質整合技術也不全然相同,有的需要記憶體+邏輯晶片,而有的則需感測器+記憶體+邏輯晶片等,市場分眾化趨勢逐漸浮現。為此,IC代工、製造以及半導體設備業者也持續推出新的異質整合技術,以滿足市場需求。

成本/效能需求不同 異質整合走向分眾化

工研院電子與光電系統研究所所長吳志毅(圖1)表示,所謂的異質整合,廣義而言,就是將兩種不同的晶片,例如記憶體+邏輯晶片、光電+電子元件等,透過封裝、3D堆疊等技術整合在一起。換句話說,將兩種不同製程、不同性質的晶片整合在一起,都可稱為是異質整合。

圖1 工研院電子與光電系統研究所所長吳志毅表示,依產品性能、成本不同,異質整合將走向分眾化。

異質整合是目前半導體產業熱門議題,也有許多業者投入發展,進而市場上有著許多解決方案。對此,吳志毅說明,在異質整合發展上,各家廠商著重的市場和技術都不一樣,因而會衍生出許多種整合方式,例如有所謂的2.5D、3D或是採用封裝的方式。然而,不論是何種技術,其核心價值都是將兩種完全不同的晶片整合成一個,這便是異質整合的概念;換個例子來說,要將兩樣物品黏在一起,可以選擇膠水、膠帶或強力膠等,有很多種方式,異質整合便是同樣的道理,端看業者的市場和成本考量人選擇要用何種整合技術。

吳志毅補充,半導體技術著重的永遠都是成本和效能。部分業者之所以會發展3D整合方案,主要原因是3D IC具有更好的效能,但相對的3D IC的成本也較高,因此適用於高階產品市場,例如AI晶片。至於原有的2.5D整合技術,並非3D IC問世之後就沒有市場,2.5D IC的性能雖然不比3D IC,但相對的成本也較低,適用於有成本考量的企業或產品。

吳志毅說,換個方式譬喻,當7奈米製程出現後,不代表所有產品都會轉成7奈米,像是14、16、28奈米,甚至是90奈米,都還有其市場,業者會依應用市場、產品設計需求和成本,選擇所需的製程技術,而異質整合也是同樣,業者會根據所需的產品性價比、效能以及市場,選擇最適合的異質整合技術。也因此,未來異質整合勢必將會出現市場分眾化的趨勢。

吳志毅認為,這對於晶圓代工廠,或是晶片製造商等也是一個新的機會。現今半導體產業只剩三家業者(台積電、三星、英特爾)能繼續推進摩爾定律(製程微縮化),而其他業者如聯電、格芯是否就沒有其他發展空間?並非如此,異質整合便是一個新的機會。這些晶圓代工、IC設計或者是封裝業者不一定要發展更先進的製程,但是卻可以透過異質整合,將原本不同性質的晶片整合成體積小、高性能的晶片,實現更多創新應用。

IC代工/製造/設備商全體動員

上述提到,異質整合為半導體產業發展帶來新契機,同時因應多元的應用市場,異質整合日後將朝分眾化發展,為此,晶圓代工業者、晶片商或是半導體設備商皆積極投入發展,各式解決方案也紛紛亮相。

英特爾再推三大封裝新技術

英特爾(Intel)日前展出先進封裝技術並推出了一系列全新基礎工具,包括將EMIB和Foveros技術相互結合的創新應用,以及全新的全方位互連(Omni-Directional Interconnect, ODI)技術。

英特爾指出,晶片封裝在電子供應鏈中看似不起眼,卻一直發揮關鍵作用,而隨著電子產業正在邁向以資料為中心的時代,先進封裝將比過去發揮更重大的作用。封裝不僅僅是製造過程的最後一步,同時也正成為產品創新的催化劑。先進的封裝技術能夠整合多種製程的運算引擎,將大幅提高產品性能,同時又可縮小面積,並對系統架構進行全面改造。為此,英特爾分享三項全新技術,分別為Co-EMIB、ODI和MDIO。Co-EMIB能連接更高的運算性能和能力,並能夠讓兩個或多個Foveros元件互連,設計人員還能夠以非常高的頻寬和非常低的功耗連接模擬器、記憶體和其他模組。

ODI技術則為封裝中小晶片之間的全方位互連通訊提供了更大的靈活性。頂部晶片可以像EMIB技術一樣與其他小晶片進行通訊,同時還可以像Foveros技術一樣,通過矽通孔(TSV)與下面的底部裸片進行垂直通訊。同時,該技術還利用大的垂直通孔直接從封裝基板向頂部裸片供電,這種大通孔比傳統的矽通孔大得多,其電阻更低,因而可提供更穩定的電力傳輸;並透過堆疊實現更高頻寬和更低延遲。此一方法減少基底晶片中所需的矽通孔數量,為主動元件釋放了更多的面積,優化裸片尺寸。

至於MDIO技術為基於其高級介面匯流排(AIB)實體層互連技術,支援對小晶片IP模組庫的模組化系統設計,能提供更高能效,實現AIB技術兩倍以上的回應速度和頻寬密度。

格芯/台積紛推3D方案

為搶搭異質整合浪潮,晶圓代工業者格芯(GlobalFoundries)近期宣布旗下基於Arm架構的高密度3D測試晶片已成功投片生產,可滿足資料中心、邊緣運算和高階消費性電子產品應用的需求。

據悉,此款晶片可提升AI、機器學習(ML)和高階消費性電子及無線解決方案等的運算系統性能與效能,其採用該公司12nm Leading-Performance(12LP)FinFET製程製造,並運用Arm 3D網狀互連技術,讓資料數據更直接地傳輸至其他內核,達到延遲最小化,提高資料傳輸速率,滿足資料中心、邊緣運算和高階消費性電子產品應用的需求。

此外,兩公司還驗證一種3D可測試設計(Design-for-Test, DFT)方法,使用格芯的混合式晶圓對晶圓接合,每平方公厘多達100萬個3D連接,拓展12nm設計在未來的應用。

格芯發言人表示,3D可測試設計方法為屬於異質整合技術,該公司和Arm共同驗證了此一測試設計方法,使用混合式晶圓對晶圓接合,使得每平方公厘的3D連接數多達100萬個。用於3D IC的DFT架構實現了各種晶片的模組測試方法,其中具有嵌入式IP核心、基於穿透矽通孔的晶粒間互連和外部I/O可作為獨立的單元進行測試,進而可靈活優化的3D IC測試流程。DFT是一項能夠採用3D技術的重要測試設計方法,而3D DFT架構具備支持板級互連測試的特色;該公司的差異化F2F晶圓鍵合技術為工程設計人員提供了異構邏輯和邏輯/記憶體整合。

格芯發言人說明,3D晶圓架構具有減少線長的本質能力,是減輕下一代微型處理器設計中互連問題的最有潛力的解決方案之一;而3D技術和異質整合功能為新設計方法提供了低延遲、高頻寬的優勢。對於異質整合來說,雖然沒有其餘的技術層面挑戰,但針對規劃、執行和驗證2.5D和3D IC的設計工具、薄晶圓處理技術、熱管理和測試等,這些製程仍需要更好的解決方案。

由於目前異質整合生態系統成熟緩慢,主要的挑戰在於單位成本高昂、低產量和實行風險,業界正在努力降低製程成本並簡化整個產業合作。未來格芯會與所有主要EDA合作夥伴密切合作,將3D IC放置在庫中,然後使用晶圓對晶圓鍵合進行組裝,使複雜的晶圓設計和組裝成果更快且更低成本。

另一方面,繼整合型扇出(InFO)和CoWoS封裝技術後,台積電也於之前發表的「3D多晶片與系統整合晶片(SoIC)的整合」論文中,揭露了完整的3D整合技術。此項系統整合晶片解決方案將不同尺寸、製程技術,以及材料的已知良好裸晶直接堆疊在一起。

論文中提到,相較於傳統使用微凸塊(Micro-bumps)的3D積體電路解決方案,此一系統整合晶片的凸塊密度與速度高出數倍,同時大幅減少功耗。此外,系統整合晶片是前段製程整合解決方案,在封裝之前連結兩個或更多的裸晶;因此,系統整合晶片組能夠利用該公司的InFO或CoWoS的後端先進封裝技術來進一步整合其他晶片,打造一個強大的「3D×3D」系統級解決方案。

台積電全球營銷主管Godfrey Cheng於部落格上指出,該公司可透過先進的封裝技術,包括基於矽製程的中介層(Interposer)或扇出製程的小晶片(Chiplet)等方法,將記憶體及邏輯晶片核心緊密整合,未來還能夠將晶圓及晶圓堆疊,提供客戶更好的晶片密度及效能。

實現異質整合 EVG/Lam各有解方

除了晶圓代工、IC製造業者積極發展異質整合技術外,半導體設備商也不落人後。EVG亞太區業務總監Thorsten Matthias(圖2)表示,如今許多新元件因無法突破技術或成本上的關卡,想要從傳統元件微縮和從系統單晶片架構下手以提升效能,已不再是可行的選項。而隨著現今許多技術領先的製造廠藉由投入影像感測器製造及矽穿孔晶圓級封裝,在異質整合方面已累積數年與數百萬片晶圓製造的經驗,使得異質整合成為半導體製造的另一項利器。

圖2 EVG亞太區業務總監Thorsten Matthias表示,異質整合的各項優點與好處已廣受業界認可。

Matthias指出,異質整合的各項優點與好處多年來已廣受業界認可,包括降低設計與測試的複雜度、縮短上市時程及降低成本;異質整合也顛覆許多層面,包括設計、架構、製程技術及整個供應鏈和從晶圓委外到封裝測試(OSAT)產業生態系統。

然而,要實現異質整合也非是一蹴可幾,需要新技術、新電晶體架構和材料等,像是薄膜轉移(Layer...

格芯發布3D測試晶片/技術加入異質整合戰局

為滿足資料中心、人工智慧(AI)、5G等新興技術發展,半導體設計除持續朝微縮製程邁進之外,異質整合技術也成為下一波IC晶片創新動能。為此,IC設計業者、晶圓代工廠等皆紛紛投入發展,例如格芯(GLOBALFOUNDRIES)近期便宣布旗下基於Arm架構的高密度3D測試晶片已成功流片生產,可滿足資料中心、邊緣運算和高端消費性電子產品應用的需求。

據悉,此款晶片可提升AI、機器學習(ML)和高端消費性電子及無線解決方案等的運算系统性能與效能,其採用該公司12nm Leading-Performance(12LP)FinFET製程製造,並運用Arm 3D網狀互連技術,讓資料數據更直接地傳輸至其他内核,達到延遲最小化,提高資料傳輸速率,滿足資料中心、邊緣運算和高端消費性電子產品應用的需求。

此外,兩公司還驗證了一種3D可測試設計(Design-for-Test, DFT)方法,使用格芯的混合式晶圓對晶圓接合,每平方公厘多達100萬個3D連接,拓展12nm設計在未來的應用。

格芯發言人表示,3D可測試設計方法為屬於異質整合技術,該公司和Arm共同驗證了此一測試設計方法,使用格芯的混合式晶圓對晶圓接合,每平方公厘多達 100萬個3D連接。用於3D IC的DFT架構實現了各種晶片的模組測試方法,其中具有嵌入式IP核心、基於穿透矽通孔的晶粒間互連和外部I/O可作為獨立的單元進行測試,從而可靈活優化的3D IC測試流程。DFT是一項能夠採用3D技術的重要測試設計方法而3D DFT架構具備支持板級互連測試的特色;而該公司的差異化F2F晶圓鍵合技術為工程設計人員提供了異構邏輯和邏輯/記憶體整合。

格芯發言人說明,3D晶圓架構具有減少線長的本質能力,是減輕下一代微型處理器設計中互連問題的最有潛力的解決方案之一;而3D技術和異質整合功能為新設計方法提供了低延遲、高帶寬的優勢。對於異質整合來說,雖然沒有其餘的技術層面挑戰,但針對規劃、執行和驗證2.5D和3D IC的設計工具、薄晶圓處理技術、熱管理和測試等,這些製程仍需要更好的解決方案。

由於目前異質整合生態系統成熟緩慢,主要的挑戰在於單位成本高昂、低產量和實行風險,業界正在努力降低製程成本並簡化整個行業合作。未來格芯會與所有主要EDA合作夥伴密切合作,將3D IC放置在庫中,然後使用晶圓對晶圓鍵合進行組裝,使複雜的晶圓設計和組裝成果更快且更低成本。

格芯推3D IC提升邊緣運算、高端消費性等電子產品應用需求。