Foundry

Mentor EDA軟體支援三星Foundry 5/4奈米製程技術

Mentor旗下的Calibre nmPlatform和Analog FastSPICE(AFS)自訂和類比/混合訊號(AMS)電路驗證平台已通過三星Foundry的最新製程技術認證。客戶現在可以在三星的5/4奈米FinFET製程上使用這些產品,為其先進的IC設計Tapeouts進行驗證和Sign-off。

三星5奈米FinFET製程具備優異的功率、效能和面積(PPA)特性,其自身的增強功能,結合更精細的5奈米幾何尺寸,能夠提供比前幾代製程節點更加突出的效能表現。而除Calibre nmDRC之外,通過三星Foundry新製程認證的Mentor工具還包括:

Calibre xACT可解決與先進奈米設計相關的技術挑戰,包括多重曝光、局部互連、高複雜度和嚴苛的約束條件等。其獨特的混合引擎可為FinFET這類細微的3D結構提供至關重要的場解算器準確度,並具備快速處理能力。

Calibre YieldEnhancer具有SmartFill和ECO Fill功能,客戶可控制設計平面度並縮短反覆設計的周轉時間,且可透過自動化PowerVia流程減少IR壓降,協助客戶提高設計可靠度。

Calibre PERC能夠對實體布局和網表進行獨特的整合分析,自動執行複雜的可靠度驗證檢查,協助客戶克服靜電放電和閂鎖(Latch-up)可靠度的相關挑戰。

Calibre nmLVS可作為三星Foundry萃取流程的前端。因應不斷增加的布局複雜度要求,以及設計團隊對先進運算的更高需求,使在驗證複雜電路的同時,仍能在預期的執行時間内達成先進製程節點的設計目標。

Calibre RealTime數位和自訂介面平台利用同樣通過三星Foundry認證予批量Calibre的設計套件,在數位和自訂設計流程中即時地實現sign-off質量的DRC檢查。在先進和成熟節點設計的DRC收斂期間,這些介面可提供顯著的生產力優勢,使客戶能快速優化其手動的DRC修正,以節省更多時間來實現PPA目標。

Mentor的AFS平台被三星Foundry的器件模型和設計套件所支援,雙方的共同客戶能够以此在驗證類比、RF、混合訊號、記憶體和自訂數位電路時,實現比傳統SPICE模擬器速度更快的奈米級SPICE準確度。

2019全球晶圓廠支出下滑 2020將再創新高

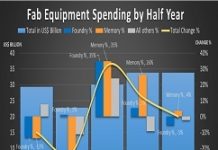

國際半導體產業協會(SEMI)旗下產業研究與統計事業群(Industry & Statistics Group)所發表的2019年第一季全球晶圓廠預測(World Fab Forecast)報告指出,2019全球晶圓廠設備支出預期將下滑14%至$530億美元,但2020年將強勁復甦27%達$670億美元,並締造新高紀綠。受到記憶體產業衰退影響,已連續三年成長的晶圓廠設備支出榮景即將在2019年告一段落。

過去兩年間,記憶體占年度所有設備支出比重約為55%,2019年這個數字預期將下探45%,但2020年會再回升到55%。由於記憶體占整體支出比重極高,記憶體市場任何波動都會影響整體設備支出。根據統計圖顯示,2018年下半年起每半年市場都有所變動,估計未來也是如此。

檢視每半年的晶圓廠設備支出趨勢圖後可以看出,由於2018下半年起記憶體庫存的增加以及終端需求疲軟,導致2018下半年DRAM和NAND(3D NAND)相關支出開始修正,進而拖累記憶體支出下滑14%。這股下滑趨勢將延續到2019年上半年,屆時記憶體支出將下滑36%,但預計到下半年相關支出可望反彈35%。儘管2019年下半市場可望鹹魚翻身,報告認為2019年全年記憶體支出仍將較2018年下滑30%。

晶圓代工是晶圓廠設備支出的第二大項目,過去兩年間,每年占整體支出比重約在25%到30%之間。SEMI預期2019和2020年的比重將持穩在30%左右。

雖然晶圓代工設備支出的波動程度通常小於記憶體部門,面對市場變化還是無法完全免疫。舉例來說,記憶體部門開始衰退之後,2018年下半晶圓代工設備支出也比上半年下滑13%。