DRAM

美光RDIMM力助資料中心效能大躍進

美光科技(Micron)日前宣布其DDR5暫存器記憶體模組(RDIMM)已進入樣品測試階段,該產品採用1znm製程技術。美光DDR5將提升記憶體效能85%,並能因應次世代伺服器的工作負載量。當資料中心系統架構需要快速供應不斷擴充的處理器核心數及更高記憶體頻寬和容量時,DDR5不僅提供雙倍記憶體容量,也展現更高可靠度。

美光電腦運算與網路業務部門資深副總裁暨總經理Tom Eby表示,資料中心的工作負載量將會不斷面臨挑戰,因為幾乎所有應用程式的資料均急遽增長,而資料中心必須從中擷取數值。要滿足這些工作負載量的關鍵便是更高效能、容量與品質的記憶體。美光DDR5 RDIMM樣品測試讓業界能向解鎖次世代數據密集應用程式的價值邁進一步。

因快速擴展的資料集以及需要大量運算的應用程式而產生的進階工作負載量,導致處理器核心數的成長,而目前的DRAM技術將導致頻寬不足。有鑑於此,相較於DDR4,DDR5將提供超過1.85倍的效能成長,也將帶來更高的可靠度、可用性與可維護性(RAS),以因應當代資料中心需求。

添加DDR5功能 SDRAM效能/部署能力大增

隨著記憶體密度上升,記憶庫(Bank)的數量也須增加,以容納更高的記憶體密度。新一代的DDR5標準將記憶庫組(Bank Group)的數量擴充一倍,並且同時維持各組的記憶庫數量不變。另外,由於能夠在任一時間點打開更多的頁面(Page),以及提升高分頁命中率(High Page-hit)的統計概率,整體的系統效率應可加強。

記憶庫組到記憶庫組的交錯時序存取(Interleaved Timing)短於特定記憶庫組內記憶庫間的存取。這些時序參數同時有「長」的時序定義(tCCD_L、tWTR_L、 tRRD_L)和「短」的時序定義(tCCD_S、tWTR_S、tRRD_S)。長的時序係指記憶庫組內記憶庫到記憶庫(Bank-to-bank)的存取,而短的時序則是指存取不同的記憶庫組(圖1)。為便於理解,在此補充說明:tCCD_L可接近tCCD_S的兩倍。增加的記憶庫組可提高短時序的使用概率,進而減輕內部時序限制。

圖1 DDR5記憶庫/記憶庫組的時序

資料突發長度增加

DDR5 SDRAM將預設的突發長度從BL8加到BL16,並提高了指令/位址和資料匯流排的效率。以同樣的讀取或寫入CA 匯流排的作業而言,資料匯流排現可提供兩倍的資料,同時還能將對IO/陣列時序限制的暴露侷限於相同的記憶庫內。透過減少存取給定資料量所需的指令數,DDR5 SDRAM還能降低讀寫作業所需功率。

此外,突發長度增加後,存取相同之64B快取行(Cache Line)資料負載所需的IO數也減少。由於預設的突發長度增加,DDR5 DIMM架構得以具備雙子通道(圖2),進而提高通道的整體並行性、靈活性和數量。針對使用128B快取行負載的系統,DDR5亦特別為×4配置的裝備提供突發長度為32位元的選項,而能進一步改善指令/位址、資料匯流排效率及總體功率表現。

圖2 DDR5 40-Pin子通道DIMM範例

刷新指令

除了適用於DDR5和早期DDR SDRAM產品的標準ALL-BANK REFRESH指令(REFab)外,DDR5還導入了SAME-BANK REFRESH(REFsb)指令。當REFsb指令發出時,它會依照記憶庫位元(Bank Bits)透過指令/位址位元所指定的目標,在所有記憶庫組中鎖定同樣的記憶庫。

SDRAM設備的REFRESH指令會要求在指令發出前,被鎖定刷新的記憶庫須處於閒置狀態(預充電,無資料活動);而且,在REFRESH指令執行期間,那些記憶庫均不能重啟後續的寫入和讀取活動(時序參數tRFC)。REFRESH指令以平均週期間隔發送(時序參數tREFI)。對於REFab指令,系統必須於發出指令前確保所有記憶庫均為閒置狀態;針對16Gb DDR5 SDRAM裝置,在「正常」刷新模式下平均每3.9μs發送一次,每次持續295ns。

REFsb指令的效能優勢在於,在指令發出前,各記憶庫組內只需有一個記憶庫保持閒置狀態。當發出REFsb指令時,其餘的12個記憶庫(圖3)不必處於閒置;而且,對於非刷新記憶庫的唯一時序限制是相同記憶庫刷新到啟動的延遲 (Same-bank-refresh-to-activate Delay)(時序參數tREFSBRD)。REFsb指令只能以倍精度刷新(FGR)模式發送,意即各記憶庫平均須每1.95μs接收一次REFRESH指令。針對16Gb DDR5 SDRAM裝置,REFsb則僅持續130ns,這也將系統存取鎖定的對象(tRFCsb)減至主動刷新的記憶庫上(圖3)。使用REFsb時還有一個限制:每個「相同記憶庫」(Same Bank)都須在第二個REFsb指令發出前收到一個REFsb指令,但REFsb指令可以任一記憶庫的順序發送。

圖3 DDR5 REFsb與記憶庫的對應

模擬結果顯示,與REFsb相比,使用REFsb時系統效能吞吐量加大6%到9%(會因讀/寫指令比率不同而異),如圖4所示。另外,REFsb將刷新對平均閒置延遲時間的衝擊從11.2ns減為5.0ns。這些計算乃基於標準排隊理論所得,並適用於具隨機驅動資料流量的單個記憶庫。

圖4 DDR5系統吞吐效能改進

效能改進

以上述特點模擬64B隨機存取的工作負載後發現,與DDR4雙Rank的3200MT/s模組相比,效能顯著提高(圖5)。在此模擬情境中,假設各系統有8個通道與1DPC。

圖5 DDR5 不同速度/記憶庫模組的效能改進

透過從DDR5設備輸出資料前在READ指令期間進行校正,RAS的提升(如on-die...

實現高畫質影像處理 Western Digital推出新SSD

Western Digital新推出WD Blue SN550 NVMe SSD,其速度比SATA SSD快上四倍。這款新SSD亦為主打效能的NVMe SSD,專為創作者和PC使用者設計,可更快速開機,且在讀取寫入方面效率大幅提升。

Western Digital推出新SSD供消費者彈性選擇。

Western Digital消費性SSD產品行銷總監翁祥文表示,有鑑於網路環境的升級,需要將產品於速度及耐用度上提升。因此改變元件散熱架構,以提升產品整體效能。

新產品考量目標客群需求設計,為PCIe介面的SSD,符合PCIe Gen3的規範,除改進散熱設計以最佳化讀取及寫入速度之外,亦考量到一般使用者的使用需求及成本。即便沒有安裝DRAM,產品表現仍比其他市面競爭產品加上DRAM的狀況還優良。針對值得關注的SSD散熱及降速問題,歷經攝氏55度高強度環境測試下,仍可有良好穩定的讀取及寫入速度。

Western Digital客戶業務部門副總裁兼總經理Eric Spanneut表示,新品採NVMe優先的作法大幅提升系統效能和速度,進而減少等待資料的時間。如此得以讓使用者工作更有效率。為將使用者需求轉為生產力,該公司推出本產品以解決多核心的需求。

綜觀現代創作者對資料儲存的需求強勁增長,無論是4K或8K影片檔案、大型文件尚需大量儲存空間的應用程式,作業環境皆需具可靠效能、耐寫度、高速及大容量,而NVMe介面可符合上述需求。無論工作、創作、遊戲或處理大量資料,新品速度都比SATA SSD快上四倍。隨著反應速度提升,對多工使用者和程式使用者而言,其整體電腦使反應將更快速及靈敏。

新品規格彈性落於介於PC跟企業級之間,意即不需高成本便可取得。Eric Spanneut進一步指出,對想使用NVMe產品的客戶而言,WD Blue SN550是理想選擇;對於系統建置商來說,新品將NVMe和SATA SSD系列布建更全面,提供高容量硬碟,因此建置商將有更多彈性打造符合不同客戶需求的系統。

2019英特爾重回半導體龍頭 索尼飛躍成長

市場調研機構IC Insights日前釋出研究報告,揭示英特爾(Intel)即便面對全球半導體市場的不樂觀,仍將超越三星(Samsung)重回全世界最大半導體供應商;而索尼(SONY)則以亮眼姿態躍升,於銷售成長率中稱冠。

英特爾在2019年全球半導體供應中排名第一,重回產業龍頭。

根據研究報告指出,2019年全球半導體產業整體銷售量不甚理想,與2018年相比估計減少13%,呈現下滑趨勢。報告中針對2019年全球半導體公司營業額進行排名,前15名排名依序為英特爾、三星、台積電、海力士(Hynix)、美光科技(Micron)、博通(Broadcom)、高通(Qualcomm)、德州儀器(TI)、鎧俠(Kioxia)、NVIDIA、索尼、意法半導體(ST)、英飛凌(Infineon)、恩智浦(NXP)及聯發科技。若扣除純晶圓代工廠台積電不計,海思(華為)將排名第15名。

全球排名前15名的半導體公司銷售額預計皆達70億美元,但於銷售量上呈現萎縮,估計比2018年減少15%,比全球估計銷售數值低兩個百分點。

進一步探究前15名,其中僅有三間:索尼、台積電和聯發科,銷售額呈現增長,其餘均呈現衰退,尤其是三大記憶體供應商:三星、海力士以及美光,銷售數字均預計比2018年下降超越29%。其中海力士跌幅最劇,銷售額下降38%。此外,包括記憶體供應商三星、海力士、美光和鎧俠在內,更有六家公司預計2019年銷售將出現兩位數的衰退。

索尼在全球半導體產業不景氣的情勢下,銷售率仍逆勢成長為全球第一。

至於報告中比較的全球半導體公司銷售成長率,上升最顯著的是索尼。歸功於影像感測器的熱銷,在一片負成長中交出超越2018年的好成績,一舉上升4名。相形之下,恩智浦預計將下跌兩名至第14名。

隨著三星於DRAM和NAND快閃記憶體市場的顯著成長,英特爾自2017年第二季便被三星取代久居的首位,連兩年追於其後。但由於2019年記憶體市場的銷售額預估將大幅萎縮34%,英特爾2019年銷售額將以26%的差距超越三星,再次成為全世界最大半導體供應商。

滿足資料儲存需求 DDR5頻寬/密度大增

對於許多的資料中心營運商來說,降低功耗都是他們的首當要務,以降低營運費用。而DDR5目標就是提供資料中心所需的增強效能以及功率管理功能,為400GE的網路速度提供良好支援。

新型的JEDEC DDR5將提供經過改善的效能,與上一代的DRAM技術相比,功率效率更高。DDR5將提供兩倍於DDR4的頻寬和密度,同時還改善了通道的效率。這些增強功能與針對伺服器和用戶端平台而提供的更加易用的介面結合到一起,將在一系列廣泛的應用中實現極高的效能並改進功率管理。

無論如何,一些主要的製造商很快即將發布他們的第一款DDR5記憶體模組,將更高的頻寬和更低的功耗推出市場。新模組將引入新一代的高速記憶體,從而取代現有的標準。

DDR5提高功率/效能

與DDR4技術相比,DDR5改善了效能並且提高了功率效率,因此,對緊湊而又穩健的DIMM插槽的需求比以往任何時候都要重要,以便為這種新技術提供支援。

例如莫仕(Molex)的DDR5 DIMM插槽比DDR4時代的產品更加緊湊,縮小整體尺寸與高度,此外還具有防屈曲功能,實現平穩的模組插入,並提供冠形的觸點以防止觸點斷裂。

DDR5 DIMM插槽的頻寬和密度比DDR4提升了一倍,可以提供6.4Gbps的速度,高度降低後的底座面可以節省更多的印刷電路板空間與豎向空間。DDR4和DDR5的針數保持相同,這兩種DIMM都含有288個插針;DDR4和DDR5的螺距也相同。除了增加速度以外,在整體尺寸和模組卡的厚度上存在著一些區別。

另外DDR5插槽連接器的尺寸要短於DDR4。對於模組卡的厚度來說,DDR4為1.40+/-0.1毫米,而DDR5將達到1.27+/-0.1毫米。至於底座面,將從DDR4的最大2.4毫米縮減為DDR5的2.0毫米最大值。

使用穩定連接器至關重要

當需要遷移到DDR5時,設計人員應當牢記幾個特定於插槽連接器的主要考慮因素。DDR5插槽採用了鍵控功能來防止插入DDR4模組,而且DDR4模組在DDR5中無法工作,反之亦然。

DDR5的確需要更高的速度。如果採用SMT端接,那麼在製程上可能會存在挑戰,與TH或PF端接方式相比或許更難以加工。CTE與印刷電路板的不符合會造成連接器的動態翹曲。隨著自動模組插入製程的到來,使用一種穩健的DDR5連接器就變得更加關鍵。DDR5插槽在插鎖塔上配備一片金屬,可以改善機械強度。

DDR5採用的模組卡更重一些,並且模組重量可能會從50克增至65克。因此,需要考慮採取良好的措施,以機械方式將連接器保持固定在印刷電路板上。

具防斷裂觸點連接器 確保電氣可靠性

在尋求推進到DDR5的過程中,需要牢記幾個方面。請考慮使用一種具有防斷裂觸點的連接器,可以實現穩健的配對接觸效果並確保電氣上的可靠性。耐高溫的無鹵尼龍外殼可以支援較高的回流溫度,同時提供環境上的可持續性。耐振動耐衝擊焊片在條件苛刻的作業過程中可提供最優的效能以及牢固的印刷電路板保持效果。此外,插槽上的金屬嵌件支援嚴格的閉鎖作業,同時可對插鎖塔進行強化。人體工學設計的穩健插鎖在閉鎖過程中以及模組卡釋放時可改善撕扯力以及抗振性。為了解決插針壓碎的問題,可以尋求使用設計良好的端子與外殼。

對於DDR5上的其他考慮事項,動態翹曲可能是一個需要關切的問題。在加工方面,與TH端接方式相比,SMT端接將更具挑戰性,並且更加困難。必須妥善的控制組立製程,同時設計與外殼材質的選取也極其重要。經最佳化的成型製程可以降低外殼內積聚起的內部應力。

隨著資料中心內的速度不斷提升,DDR5將成為一個理想的選取,為這種速度上的提升提供支援。DDR5插槽的生產正在穩步增長,並且將在下一年保持這一成長勢頭。為解決上述問題,有業者提供種類廣泛的記憶體連接器,符合有關雙列直插記憶體模組(DIMM)和單一內嵌記憶體模組(SIMM)的JEDEC產業標準要求,並且還為筆記型電腦、桌上型電腦、工作站、伺服器、儲存及通訊應用提供自訂的記憶體模組。

(本文作者為Molex產品經理)

三星再發全新12層3D-TSV封裝技術鞏固市場優勢

3D封裝技術再現新突破。三星(Samsung)近日宣布,該公司已經開發出業界首個12層三維矽穿孔(3D-TSV)封裝技術。3D-TSV技術(尤其是12層)被認為是現今大規模量產高性能晶片所面臨的巨大挑戰之一,因為需要極高的精度才能通過擁有60,000多個TSV孔、以3D封裝垂直互聯的12個DRAM晶片。

三星電子測試與系統封裝執行副總裁Hong-Joo Baek表示,隨著各種新時代的應用不斷興起,像是人工智慧(AI)、高性能運算(HPC)等,能提升記憶體性能的封裝技術變得越來越重要,也越來越複雜。同時,隨著摩爾定律的擴展逐漸達到極限,預計3D-TSV技術的效用在未來將更加重要與關鍵,而該公司希望在此一領域一直維持在領先地位。

據悉,12層3D-TSV封裝技術的厚度與當前8層第二代高頻寬顯示記憶體(HBM2)相同,這在元件設計上是一大進步,因對客戶而言意味著可行更高容量、更高性能的設計,而毋須大幅改變系統架構設計。此外,透過3D封裝技術,將可使晶片間的資料傳輸時間更明顯的縮短,在明顯提高資料傳輸速度的也降低功率損耗。

總而言之,依靠新研發的12層3D-TSV 技術,三星將可為資料密集、高速傳輸等應用提供效能更高的DRAM;而且,透過將堆疊層數從8個增加至12個,三星將能在很短的時間內大量生產24GB高頻寬記憶體(容量為目前是市場上8GB高頻記憶體的3倍)。另一方面,三星也希望憑藉12層3D-TSV技術,滿足快速成長的大容量HBM市場需求,並同時希望該公司在高階半導體/記憶體市場的競爭優勢。

三星研發12層3D-TSV封裝技術,再強化晶片效能。

中國自主DRAM之夢發芽 長鑫存儲量產在即

成立於2016年的中國長鑫存儲(Changxin Memory Technologies),先前稱合肥長鑫與福建晉華、長江存儲為「中國製造2025」的三大記憶體國家隊。該公司日前正式宣布,首款自主設計DRAM(動態隨機存取記憶體)晶片2019年底預計開始逐步量產,透過重新設計DRAM架構,盡量減少美國技術使用,同時首度公開談論其技術內涵,希望有效降低技術侵權疑慮。

中國長鑫存儲在合肥投資新台幣近2500億元,準備量產自主DRAM記憶體

據了解,長鑫在合肥DRAM廠已投資約80億美元,計畫在年底量產,最初每月預計生產約1萬片晶圓,相較目前全球每月生產130萬片晶圓,上述數字僅如滄海之一粟,但對還沒有本土自製DRAM晶片的中國來說,卻不啻是項重大突破。2018年全球DRAM市場規模達996.5億美元,三星電子、SK Hynix、美光等三大廠掌控了95%市場。

長鑫表示其DRAM設計來自德國晶片商英飛凌旗下2009年破產的DRAM廠奇夢達(Qimonda),長鑫存儲副總裁、未來技術評估實驗室負責人平爾萱表示,該公司已經把原本奇夢達的46奈米製程 DRAM提升到10奈米,也開始在極紫外光(EUV)、高介電常數金屬閘極(High-k Metal Gate, HKMG)和環繞閘極(Gate All Around, GAA)等新技術的研發。奇夢達曾提出埋入式電柵三極體技術,利用空間將三極體的性能提升,這種提升隨著線寬的減少越來越被需要。從堆疊式架構的發展歷史以及展望將來的發展趨勢就可以發現,現在DRAM沿用密集排布電容及埋入式電柵三極體,甚至未來3~5代DRAM應該都會延續類似架構。

DRAM是基於電容儲存電荷為原理的緊密鋪排的陣列,這個陣列透過一系列外圍電路管理以讀寫裡面儲存的資料。平爾萱說,與過往相比,今天一個面積小於指甲的DRAM晶片可容納80億儲存單元,而8個儲存單元可以代表一個字母,因此一個晶片可能儲存10億個字母。而這些數據可以6Gb/sec 的速度,在幾秒內完成讀寫。DRAM技術在發明之後的幾十年里,經歷了從早期簡單的平面結構,變化成為立體溝槽式電容及堆疊式電容的架構,為了爭取更多的電路表面積,演變出向上和向下兩種技術發展路線,而最終以堆疊式架構勝出。

原因是溝槽式架構面臨幾個技術瓶頸:其一是溝槽式只限於單面表面積,堆疊式可用雙面表面積,溝槽式架構很快就達到了刻蝕深寬比極限;其二是高介電質材料的應用受到溝槽式中高溫製程的限制。展望未來,平爾萱認為,DRAM是有極限的,透過技術改進,可以延後物理性能的限制,如導入 EUV微影技術及HKMG三極體以縮小線寬及加強外圍電路性能。EUV是繼193奈米 Immersion Scanner後又一個曝光技術革命,EUV主要是針對陣列,但外圍線路的增強及微縮也是近來DRAM技術發展的另一個機會。另外,由於DRAM製程中有電容這一段,因此HGMG製程的選擇需與電容製程匹配,透過導入HKMG,不但可以推動儲存密度進一步提高,連接埠速度也同步獲得了提升。

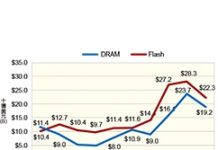

2019年記憶體產業資本支出總金額約416億美元

隨著記憶體廠擴展和升級的大浪潮即將結束,代工廠將在2019年占據大部分半導體資本支出比重。過去兩年,記憶體的資本支出是推動整個半導體產業資本支出大幅成長的因素。這些升級和擴廠計劃中的大多數已完成或已進入其最終建設階段。因此,預計記憶體資本支出將占今年半導體行業資本支出總額的43%,低於2018年的49%。繼2018年創下1,059億美元的紀錄之後,預計2019年半導體資本總支出將下滑8%至978億美元。

七年來,記憶體設備資本支出的比重大幅增加,從2013年的27%(147億美元)成長到2018年創紀錄的49%(520億美元)紀錄,2019年資本支出約416億美元,2013~2019年的年複合成長率為18.9%。2017年和2018年支出最大的IC產品是Flash記憶體/非揮發性記憶體類別,三星、SK海力士和美光三家大廠DRAM和NAND記憶體都積極投資,而英特爾、東芝Memory、Western Digital、SanDisk和XMC、Yangtze River Storage Technology在過去18個月中均大幅提高了3D NAND快閃記憶體容量, DRAM和NAND記憶體市場已進入產能過剩和價格疲軟的時期。 DRAM和NAND快閃記憶體的每位元價格急劇下跌,以及對2019年的資本支出大幅削減可以證明。

在2019年,預計DRAM和Flash的資本支出將分別衰退19%和21%。預計2019年記憶體資本支出為416億美元,比2018年減少104億美元。今年DRAM和快閃記憶體市場的支出大幅削減,是記憶體廠商試圖防止在2019年下半年和2020年價格持續下跌的原因。

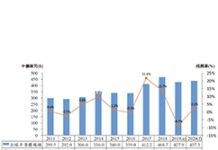

MIC:2019年全球半導體產值衰退8.7% 2020年後緩步回升

全球半導體產業,歷經2017與2018年,由記憶體市場需求井噴帶動的連續兩年兩位數成長的榮景宣告結束,2019年產業全面修正,根據半導體貿易統計群組織(WSTS)與資策會MIC的預測,2019年全球半導體產業產值為4279億美元,較2018年衰退8.7%,2020年將成長至4373億美元,成長2.2%,呈現緩步回升的態勢。

2017年線上高畫質影音帶動資料中心(Data Center)的大幅成長,記憶體需求包括DRAM與NAND Flash跟著水漲船高,缺貨情況湧現也推升記憶體價格,全球主要記憶體廠業績倍數成長;其後又有許多充滿話題的新興科技如人工智慧(AI)、區塊鏈、自駕車、虛擬貨幣、5G等,持續帶動產業需求,造就半導體產業連續兩年兩位數成長的榮景,2017年產業成長率達21.6%,2018年在高基期環境下再度成長13.7%。

不過,熱絡的情況2019年急速降溫,上半年記憶體需求不再激情,DRAM與NAND Flash價格大幅滑落,再加上美中貿易戰影響,終端庫存過高,也拖累全年半導體產業的整體表現。資策會MIC預估,經濟成長趨緩等因素將延續到2020年,終端消費者的消費意願因經濟情勢不確定而下滑,使得廠商下單趨於保守,訂單能見度低,將影響2020年半導體產業整體表現,展望未來,產業將呈現緩步復甦,2020年成長2.2%,2021年以後產業規模預期可以恢復到2018年的水準。

美光開始量產採用1z奈米技術節DRAM

美光科技宣布DRAM擴充的進展,成為首家開始使用1z nm製程技術量產16Gb DDR4產品的記憶體公司。

美光科技技術開發執行副總裁Scott DeBoer表示,現今擴充DRAM條件變得更加複雜,開發和量產業界最小尺寸的DRAM節點展現了美光世界級的工程和製造能力。率先進入市場讓美光擁有競爭優勢,我們將繼續為廣泛的終端客戶應用提供高價值解決方案。

與上一代1y nm節點相比,美光的1z nm 16Gb DDR4產品顯著提高位元密度、大幅增進效能並降低成本。同時,它也促進美光持續改善其運算DRAM(DDR4)、行動DRAM(LPDDR4)和圖形DRAM(GDDR6)產品系列的相對效能和功耗。對於包括人工智慧、自動駕駛車輛、5G、行動裝置、圖形、遊戲、網路基礎設施和伺服器等應用而言,功率和效能之間的優化平衡是關鍵的差異化因素。

美光透過量產16Gb DDR4記憶體解決方案,開始將技術移轉至1z nm。使用更小的節點進行生產帶來多項優勢,包括功耗較上一代8Gb DDR4產品降低約 40%。美光全面的1z nm DDR4產品組合也滿足資料中心對更高效能、更高容量和更低功耗,日益增長的需求。

此外,美光也宣佈公司已開始批量出貨基於UFS規範多晶片封裝(uMCP4)的業界最高容量單片16Gb低功率雙倍資料速率4X (LPDDR4X)DRAM。美光的1z nm LPDDR4X和uMCP4滿足了行動裝置製造商尋求更低功率和更小封裝,以設計具有吸引人的規格尺寸和長電池壽命的裝置需求。