CoWoS

新思科技攜手台積電 推出3DIC Compiler平台

新思科技日前宣布與台積公司合作,雙方採用新思科技Compiler產品的先進封裝解決方案,提供通過驗證的設計流程,可用於以矽晶中介層(Silicon Interposer)為基礎的基板上晶圓晶片封裝(Chip-on-Wafer-on-Substrate, CoWoS-S)以及高密度晶圓級且以RDL為基礎的整合扇出型封裝(Integrated Fan-Out ,InFO-R)設計。3DIC Compiler針對現今複雜多晶片(Multi-die)系統所需的封裝設計提供的解決方案,可用於高效能運算(High-performance Computing, HPC)、汽車和行動等應用。

3DIC Compiler平台可縮短封裝時間

台積公司設計建構管理處資深處長Suk Lee表示,AI和5G網路等應用對於較高水平整合、較低功耗、較小尺寸以及更快生產速度的需求日益增加,帶動了先進封裝技術的需求。台積公司創新的3DIC技術如CoWoS和InFO等,讓客戶能透過更強大的功能性和增強的系統效能,以更具競爭力的成本實現創新。我們與新思科技的合作為客戶提供了通過認證的解決方案,進而基於台積公司的 CoWoS和 InFO 封裝技術進行設計,以實現高生產力及加速完成功能性矽晶片。

新思科技設計事業群系統解決方案資深副總裁Charles Matar認為,對於想要利用多晶片解決方案設計出新一代產品的客戶,新思科技與台積公司深知其所面臨的設計挑戰,而我們雙方的合作正提供客戶一個最佳的實作途徑。透過在單一的完整平台上提供原生實現(Natively Implemented)矽中介層和扇出型佈局(Fan-out Layouts)、物理驗證(Physical Verification)、協同模擬(Co-simulation)和分析功能,讓客戶得以因應現今複雜的架構和封裝要求,還能提高生產力並縮短周轉時間(Turnaround Time)。

新思科技3DIC Compiler解決方案提供晶片封裝協同設計和分析環境,可在封裝設計出最佳的2.5D/3D多晶片系統。該解決方案包含了台積公司設計巨集(Design Macro)的支援和以高密度中介層(Interposer)為基礎、使用CoWoS技術之導線(Interconnect)的自動繞線(Auto-routing)等功能。針對以RDL為基礎的InFO 設計,則透過自動化的DRC感知之全角度多層訊號和電源/接地繞線(Power/Ground routing)、電源/接地平面設計和虛擬金屬填充(Dummy Metal Insertion),以及對台積公司設計巨集的支援,能將時程從數個月縮短至數周。

對CoWoS-S和InFO-R設計來說,晶粒(Die)分析需要在封裝環境和整個系統下進行。就設計驗證和簽核而言,晶粒感知(Die-aware)封裝和封裝感知(Package-aware)晶粒電源完整性(Power Integrity)、訊號完整性和熱分析(Thermal Analysis)皆非常重要。新思科技的3DIC Compiler整合了安矽思(Ansys)晶片封裝協同分析解決方案RedHawk系列產品,能滿足此關鍵需求,實現無縫分析(Seamless Analysis)且能更快速聚合成最佳解決方案。此外,客戶可藉由消除過度設計來實現更小的設計以及達到更高的效能。

推進摩爾定律 半導體先進封裝領風騷

半導體效能的提升與「摩爾定律」多年來幾乎成為同義詞,過去製程微縮是達成每兩年同樣單位面積中,塞入兩倍電晶體最主要的手段,然而製程微縮在近年也碰到物理極限瓶頸的挑戰,如何持續透過技術的演進改善積體電路的效能,成為半導體產業最重要的任務,「先進封裝」成為最近幾年提升晶片效能的重要技術,相關技術受市場重視程度也水漲船高。

半導體線寬/線徑的微縮遭遇技術挑戰,晶片或裸晶的整合成為推升半導體效能的另外一個手段,立體堆疊與異質整合(Heterogeneous Integration)則是封測技術發展的核心要項。透過封裝技術整合晶片與製程微縮是不同層面的積體電路整合,但目的同樣都是為了提升電晶體的集積度,從早期的系統級封裝(System in Package, SiP)到晶圓級封裝、3D堆疊等同質整合(Homogeneous Integration)技術,到近期代表性的異質整合概念小晶片(Chiplet)設計帶動的封裝發展都具有高度潛力。

先進封裝成長動能強勁

先進封裝包含覆晶封裝、晶圓級扇入扇出型封裝及內埋式封裝等。根據產業研究機構Yole D'eveloppement研究指出,2018~2024年先進封測產值之年複合成長率(CAGR)高達8.2%,相較非先進封測技術產值CAGR約2.4%,與整體封測業產值成長率約5%,成長動能相對突出,且2024年先進封測產值與其他產值比重將進一步縮小。

隨著電子終端產品朝向低價格、多功能、高效能、高整合度發展,未來幾年5G與AI將引領科技應用發展的腳步,而半導體晶片製程走到3~5奈米,終端產品也要微型化與高度整合的晶片協助,須使用晶圓級封裝(Wafer Level Package, WLP)技術,如2.5D/3D IC、扇出型封裝(Fan-out Package)等,因應用領域或晶片類型不同會採用不同的技術,工研院產科國際所產業分析師楊啟鑫表示,主要目的就是提升效能與降低成本。

扇出型晶圓級封裝(Fan-out Wafer Level Packaging, FOWLP)技術與採用TSV的正統3D IC相較,概念接近2.5D IC,且成本可低於TSV 3D IC,因而逐漸受市場青睞。而在市場需求部分,扇出型封裝晶片具備薄型化與低功耗之優勢,故在產品應用上以可攜式裝置為大宗,預計2021年將消耗363萬片12吋晶圓,相較於2014年台積電推出InFO封裝時之33萬片12吋晶圓消耗量,已大幅成長約11倍。

而扇出型封裝若要能持續降低製作成本以增加應用,擴大製程基板的使用面積是最重要的手段,以12吋(300mm)晶圓來看,其可使用面積僅約為3.5代(620mm×750mm)玻璃基板的15%,突顯玻璃基板在面積上的優勢。相較於晶圓級扇出型封裝技術,投入面板級扇出型封裝若能建立足夠的良率,將可以大幅降低成本,所以面板級扇出型封裝成為封測大廠2020年的發展重點,楊啟鑫指出,面板級扇出型封裝分為先晶片(Chip First)與後晶片(Chip Last)技術類型,各廠也有自己的發展重點。

面板級扇出型封裝成兵家必爭之地

先晶片技術的優勢在於不需凸塊(Bumping)製程成本較低,缺點為若低良率發生時將導致晶片損壞;後晶片的優勢在於可以製作高階晶片,大型且具高密度接腳,缺點為需花費凸塊製程費用導致成本較高。關於主要封裝廠的動態,楊啟鑫說明,日月光積極布局扇出型封裝技術,除了自行開發之外,也與英飛凌(Infineon)及DECA的M-Series技術合作及授權,其他系列技術還包括:eWLB、FOCoS、FOPoP、FOSIP、HD FOCoS、Panel FO等。

另外,全球記憶體封測第一大廠力成,近年積極發展邏輯IC封測,從中低階邏輯IC封測跨入高階面板級扇出型封裝技術,開發各種型態的扇出型封裝技術,符合不同IC的應用需求(圖1)。在低成本部分有不需凸塊的Bump...

Mentor IC設計平台通過台積電製程技術認證

Mentor近期宣布,該公司的多項IC設計工具已獲得台積電的N5和N6製程技術認證。此外,Mentor與台積電的合作關係已擴展到先進封裝技術,可進一步利用Mentor Calibre平台的3DSTACK封裝技術來支援台積電的先進封裝平台。

台積電的N5和N6製程技術可協助許多全球領先的IC設計公司提高處理器效能、縮小尺寸並降低功耗,以應對汽車、物聯網、高效能運算、5G行動/基礎設施、人工智慧等領域激烈的市場競爭。

Mentor的IC部門執行副總裁Joe Sawicki表示,Mentor與台積電長期合作並且擁有豐碩的成果,如此緊密的夥伴關係將持續協助共同客戶開發出高度創新和差異化的IC。很高興Mentor設計平台能夠獲得台積電最新的半導體製程技術認證,雙方的夥伴關係得到了更進一步擴展。

最近通過台積電N5和N6製程認證的Mentor IC設計技術包括Calibre nmPlatform,它是IC實體驗證領域的工具。Calibre可為全球成功的晶片製造商和IC設計人員提供出色的效能、準確度和可靠性驗證方案;Calibre xACT抽取工具─Calibre nmPlatform中的組成元件,可提供強大的寄生參數抽取功能和高準確度的數據,以供布局後分析和模擬之用;Mentor的Analog FastSPICE(AFS)平台─可為奈米類比、射頻(RF)、混合訊號、記憶體和客制化數位電路提供先進的電路驗證。

除了獲得這些認證,Mentor亦宣布,其AFS平台現在可支援台積電的行動裝置和高效能運算(HPC)設計平台。此認證可協助為HPC應用提供類比、混合訊號和射頻(RF)設計的Mentor客戶,使用台積電的最新製程技術充滿信心地進行晶片驗證。Mentor還同時宣布將與台積電合作,進一步利用Calibre的3DSTACK封裝工具來支援台積電的CoWoS封裝技術。該技術採用矽中介層作為晶粒間端口連接檢查的解決方案,Calibre xACT可用來提供寄生參數抽取。

台積電設計建構行銷事業處資深處長Suk Lee表示,作爲台積電重要的合作夥伴,Mentor持續提供豐富多樣的設計工具和平台,以支援台積電最先進的製程技術。期待與Mentor繼續共同努力,透過電子設計自動化 (EDA) 工具協助雙方的共同客戶運用5奈米製程這樣的TSMC領先技術提升晶片功率和效能,運用先進的EDA工具成功實現晶片設計。

應用範圍擴展/效能指標躍進 5G測試/驗證十八般武藝齊備

2020年伊始,台灣的5G頻譜競標結果初步揭曉,全球各個國家與地區也將投入更多5G商轉活動,5G進入高速發展階段,相關裝置預計將大舉出籠,包括網路基礎建設、聯網設備、行動終端與聯網節點等,根據產業分析機構研究指出,2025年5G裝置年出貨量將突破10億台。5G網路速率更快、使用頻段更高、連結規模更大、網路延遲更低、聯網可靠性更高,技術規格全面提升,使得產品設計難度大幅提高,如何達成效能目標,除了從晶片、架構、系統設計等層面提升之外,更需要透過良好的產品測試、驗證協助達成5G的技術目標。

5G技術規格與前代技術4G LTE相較,產品測試驗證帶來諸多挑戰,如量測準確度,由於5G使用頻段更高,天線校準與準確度、治具設備容錯範圍與訊號反射等,產生量測不確定性;且測試計畫複雜,須將量測作業整合至裝置測試計畫中,進行電波暗室整合、波束特性等驗證;再者測試時間延長,因為5G使用頻段更寬廣,每個使用到的頻段都需進行驗證,導致測試計畫複雜度大為提升,校準與量測的時間更長。

5G測試驗證複雜度大幅提高

由於5G技術革新幅度更甚於4G,加上5G應用領域廣泛,可以說是未來10年全球網路的基礎架構,重要的是5G網路規模將是4G的數十倍,多樣化的應用帶動網路架構持續成長,從技術架構來觀察,5G為因應三大應用情境,採用高度彈性的底層技術,透過網路切片(Network Slicing)與軟體定義網路(Software Defined Networking, SDN)和網路功能虛擬化(Network Function Virtualization, NFV)來達成差異頗大的各式網路應用需求,透過這些技術自由組合各種應用需要的功能,造成數以萬計的網路型態,測試驗證複雜度可見一斑。

另外,5G網路在技術指標的要求上,並未因網路複雜度而有所放鬆,三大技術指標傳輸速率最高達20Gbps,每平方公里聯結數量達100萬,網路延遲1毫秒(ms),就現有技術水準而言都不是簡單任務,包括網路架構、晶片、系統等設計都需升級,甚至材料也需大幅革新。5G技術與產品驗證涵蓋的範圍也非常廣泛,本文僅從晶片設計測試、半導體測試設備、訊號測試儀器等面向進行探討,期能一窺5G測試驗證的概況。

5G效能需求搭配先進構裝技術

IC設計高度集積化的發展從未停止,從過去電路線寬微縮發展到系統級封裝與近年的異質整合,5G對於效能的要求使得晶片需要採用先進製程,宜特科技可靠度工程室副總經理曾劭鈞(圖1)表示,5G晶片主要分成需要輕薄短小且省電的行動終端晶片與強調效能的基地台/雲端設備高速運算晶片。行動裝置在效能提升之下仍以追求輕薄短小的封裝型式為主,手機應用處理器(AP)以晶圓級晶片尺寸封裝(Wafer Level Chip Scale Package, WLCSP)延伸出的扇出型(Fan-out)及Fan out POP(Package on Package)封裝型式為主。

圖1 宜特科技可靠度工程室副總經理曾劭鈞表示,2.5D IC是讓不同製程的裸晶,採取平行緊密排列,放置在矽基板的中介層上。

另外,5G將高頻毫米波頻段導入商用,使得5G訊號從1GHz以下,延伸到超過30GHz,曾劭鈞認為,5G帶動更多天線的需求在天線數量激增但可用面積維持不變的情況,射頻前端的AiP(Antenna in Package)封裝型式則成為目前廠商的最佳解決方案,而AiP主要採SiP(System in Package)或PoP的結構來縮小天線體積。

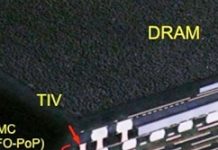

而在雲端/基地台裝置的部分,曾劭鈞提到,5G的基地台要處裡更龐大的資料量,目前廠商採用先進的2.5D/3D封裝來提升訊號傳遞速度/品質,以Silicon die如CoWoS的矽中介層(Silicon...

2024年先進封裝產業規模將達440億美元

先進封裝製程是當今所有半導體製造技術的核心。對所有半導體公司而言,先進封裝技術在由 5G、人工智慧和物聯網等大趨勢直接影響的產業發展方面具有戰略意義,並能確保其業務的發展。產業研究機構Yole Développement(Yole)表示,2024年先進封裝市場規模為440億美元,2018~2024年的年複合成長率為7.9%。

2018~2024年主要先進封裝製程成長趨勢 資料來源:Yole Développement(12/2020)

面對不斷變化的目標及大趨勢的影響,半導體廠商正在調整各自戰略。而半導體供應鏈及其背後的先進封裝產業也在經歷著不同層次的變革。部分廠商已經成功涉足新的商業領域,顯著影響IC產業鏈,而其他廠商則未成功。不同的廠商有不同的驅動因素轉型或拓展新業務—例如谷歌、微軟、Facebook和阿里巴巴這些軟體公司正在設計自己的處理器,以便在組裝層面獲得系統級整合/定制和供應鏈控制。

最大的變化是代工廠涉足先進封裝業務。儘管他們是該領域的新進者,但帶來的影響是顯著的:台積電在扇出型和3D先進封裝平台方面領先,提供各種產品,如InFO(及其變種)、CoWoS、WoW、3D SoIC 等。對於台積電來說,先進封裝已經成為一項成熟的業務,預計2019年其先進封裝業務的營收將達30億美元,在OSATs中排名第四。

聯電是2.5D封裝矽轉接板的主要供應商。聯電最近與Xperi合作,為各種半導體元件優化並商業化ZiBond和DBI技術。武漢新芯為影像感測器和高性能應用提供3D IC TSV封裝方案。整體而言,這些廠商有助於將封裝從基板轉移到矽平臺。其實,不止代工廠進入先進封裝領域,IC基板和PCB製造商,如SEMCO、Unimicron、AT&S和Shinko,透過板級扇出封裝和有機基板中的嵌入式晶片涉足先進封裝領域。這些公司正在瓜分OSAT的市場,特別是先進封裝業務。

迎向Chiplet新時代 先進封裝模糊前後段界線

在AI浪潮席捲下,為了提供更高的運算效能,處理器核心數量,以及其所搭配的快取記憶體容量、I/O數量都呈現指數型暴增。這些情況使得IC設計者即便使用最先進製程,也很難把晶片尺寸變得更小。

不僅如此,如果按照傳統設計方法,晶片面積還越來越大,在某些極端狀況下,甚至還出現一片12吋晶圓只能生產十多顆,甚至不到十顆晶片的情況。如果再把良率因素考慮進去,採用這種設計方法製造出來的晶片,單顆成本恐將突破新台幣100萬元。這顯然不是晶片設計者跟客戶能夠接受的。

另一方面,5G對高頻寬、低延遲與大量連線的要求,使得通訊晶片必須要有更高的整合度,才能夠滿足5G提出的效能標準。同時再加上絕大多數物聯網裝置都有嚴格的成本、功耗與外觀尺寸限制,通訊晶片業者如果不想辦法利用先進封裝技術,把更多通訊元件、甚至天線整合在單一封裝內,形成完整的微型通訊模組,將難以滿足應用市場需求。

同質/異質整合攜手 共同因應AI與5G挑戰

AI跟5G正好代表兩種看似截然不同,但其實殊途同歸的半導體產業發展方向--同質整合(Homogeneous Integration)與異質整合(Heterogeneous Integration)。而且在許多情況下,這兩種整合其實是同時並存的。

針對同質整合,台積電研發副總經理余振華(圖1)表示,不管是依循摩爾定律(Moore's Law)的道路進行製程微縮,抑或是採用先進封裝技術,把不同晶片整合在同一個封裝體內,客戶追求的目標永遠都一樣--用更低的成本來實現電路功能。因此,除了製程微縮之外,如果有其他技術選項可以達成這個目標,客戶當然會樂於採用。而同質整合跟異質整合之所以興起,就是因為這兩種先進封裝技術,能夠有效降低成本。

圖1 台積電研發副總經理余振華表示,為協助客戶降低晶片生產成本,同質/異質整合並用將是未來的發展方向。

同質整合通常應用在處理器或邏輯晶片上,這類晶片為了提供更高的效能,滿足AI運算需求,不僅核心數量越來越多,核心旁邊配置的快取記憶體容量也跟著變大,I/O的需求也跟著暴增。如果繼續採用傳統SoC的設計思維,不把這類大型晶片切割成多顆小晶片,再用先進封裝技術整合起來,其生產良率會受到極大影響。

另一方面,把SoC按照功能進行切割,也有助於實現IP重複利用,並且讓設計最佳化。一顆SoC裡面,其實有很多電路不適合用最先進的製程技術生產,例如記憶體、I/O跟其他與類比/混合訊號有關的功能電路。與其將所有功能都整合在一顆晶片上,把這些電路功能切割開來,用性價比更高的製程來生產,反而更具經濟效益。這個觀念就是所謂的異質整合。

同質整合搭配異質整合的案例很多,台積電也已經有許多客戶成功開發出這種採用混和架構的產品,例如賽靈思(Xilinx)的高階FPGA,一方面使用同質整合,把一顆大型晶片切割成多顆小晶片,再利用CoWoS整合;另一方面,該公司的FPGA旁,還有多顆HBM記憶體,同樣利用CoWoS進行整合,以獲得更大的記憶體頻寬。

不過,由於CoWoS的成本高昂,在很多情況下已超過客戶可接受的門檻,因此成本相對低廉,但效能較低的InFO,獲得更廣大的客戶群青睞。此外,InFO的結構還在持續進化,且目前台積電InFO的線寬/間距(L/S)已經可以做到2/2微米;在實驗室裡面,甚至已發展出1/1微米以下的技術,且層數還在持續往上疊加,因此InFO家族的性能正在逐漸逼近CoWoS,也開始有網通晶片廠開始使用InFO。

至於在CoWoS方面,由於矽中介層(Si-interposer)的成本偏高,因此台積電3DIC處長鄭心圃透露,該公司內部也在發展以有機材料取代矽中介層的CoWoS,盼藉此提供客戶更多選擇。

除了成本考量外,從技術角度來看,IC設計者未來在開發新晶片時,也必然要導入同質/異質整合。聯發科副處長邱寶成(圖2)就指出,雖然先進製程可以做出更小的電晶體,但功率密度並未跟著電晶體縮小而下降。

圖2 聯發科副處長邱寶成認為,藉由先進封裝實現同質/異質整合,可有效協助設計者降低晶片的功率密度。

以聯發科目前功率密度最高的晶片為例,其功率密度可達380W/平方公分。用電熨斗做為比較生活化的比較基準,大家都知道電熨斗很燙,但其實電熨斗的功率密度只有10W/平方公分,由此可見功率密度對晶片設計者帶來的挑戰是多麼艱鉅。

把晶片設計適當分割開來,不只可帶來良率提高,成本下降的經濟效益,對於降低功率密度也有幫助。不過,由於AI、5G應用對晶片效能跟I/O數量的需求很大,IC設計者不希望在這方面有所妥協,因此聯發科非常樂見各種更先進的互連封裝技術出現,讓晶片設計者可以有更多選擇空間。

L/S迅速微縮 封裝難度/可靠度挑戰大增

其實,把時間往回推一年,在2018年的系統級封測高峰論壇上,除了CoWoS之外,業界能提供的扇出(FO)封裝技術,L/S大多還只能做到10/10微米,但一年之後,2/2微米已經成為新的標準,而且RDL的層數已經迅速推進到4P5M(四層有機聚合物,五層金屬層)。由此可見晶片客戶跟半導體製造業者對先進封裝技術的強烈需求。

然而,更細的互連線路、更多層數的立體堆疊,不僅需要新的材料跟製程設備,也使得封裝的生產良率、可靠度面臨更嚴苛的挑戰。有鑑於此,材料、設備商紛紛推出新一代材料或製程設備機台,如Atotech、Brewer Science、EV Group、K&S、Lam Research、SPTS、Smoltek、SÜSS MicroTec、千住金屬(SMIC)等。這些廠商提供的解決方案,讓台積電、日月光、力成跟艾克爾(Amkor)等前後段業者得以將先進封裝推向量產。

而在確保生產良率跟封裝可靠度方面,檢測(Inspection)與計量(Metrology)廠商如Camtek、Cyberoptics等,也針對各種先進封裝推出新的解決方案。事實上,由於先進封裝興起的緣故,檢測與計量在封裝領域所扮演的角色,將比過去更為關鍵。

由於先進封裝涉及多晶片整合,如果半導體製造商沒有在封裝前先對個別晶片進行完整檢測,鎖定Known Good Die(KGD),再進行Die to Wafer(D2W)或Chip to Wafer(C2W)整合,將會把Bad Die跟其他Good Die封在一起,最後得到無法正常運作的元件,並蒙受巨大的經濟跟良率損失。由此可知,檢測與計量在後段製程的重要性將越來越高,而這也會使封裝廠的產線設計跟運作流程變得越來越像前段廠。

從SoC走向Chiplet EDA工具支援至關重要

除了材料跟設備機台外,由於先進封裝變得越來越複雜,因此封裝設計者很難再用現有的設計工具來完成先進封裝設計。明導(Mentor)亞太區技術總監李立基(圖3)就指出,在一個封裝只有幾百個I/O的時代,封裝設計者還有可能用試算表(Spreadsheet)來規畫I/O,但在動輒數千甚至上萬個I/O互連的先進封裝設計中,這種方法不僅太耗時,而且出錯的機率很高。基於資料庫的互連設計,還有設計規則檢查(DRC),都將成為先進封裝設計的標準工具。此外,以往封裝業界習慣使用的Gerber檔格式,在先進封裝時代也必須改成GDSII檔格式。整體來說,封裝業界所使用的工具,都會變得越來越像前段Fab跟IC設計者所使用的工具。

圖3 明導亞太區技術總監李立基認為,未來後段封裝設計的EDA工具,將越來越接近前段IC設計用的EDA工具。

另一方面,在晶片設計端,為了把SoC拆解成Chiplet,EDA工具也必須跟著大翻新。而且不僅是RDL Netlist、線路布局(Place & Route)的工具需要更新,設計人員還需要更多設計模擬工具來解決多晶片所衍生的電源一致性(PI)、訊號一致性(SI)、電磁相容(EMC)、散熱(Thermal)等問題。新思(Synopsys)、益華(Cadence)與明導都有對應的解決方案。