資料中心

英特爾積極投入 100G Ethernet有望加速普及

因應雲端、伺服器和資料中心等高速傳輸與運算需求,英特爾(Intel)積極推動100G乙太網路(Ethernet)布建,100G Ethernet普及率可望大幅加快。英特爾業務暨行銷事業群商用業務總監Alex Cheng表示,英特爾在資料中心市場擁有95%以上的生態系(包含運算、儲存到網路等),憑藉此一優勢,當英特爾開始進入100G Ethernet市場之後,整個資料中心產業的上、下游,便會因而加快100G Ethernet的布建速度。

據悉,為了推動100G Ethernet建置,英特爾在不久前發布Intel乙太網路800 系列控制器與轉接器,並預計於2019年第三季開始量產。英特爾指出,新的乙太網路系列增添了各種突破性的功能,包括應用裝置佇列(ADQ),其可提高應用效能和滿足服務層級協議(SLA)的一致性。

ADQ可讓應用程式運作開放原始碼的Redis(一種雲端服務供應商中廣泛使用的資料庫)時,回應時間可預測性提升50%以上,延遲性降低45%以上,吞吐量則提高30%以上。

除此之外,其他進階功能包括增強的動態設備個人化(DDP),以提高封包處理效率和啟用新服務,並透過iWARP和RoCE v2遠端直接記憶體存取(RDMA)的支援以更快地處理對延遲高度敏感性的工作負載。

Alex Cheng說明,目前資料中心以10G Ethernet最為普及,100G Ethernet被認為是小眾市場。然而,物聯網、AI的興起,為能有更快的傳輸、運算效率,使用高速網路連接雲端的時代已然來臨;而英特爾在資料中心的建置,不僅著重運算、儲存,也特別關注網路。因此,便決定積極投入100G Ethernet的建置,透過新推出的800系列和自身的生態系優勢,將能使100G Ethernet的建置更順利,使各資料中心及早進入100G Ethernet時代。

加強資料中心/高速互連優勢 NVIDIA斥資69億美元收購Mellanox

為搶占資料中心市場,拓展業務範圍,NVIDIA斥資69億美元收購邁倫科技(Mellanox)。此收購案將結合NVIDIA的運算平台和Mellanox的互連技術,NVIDIA將能最佳化資料中心規模的運算負載量,提供全球前500大超級電腦中超過250台的互連能力,滿足雲端服務供應商與電腦製造商對於高速運算、互連的需求。

NVIDIA創辦人暨執行長黃仁勳表示,人工智慧、資料科學及數十億同時出現的電腦用戶都在急劇加速對全球資料中心的需求。為了滿足這樣的需求,將需要能夠透過智慧網路結構來大量連接快速計算節點的整體架構,以形成一個巨大的資料中心規模的運算引擎。

根據此協議,NVIDIA 將以每股125美元現金收購Mellanox所有已發行普通股,交易金額約為69億美元。此項交易案已獲得兩間公司的董事會同意,並預計將在2019年年底前完成。

現今在人工智慧、科學運算和數據分析的資料與運算強度正以倍數成長,大規模和企業資料中心對高效運算、互連的需求越來越多;但CPU的效能進展隨著摩爾定律的結束而放緩,驅使GPU和智慧連網解決方案應用大增。

可想而知,未來的資料中心將被建構為具有數萬個運算節點的巨型運算引擎,且將整體設計可彼此互連以獲得最佳效能;而Mellanox主要發展高速互連解決方案,其InfiniBand互連技術與高速Ethernet方案目前已被用於全球超過半數最快的超級電腦,以及許多超大規模資料中心。

收購Mellanox後,NVIDIA將能最佳化資料中心規模的運算負載量,可囊括所有運算、網絡和儲存堆疊,為客戶達到更高效能、更高的利用率與更低的營運成本。

資料中心內部介面大提速 PCIe Gen4測試步步為營

在資料中心內部,各種設備/裝置使用Ethernet100G/200G/400GbE作為外部連結介面,PCIe則是被廣泛用作內部數據傳輸的介面。PCIe主要做為電腦系統內部的通用傳輸介面。剛開始PCIe Gen1傳輸速率為2.5GTps,可相容PCI介面,隨著傳輸需求的發展PCIe Gen2的速度為5GTps,PCIe Gen3的速度為8GTps;目前PCI SIG最新的規格PCIe Gen4速率提升到16GTps。此外,PCIe Gen5傳輸速率預計提升到32GTps,PCI-SIG正在制定相關的規格。

PCIe Gen4傳輸速率高達16GTps,不僅僅是使用在一般的電腦裝置中,更是被廣泛地運用到各種設備的內部傳輸介面,例如傳輸設備、伺服器、儲存裝置等。

傳輸速率越高,訊號的傳輸衰減越大,使得從訊號發射端(Tx)到接收端(Rx)傳輸過程所產生的衰減也跟著增加,過大的衰減將導致訊號劣化,使得接收端無法做訊號判別接收。也因此,PCIe Gen4的Tx和Rx端均使用了等化器(Equalization),以補償高速訊號傳輸的衰減,接收端的誤碼率(BER)測試驗證是必要的。

Link EQ為Gen3/Gen4測試新需求

PCIe裝置在連接時,會進行LinkEQ溝通,將TRx EQ做最佳化設定,如此一來也使得Tx和Rx間的Link Equalization(Link EQ)成為PCIe Gen3/Gen4 TxRx新測試需求。接收端測試設備誤碼儀(BERTs)這時候須具備Protocol溝通能力,在執行TRx LinkEQ測試時,扮演與待測物溝通的角色,讓待測物與儀器進行溝通設定好最佳TRx EQ後,進行後續誤碼(BER)驗證(圖1)。

圖1 Anritsu MP1900A PCIe Rx測試架構

隨著各種傳輸介面如TBT3、USB、PCIe傳輸速率越來越快,接收測試變成是必須的驗證項目。工程師須藉由誤碼儀提供協會規範的Stress訊號來進行接收端品質驗證。而Rx LinkEQ壓力測試在PCIe Gen3後變成是Certification必要項目。在整個測試流程中包含的訊號校正(Calibration),Link Training與BER測試。

PCIe裝置主要分為兩種類型:System(或Root Complex),如作為主設備的CPU和主機板;以及作為連接到主設備的附加裝置AIC(Add-in...

資料中心傳輸需求大增 高速光收發器模組需求起飛

近幾年,由於線上遊戲、隨選視訊、社群網路、雲端計算等需要大頻寬需求的應用不斷的推陳出新,讓全球網路的流量呈現爆炸性的成長。另外,為了支援雲端服務、高速運算等高網路流量的應用,資料中心(Data Center)建置的數量與規模也有非常明顯的成長。

根據Cisco的報告指出,在2015年資料中心的傳輸總流量約為4.7 Zetabytes,並預估到2020年將達到15.3 Zetabytes,將有超過三倍的成長。資料中心的訊息傳輸約有70%流量是發生在資料中心內部的傳輸,約有15%的流量是發生在資料中心之間的傳輸。由此可知大部分的傳輸流量是出現在資料中心內部,所以資料中心內部需要提高資料傳輸速率,同時還需要能夠具備低成本與低功率消耗的特性,而光訊號傳輸是目前唯一可以滿足這些需求的技術。因此,未來在資料中心內部的高速光收發器模組,也將持續有大量的需求;而且光收發器模組的技術發展,也將持續提高傳輸速率。

400G光收發器將成主流

為了實現高速光訊號傳輸,高速小型光收發器模組的開發是其中的關鍵技術,目前資料中心以40Gbps與100Gbps的光收發器模組為主要配備,而目前光收發器模組的生命週期約為三至四年,且有漸漸縮短的趨勢;所以市場預計200Gbps與400Gbps的光收發器模組將很快取代現有的傳輸模組。而隨著未來資料中心之間與內部互連越來越大的傳輸流量需求,估計在不久的將來800Gbps和1.6Tbps的傳輸系統也將會有所需求。

100Gbps光收發器模組的開發最早從2010年開始,當時IEEE 802.3標準提出SR10、LR4和ER4三種標準,分別應用在100m OM3多模光纖、10km單模光纖和40km單模光纖的傳輸;在2015年,提出SR4的標準,應用在100m OM4多模光纖的傳輸。SR10使用10個光發射器與光接收器,每個通道的傳輸速率是10Gbps;LR4、ER4和SR4則使用4個光發射器與光接收器,每個通道傳輸速率為25Gbps。多源協議(Multi-Source Agreement, MSA)也在2014年提出PSM4和CWDM4兩個標準,也是使用四個光發射器與光接收器,每個通道傳輸速率為25Gbps;PSM4應用在500m單模光纖的傳輸,而CWDM4則應用在2km單模光纖的傳輸。表1彙整了目前常用100Gbps光收發器模組的標準與相關特性。

100Gbps光收發器模組的封裝類型常見的有CFP、CFP2、CFP4和QSFP28。CFP-MSA定義熱插拔收發器應用在40Gbps與100Gbps網路傳輸的需求,可以支援在單模與多模光纖上傳輸多種速率,在電氣介面可以支援10×10Gbps高速資料訊號的發射與接收,具有較大的模組尺寸,以及較高的功率消耗約為24W,不適合需要高密度傳輸的資料中心之需求。CFP2光收發器模組的體積是CFP的一半,功率消耗低於9W。CFP4光收發器模組的體積又是CFP2的一半,功率消耗也大約下降一半。CFP、CFP2、CFP4是較早期的型式,而QSFP28延續QSFP的外觀結構,但每個通道傳輸速率達28Gbps,具有比CFP4更小的模組尺寸與更低的功率消耗,所以目前已經成為資料中心100Gbps光收發器模組封裝的主流型式。

在光收發器的訊號調變技術中,若採用四階脈波振幅調變(Four-level Pulse Amplitude Modulation, PAM4)的資料格式,每階振幅可以表示兩個位元的資料,相較於以往採用非歸零(Non-Return Zero, NRZ)的資料格式,每階振幅只能表示位元0或1的資料。因此,PAM4資料格式在相同的頻寬下大約可以提高一倍的資料傳輸速率。因此,在已發布400Gbps光收發器的標準中,PAM4資料格式已被採用,並成為資料傳輸的主要調變格式。從2014年開始,IEEE 802.3便開始研議400Gbps光收發器的標準,一直到2017年12月正式公布標準,提出SR16、DR4、FR8和LR8四種標準。SR16仍使用25Gbps NRZ的資料訊號,以32道並列(16道做為發射,16道做為接收)多模光纖進行傳輸,使用OM4多模光纖可傳輸100m。DR4、FR8和LR8都採用PAM4的資料調變格式,但DR4採用的是100Gbps(50Gbaud)PAM4,而FR8和LR8則採用50Gbps(25Gbaud)PAM4;DR4使用8道並列的500m單模光纖進行傳輸,而FR8和LR8則使用WDM技術分別在2km與10km的單模光纖中傳輸。100G Lambda MSA也在2018年1月提出400G-FR4的標準,採用100Gbps PAM4資料格式,並使用WDM技術在2km單模光纖中傳輸。考量目前技術成熟的光電元件與相關積體電路的操作頻寬,預計400Gbps光收發器模組以8×50Gbps的解決方案將比4×100Gbps更快可以被實現達成。表2彙整了目前400Gbps光收發器模組的標準與相關特性。

資料中心內的光收發器模組技術朝向400Gbps速率發展的方向已是主流趨勢,而對於400Gbps光收發器模組要採用何種封裝型式,成本的考量會是技術轉型的思考重點,需要考量向下的兼容性與向上的發展性。目前400Gbps光收發器模組的封裝類型主要發展有三種,CFP8、QSFP-DD、OSFP。CFP8規範的外觀尺寸比CFP4大,可以支援16×25Gbps NRZ或8×50Gbps PAM4的傳輸介面,最高功耗為24W;由於CFP8的尺寸較大且功率消耗較高,因此資料中心較不考慮採用此類型收發器模組。QSFP-DD模組結構在標準的QSFP四通道電氣介面,多增加一排四通道介面,成為具有八通道的光收發器;QSFP-DD模組可以支援QSFP+和QSFP28標準,所以使用QSFP-DD模組所設計的系統可以向下兼容;功率消耗規範為12W;目前受到Amazon、Facebook和系統設備廠商Cisco的支持。OSFP模組封裝是比較新的外型,尺寸比QSFP-DD略大一些,所以可支援較高的功率消耗達到16W,較容易達成長距離傳輸的設計,但缺少與QSFP28向下兼相性;目前受到Google與Arista Networks等公司支持。如圖1,為CFP8、QSFP-DD、OSFP三種400Gbps光收發器模組封裝型式。

圖1 400Gbps光收發器模組封裝類型

除了前述三種400Gbps光收發器模組封裝型式外,COBO(Consortium of...

PCIe/CCIX化敵為友 資料中心傳輸效率翻倍

受到產業轉型、智慧型終端裝置、雲端服務及物聯網(IoT)普及率增加影響,全球網路資料中心流量近年來一直保持高速成長。在2018年,更能看到許多國際大廠如火如荼規畫興建新廠房,此一趨勢帶動了伺服器周邊零組件需求大增,其中,高速傳輸介面的發展更是備受注目。

雲端/邊緣同時驅動 資料中心蓬勃發展中

近年來,各大網路業者皆投入大量資金在建設超大型資料中心(Hyperscale Data Center),市調機構IDC估計2015年~2020年期間,資料中心市場將以每年5~10%的速度擴張。

拓墣產業研究院表示,數據資料的重要性已帶動企業對於數位轉型的龐大需求,但大量數據卻為既有資訊系統架構帶來沉重負擔。從雲端儲存、傳輸到運算,全面翻新企業的營運思維,造就了雲端廠商在近幾年的亮眼成績,以亞馬遜(Amazon)、微軟(Microsoft)、谷哥(Google)、IBM、阿里雲表現最為突出。

然而,不僅是超大型資料中心的發展引人注目,5G、人工智慧(AI)、物聯網等新興技術受到重視,以及各種終端應用全面智慧化的趨勢,邊緣運算概念所牽涉到的小型資料中心市場同樣不容小覷。DRAMeXchange資深分析師劉家豪便指出,未來隨著資料中心建置的普及,以及2020年之後5G的落實,針對邊緣運算的微型伺服器應用(Micro Server)將會在未來3~5年顯著成長,帶動相關零組件與記憶體的使用量明顯增加。

PCIe Gen5 Base Spec測試規範將就位

PCI-SIG在2010年發布PCI Express(PCIe) Gen3版本,並在市場上應用多年後,在2017年才終於推出了PCIe Gen4版本;並且,預計將在2019年8月完成PCIe Gen4 1.0版本制定。與此同時,PCI-SIG已開始積極投入PCIe Gen5的規範制定,並預計在2019年完成Gen5 Base Spec測試規範,滿足晶片層的量測需求。

PCIe Gen3傳輸效率為8GTps,PCIe Gen4則提高到16GTps,能滿足大量資料的傳輸需求,將於2019年制定完成的PCIe Gen5則會將傳輸速率進一步拉升,到達32GTps。而帶動這波介面速率升級的關鍵驅動力,就是資料中心廣泛建置所帶來的高速傳輸需求。Cadence亞太區資深應用工程經理李志勇(圖1)認為,目前PCIe Gen4甫起步,要再過一段時間才會漸漸看到商用產品出現,設備的汰舊換新亦是一漫長的過程,因此短期之內在伺服器市場將會看到PCIe Gen3與Gen4規格並存。

圖1 Cadence亞太區資深應用工程經理李志勇認為,由於設備更新需要相當的時間,PCIe Gen3與Gen4規格並存將成為短期內的狀況。

PCIe Gen5晶片2021量產

在未來PCIe介面的進化過程將會比以往更為快速。賽靈思PCIe與儲存解決方案資深產品經理Rakesh Cheerla(圖2)認為,由於處理器、PCIe交換器、繪圖處理器、張量處理器、乙太網路(Ethernet)NIC網卡以及FPGA等各大產品供應商都將推出PCIe Gen4晶片,因此估計資料中心的各種高效能應用將於2019年到2020年快速轉移至PCIe...

物聯網將帶動網路資料無「限」量產

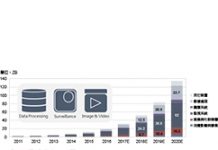

物聯網(IoT)不斷的蒐集數據、產生數據也帶來帶來數據處理的新挑戰。IoT裝置最直接的影響反映在數據流量、運算資源負載等數據傳輸(Datacom)問題,產業研究機構資策會MIC表示,雲端資料中心(DC)在2021年的數據流量大約近20,000EB(20ZB),2016~2021年的年複合平均成長率(CAGR)達到22%。

對比雲端DC、傳統DC工作量比重,雲端DC的比重在2021年將達到95%,意味著未來多數的傳輸設備,皆會更加倚靠雲端或以公有運算為基礎的解決方案,現有架構將不足以因應IoT的數據成長。

關於資料類型,資策會MIC認為,在2020年全球數據的生成類型當中,排名首位的數據生成是來自監視、影像動畫或圖像系統,其次則是一般數據處理(如網通通訊的排程),第三則為娛樂與社群媒體顯示IoT的需求,涉及到第一線使用者的使用習慣變化,尤其是倚靠圖像、影像作為媒介的傳輸習慣。

SerDes速度成400GbE挑戰 賽靈思Versal新品正面迎戰

資料中心市場若要採納400G Ethernet(400GbE)主要將面臨三大挑戰:更低成本、更低耗電以及採用更高速的SerDes,這三者之間也將彼此相互影響。

資料中心不停的追求更高的效能,促使業界發展出更快的介面速度。賽靈思(Xilinx)有線IP行銷部門經理Amy Chang指出,SerDes的高速序列介面是促成介面技術快速進展的關鍵技術,目前使用的SerDes技術為32GT/s。賽靈思以及少數幾家供應商現在能透過三公尺以上的銅導線與光纖支援56 GT/s的傳輸速度。

在未來三至五年,SerDes技術的鏈路速度將翻倍至112GT/s,而賽靈思未來推出的Versal系列產品也將皆支援此速度。目前業界主流的SerDes世代支援25G NRZ,並需要16鏈路的25G通道來支援400GbE乙太網路解決方案。隨著業界開始廣泛採納56G PAM4收發器,400GbE技術的成本與耗電需求將逐漸下滑,而112G PAM4在幾年內也會跟進。

賽靈思採用16×25G的介面及軟體矽閘極(Soft Silicon Gates)技術來展示400GbE方案的半導體廠商。賽靈思近期已開始出貨新款可支援8×53G 400GbE IP的UltraScale+ 58G系列元件,而預計在2020年將隨後推出112G。

Chang進一步說明,由於各界需要更高的資料傳輸率,FlexE將透過現有的低成本實體層,承載這些更高的資料傳輸率。賽靈思已採用標準型低成本100GbE技術,在4x100GbE FlexE上達到400GbE的傳輸率。在未來,該公司目標是透過N×400bG實體層運行更高的資料傳輸率(Terabit等級)。賽靈思將採用低成本的技術,來提供軟體IP促成這些更高的資料傳輸率。

記憶體規格大躍進 DDR 5訊號完整成測試挑戰

DDR3提供800~2133MT/s(每秒傳輸Mega)。DDR4提供1600~3200MT/s,傳輸速度是DDR3的兩倍。只需使用1.2V電壓,不僅效率比DDR3的1.5V更高,更可延長電池壽命並降低負載。循環冗餘檢查(CRC)和DDR4技術的晶片內建同位元偵測可增加額外指令與位址傳輸驗證,也能改善資料完整性。此外,DDR4記憶體容量也提升為四倍。DDR3最大記憶體容量是128GB,DDR4最多則可儲存512GB。

簡而言之,DDR4相較於DDR3的優勢包括:傳輸速度更快、效率更高、資料完整性更佳以及、更多記憶體空間。

至於DDR5標準,則可提供超過6GT/s傳輸速度及Tb等級記憶體容量時;整體傳輸速度和記憶體容量會再提高一倍;也就是傳輸速度更快、效率更高,以及記憶體空間更多。

訊號完整性為首要設計挑戰

DDR設計中最常見的訊號完整性挑戰就是記憶體控制器的時序問題。使用者可能會直接以購買方式取得設計所需記憶體控制器,而非採用訂製方式,若是如此,便需要在主機板和記憶體控制器間調整時序。

這樣的方式便足以執行設定和保持時間測試,以進行資料傳輸驗證。過去由於速度較慢,邊限也較寬,因此只要在通過設定與保持時間測試的情況下,在規格內便有足夠空間進行DDR2或DDR3設計。但速度提升也使邊限變得更加嚴格。若於進行DDR4或DDR5設計採用簡易的設定與保持時間測試,所提供之邊限已不足以通過規格驗證,而驗證DDR4需要眼圖(圖1)。

圖1 相符性應用測試內容中之DDR4遮罩測試,眼圖中央的矩形即為遮罩區域。

DDR4標準需在規格內符合隨機抖動和誤碼率的特定邊限與容差,因此可根據此標準為示波器建立遮罩,遮罩會定義示波器顯示器上的某個區域,此區域內的波形必須維持在滿足標準需求的狀態;如果眼圖閉合過多且進入遮罩,可能代表存在誤碼而無法通過規格標準。

我們預測DDR5眼圖會因DDR5速度提升而閉合。若確實如此,就必須利用等化技術讓眼圖張開至適當程度,以驗證設計。此外,DRAM錫球中會定義DDR5規格,但無法進入晶片探量。因此,必須改對通道進行探量,但無法透過此方式得知晶片中的眼圖為張開或閉合,需要決策回饋等化器來消除通道的脈衝響應效應。

善用邏輯分析儀避免資料毀損

驗證DDR4、LPDDR4、DDR5或LPDDR5設計時,常會遇到資料毀損的問題。造成資料毀損的原因有許多種,包含訊號完整性或功能性問題。示波器可對訊號完整性(包括眼圖大小、上升與下降時間及功率完整性)進行驗證與除錯,而邏輯分析儀則用來對記憶體系統功能或協定相符性進行除錯與驗證。若發生記憶體裝置無法以正確順序或在指定時序內接收正確指令等功能性問題,可能會造成資料毀損和系統癱瘓。測試是判斷實體或功能性錯誤和原因的重要方式,讓設計人員可為設計進行除錯並防止故障。

相符性測試軟體降低除錯難度

另外,設計人員還可利用相符性測試軟體,讓測試和除錯作業變得更輕鬆。相符性測試軟體可於示波器上執行,幫助驗證設計的訊號完整性及實體層。此軟體可自動執行相符性測試、驗證設計,並可產生通過/不通過報告,只需要將訊號連接到示波器,然後執行應用軟體即可。

若於進行設計功能或協定相符性測試時選擇合適的邏輯分析儀,便能以高達4200MT/s的資料速率及最高每個訊號400M樣本的追蹤深度,同步擷取所有DDR訊號(在DIMM/SODIMM設計超過100個訊號)。強大的分析軟體可進行記憶體協定傳輸解碼,並針對流經系統的訊務提供多種視圖與圖表,視圖和圖表可幫助驗證工程師快速瀏覽訊務流量,找出有問題的區域,協定相符性驗證軟體可於記憶體系統中精確找出問題。

總而言之,DDR記憶體晶片技術在過去十年歷經了兩個世代的演進,而新一代目前正在進行定義。每一代技術在速度、效率及記憶體容量方面都有所改進。

(本文由是德科技提供)

邊緣運算帶動新傳輸需求 CCIX/PCIe相輔拓商機

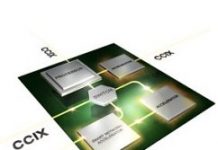

物聯網、機器學習等等新應用的興起,驅動了許多運算與資料處理的需求,該需求為資料中心產業鏈帶來了許多機會,同時也帶來了挑戰。目前,在應用領域中以PCIe Gen4為主流介面,而CCIX的出現,則有望在與PCIe聯手合作的狀況下,開啟更多異質運算的可能性。

自2016年起成立的CCIX聯盟,正企圖推動統一的標準,並創造出頻寬更高、延遲更低的介面標準,如此看來,不免認為CCIX將成為PCIe的頭號勁敵。然而Arm資深產品經理Jeff Defilippi認為,CCIX是一個基於PCIe協定延伸而生的通訊協定,對於Arm而言,會將CCIX視為一個與PCIe互補的通訊協定,而非競爭者。在新興的應用之中,出現了越來越多特殊的設備,像是TPU、GPU、FPGA的卸載應用,CCIX可充分運用既有的伺服器互連基礎設施,還提供更高的頻寬、更低的延遲,以及共用快取記憶體的資料同步性。這不僅大幅提升加速器的實用性以及資料中心平台的整體效能與效率,亦能降低切入現有伺服器系統的門檻,以及改善加速系統的總體擁有成本(TCO)。

Defilippi進一步說明,PCIe在市場行之有年,在短時間內依然會是非常關鍵的通訊協定;Arm也會持續支援相關的解決方案。Defilippi也指出,現在也可以看見越來越多設備同時支援PCIe與CCIX介面。

另一方面,伺服器不僅僅是可應用於超大型資料中心,中小型的資料中心也同樣帶動市場發展的重要驅動力。Defilippi舉例,如機器學習相關的應用不見得只會出現在大型資料中心,許多邊緣運算設備也同樣可以做到機器學習應用。而位於邊緣、較為小型的資料中心,所需要的高速傳輸介面與大型資料中心並無太大差異;然而,對於機器尺寸的要求將會更加嚴苛,這才是未來主要的技術挑戰所在。

希捷內部測試硬碟單位容量突破16TB

希捷科技近日宣布已運用其先進熱輔助磁記錄(HAMR)技術,建置並測試世界首款格式化且功能完備的標準3.5吋16TB企業級硬碟平台,打造出前所未有的高容量硬碟。希捷科技以領先群倫的HAMR技術樹立另一重大里程碑,2020年將單一硬碟的容量提升至20TB以上的計劃如預期進展。

希捷模擬客戶將硬碟整合至企業應用時常見的使用情境,對預發行版本Exos 16TB的HAMR硬碟進行測試。測試結果成功地顯示HAMR硬碟與標準企業應用環境中的其他硬碟並無二致,能夠隨插即用且順利運行。當用戶欲整合HAMR硬碟至現有的資料中心及系統時,無須進行任何結構上的改變,只需像使用其他任何企業級硬碟一樣插上即可使用。

隨著資料不斷在邊緣被擷取及創造,人們對儲存容量的需求也持續加速成長;人工智慧應用的不斷演進也促使更大資料集的需求,以淬鍊出關鍵的學習。換句話說,經濟實惠且易布建的儲存產品將推升數位化世界的發展。

希捷研發出HAMR技術大幅提升單一硬碟的儲存容量,新媒介磁記錄技術讓資料位元或顆粒變得更小、密度更高,同時維持磁性的穩定度。每個讀寫頭上的小型雷射二極體會加熱磁碟上的小點,使讀寫頭能夠迅速轉換每一個穩定位元的磁性以寫入資料。希捷的專利HAMR技術將符合業界的標準規格,能在相同空間下比傳統硬碟容納更多兆位元組(TB),降低用戶總持有成本。