新思

新思/台積電聯手加速3奈米SoC製程創新

新思科技日前宣布旗下數位(digital)與客製化(custom)設計平台已通過台積電3奈米製程技術的認證。該認證是以台積電最新的設計規則手冊 (design rule manual,DRM)和製程設計套件(process design kit,PDK)為基礎,為雙方廣泛合作和嚴格驗證的成果,能帶來可實現優化的功耗、效能和面積(PPA)的設計解決方案,進而加速新一代設計的開發。

台積電設計建構管理處資深處長Suk Lee表示,與新思科技多年來的合作成果為客戶提供了基於台積電先進製程技術的平台解決方案,令客戶受惠於台積電3奈米製程技術所帶來的功耗表現與效能的大幅提升,進而實現矽晶開發的創新,同時能快速將產品創新推向市場。通過認證的新思科技設計解決方案讓客戶可以更自信地基於台積電N3製程進行設計,並獲得優化的PPA。

藉由與台積電密切合作,新思科技開發出關鍵的特色功能和新技術,以確保台積電N3製程從合成到布局繞線,再到時序(timing)及物理簽核(physical signoff)的完整流程之間的關聯性。新思科技的Fusion Compiler RTL-to-GDSII 解決方案和 IC Compiler II布局繞線解決方案已加以擴展可支援台積電 N3 製程。經強化的新思科技Design Compiler NXT合成解決方案能讓設計人員充分利用台積電3奈米技術,透過採用高度精確的全新電阻和電容估計方法提升結果品質(QoR),並與新思科技的IC Compiler II布局繞線解決方案具備更緊密的關聯性。PrimeTime 簽核解決方案(signoff solution)支援先進的多輸入切換 (multi-input switching,MIS),用於精確的時序分析(timing...

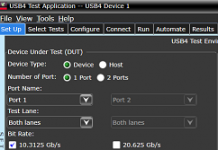

是德推出USB4測試解決方案 提高設計效能並確保符合性

是德科技(Keysight)日前宣布推出全新的USB4測試解決方案,以全面提升USB設計效能並確保USB標準相符性,進而實現最佳的量測準確度和信號傳真度。

是德積極參與USB開發者論壇(USB-IF)的下一代USB4規範制定工作。 各種不同的電子產品,包括智慧型手機、筆記型電腦、桌上型電腦、平板電腦和數位相機,都將倚賴新一代的高速數位標準來維持運作。USB4基於Thunderbolt協定規格,是一種隨插即用的數位通訊介面,在頻寬、功率以及資料傳輸效能具有顯著的優勢。

新思科技(Synopsys)IP行銷與策略資深副總裁John Koeter表示,全球約有數十億個裝置,均依靠新思DesignWare USB IP來相互連接,充分展現了我們為設計工程師提供高品質IP,以符合多數先進協定標準要求的用心。新思能夠提供完整USB4 IP解決方案。利用是德全方位USB4測試與除錯解決方案,我們可確保我們的IP符合USB-IF規範,以協助設計工程師更快推出符合標準、可互通的產品,並且大幅降低風險。

是德網路和資料中心事業群副總暨總經理Joachim Peerlings表示,資料中心業者和裝置製造商必須找到能夠符合成本、效能和功耗要求的資料傳輸方法。 是德提供最齊備的測試和量測解決方案,有助於加速USB4設計的開發,進而建立一個端對端通訊生態系統。

新思/台積/微軟聯手 提供高可擴展時序簽核流程

新思科技(Synopsys)近日宣布,與台積電(TSMC)和微軟公司(Microsoft)合作完成用於雲端環境、具備開創性與高度可擴展性的時序簽核流程(timing signoff flow)。這項長達數個月、集合三方合作夥伴的大規模合作案,有效加速新一代系統單晶片(systems-on-chips,SoCs)的簽核路徑(path)。利用微軟Azure平台上的新思科技 PrimeTime靜態時序分析和 StarRC 寄生萃取(parasitic extraction)可大幅提升簽核流程的產出量。

台積公司設計建構管理處資深處長Suk Lee表示,由於先進的製程技術、加上擴大的元件庫以及待分析的操作條件增加,使得晶片設計的複雜度不斷提高,因此設計簽核的周轉時間(turnaround)就變得非常重要。利用雲端平台是大幅提升簽核速度的好方法,而且將徹底影響矽晶設計。台積公司是第一個與設計生態系合作夥伴和雲端供應商合作,實現雲端環境晶片設計的晶圓代工廠。藉由與微軟和新思科技的合作,我們的雲端聯盟在時序簽核方面展現了顯著的產出提升與可擴充性,並為共同客戶提供靈活、安全且有效率的解決方案,來加快 SoC 的上市時程。

微軟Azure晶片、電子與遊戲產品工程首席經理 Mujtaba Hamid表示,在先進製程節點上,由於製程複雜性高,想要縮短設計時間便需要橫跨基礎架構與工具鏈的技術創新。這項合作關係為signoff iteration的成本與效能間的取捨提供了關鍵的見解,協助客戶為矽晶產品的設計做出有效的決策。

採用台積公司 N5 製程以及PrimeTime 靜態時序分析和 StarRC 萃取的的百萬閘極(gate)晶片設計,在微軟Azure最新的Edsv4系列運算個體(compute instance)上執行時序簽核。藉由大規模並行處理數百台機器的運作,PrimeTime DMSA 和 StarRC 多角萃取(multi-corner extraction)之向外擴展(scale-out)可大幅提高產出量。此外,在單一機器上執行多個情境,向內擴展(scaling-in)也可節省大量成本。

新思針對台積5奈米製程推IP組合 加速高效運算SoC設計

新思科技(Synopsys)近日宣布,針對運用於高效能運算系統單晶片 (SoC)的台積公司 5奈米製程技術,推出業界廣泛的高品質 IP 組合。應用於台積公司製程的DesignWare IP組合內容包括介面IP(適用於業界最廣泛使用的高速協定)和基礎IP,可加速高階雲端運算、AI加速器、網路和儲存應用SoC的開發。新思科技DesignWare IP 與台積公司 5奈米製程的結合,可協助設計人員掌握設計在效能、功耗和密度的嚴格要求,同時降低整合風險。

台積公司設計建構管理處資深處長Suk Lee表示,我們與新思科技長期合作為我們雙方的客戶提供了基於先進製程技術的DesignWare IP,令客戶面對高效能運算等各種市場時能達成一次完成矽晶設計(first-pass silicon success)。基於台積公司先進製程技術的廣泛DesignWare IP組合,可協助設計人員快速地將必要的功能融入設計中,同時受惠於先進晶圓代工解決方案 、也就是5奈米製程技術,所帶來的強大功耗與效能的提升。

新思科技IP行銷策略資深副總裁John Koeter則表示,近二十年來,新思科技的DesignWare IP一直走在業界前端,基於台積公司的每一代製程技術實現無可比擬的功耗、效能和面積表現。藉由提供基於台積公司5奈米製程技術的業界廣泛的介面和基礎IP組合,新思科技協助雙方客戶加速高效能運算SoC的發展。

新思攜手台積電實現HPC/行動/5G/AI等SoC設計

新思科技(Synopsys)近日宣布,運用於台積公司N6 及N5製程技術的數位與客製化設計平台已取得認證。新思科技與台積公司的長期合作加快了高效能運算(high-performance computing ,HPC)、行動、5G 和 AI 晶片設計等關鍵垂直市場的新一代產品設計。

這項成就是雙方多年來廣泛合作的成果,以提供最佳的設計解決方案,並透過創新來提升節能效率和設計效能,從而加速新一代設計的發展。新思科技與台積公司的合作也擴展到 3DIC 製程技術,其中包括 CoWoS 、InFO 和 TSMC-SoIC ,這些技術能實現可擴展的整合,以達到更好的功能與更強大的系統效能。

台積公司設計建構管理處資深處長Suk Lee表示,台積公司與其生態系統夥伴密切合作,確保半導體設計人員能使用台積公司最新的製程技術,以符合高成長市場中新一代設計對效能和低功耗的要求。我們期待與新思科技繼續合作,以協助雙方客戶為高效能運算、行動、5G 和 AI 應用釋放矽晶開發之創新能量。

通過認證、運用於HPC和行動設計流程的新思科技設計工具的創新功能,能讓設計人員充分利用台積公司 N6 和 N5 製程技術,提高密度、操作頻率(operating frequency)和功耗表現。另外,新思科技的工具功能也已經過提升,可支援低功耗行動和 5G...

新思推3DIC Compiler平台加速多晶粒系統整合

新思科技(Synopsys)近日推出3DIC Compiler平台,可在單一封裝中實現複雜的2.5D和3D多晶粒系統(Multi-die System)的設計與整合。該平台提供全面性的整合、高效且易於使用的環境,透過單一解決方案提供架構探索(Architectural Exploration)、設計、實作與簽核,同時達到訊號、功耗與熱完整性(Thermal Integrity)的最佳化。透過3DIC Compiler,IC設計與封裝團隊可達到良好的多晶粒整合與協同設計(Co-design)水準,並實現更快速的收斂。

三星電子(Samsung)設計平台開發部執行副總裁Jaehong Park表示,透過與新思科技的合作,可以為共同客戶提供適用於高階網路和高效能運算應用的先進多晶粒封裝解決方案。新思科技的3DIC Compiler整合型平台,顛覆先進多晶粒封裝的設計方式,因為它能為 2.5D/3D 多晶粒解決方案提供整體的設計工作流程。

隨著對矽晶可擴展性(Scalability)和新系統架構的需求不斷增加,2.5D和3D多晶粒的整合已成為符合系統層級效能、功耗、面積與成本要求的首要條件。越來越多的因素促使系統設計團隊利用多晶粒整合來因應人工智慧和高效能運算等新型應用,而這些應用也促進封裝解決方案將高頻寬或低延遲(low-latency)記憶體相結合的新型封裝架構,如小晶片(Chiplet)和堆疊式晶片(Stacked-die)整合其中。

隨著2.5D和3D IC的問世,IC封裝的需求條件也越來越類似IC設計的需求條件,例如像是具有數十萬個晶粒間互連(Inter-die Interconnect)的類SoC規模(SoC-like Scale)。傳統的IC封裝工具與現有的IC設計工具通常很鬆散地整合在一起,然而,傳統工具的可擴張展性根本上受限於數據模型,且隨著近來複雜3D架構設計的要求而不敷使用。此外,由於沒有交集的工具加上整合鬆散的流程,使得3DIC設計時程總是不可預測、漫長且時常無法收斂。

新思科技的3DIC Compiler以IC設計數據模型為基礎,透過更現代的3DIC結構實現容量和效能的可擴展性。3DIC Compiler提供了涵蓋規畫、架構探索、設計、實作、分析與簽核的單一環境。另外,還針對所有檢視(Views)包括架構、規畫、設計、實作、分析和簽核等),提供360度3D檢視、交叉探測(Cross Probing)等獨特且易於使用的視覺化功能,為IC 封裝的可用性(Usability)樹立了新標準。

新思科技與多物理場模擬(Multi-physics Simulation)領域的廠商安矽思(Ansys)公司合作,將安矽思具備通過矽晶驗證分析能力的RedHawk系列產品與3DIC Compiler整合。RedHawk 能產生高度精確的訊號、熱和功耗數據,而這些數據能與3DIC Compiler緊密整合,用於封裝設計。與分散的解決方案相比,RedHawk 和新思科技 3DIC Compiler之間的自動反向演繹(Back-annotation),能以較少的迭代(Iteration)次數實現更快速的收斂。

安矽思副總裁暨總經理John...

新思針對新網路通訊系統推800G乙太網路驗證IP

新思科技(Synopsys)近日宣布,針對800G乙太網路推出第一個驗證IP(Verification IP, VIP)和通用驗證方法(Universal Verification Methodology, UVM)原始碼測試套件。

MorethanIP公司總裁Francois Balay表示,該公司的800Gb乙太網路MAC與PCS核心已協助客戶開發出針對800Gb乙太網路應用之解決方案。而新思科技是第一個為800G乙太網路提供VIP、原始碼測試套件和DesignWare IP的公司,這不但能強化網路通訊生態系統,還可促進相關技術的採用和高速網路應用的快速發展。

隨著支援隨選視訊(Video-on-demand)、社群網路與雲端服務的頻寬需求不斷增加,新思科技針對800G乙太網路的VC VIP,是以乙太網路技術聯盟(Ethernet Technology Consortium, ETC)規範為基礎,可協助SoC設計團隊為資料中心設計出易於使用且能快速整合的新一代網路晶片,從而加速驗證收斂(Verification Closure)與上市時間。當VC VIP用於驗證新思科技針對FinFET製程中之DesignWare 56G 乙太網路、112G 乙太網路和112G USR/XSR PHY,設計人員可輕易地將其與800G SoC整合,以符合其長距離(Long Reach)和短距離(Short Reach)介面的要求。

ETC標準針對8 lane x100...

新思推RTL Architect加速設計收斂

新思科技(Synopsys)近日宣布RTL Architect即刻上市,該創新產品可有效加速RTL設計收斂(Design Closure),促進整體晶片設計流程的向左推移(Shift-left)。新思科技的RTL Architect是第一個具備實體察覺(Physically Aware)的RTL設計系統,能縮短一半的SoC實作週期,並實現卓越的結果品質(Quality-of-results, QoR)。

瑞薩電子(Renesas)EDA共享研發暨電子數位設計技術處處長Hideyuki Okabe表示,瑞薩正在設計一種複雜而先進的車用SoC,而這需要架構調整(Architecture Tuning)以實現最高的OoR,以便在目標市場中脫穎而出。新思科技RTL Architect能讓該公司在RTL階段快速探索、驗證各式架構,並找出最佳方案,讓該公司不必擔心後期發生突發狀況。

為了提升功耗、效能和面積(PPA)的表現,以符合人工智慧和汽車應用等新垂直市場的要求,快速探索特定領域的RTL架構已成為RTL團隊經常面對的挑戰。由於下游實作的準確度低,因此用來評估RTL品質的現有單點工具(Point Tool)受到嚴重限制。這些早期設計週期的不準確性導致下游實作工具得進行彌補措施,通常得回頭修正RTL才能達到PPA的目標。為了因應這些挑戰,RTL Architect採用新思科技「融合設計平台」(Fusion Design Platform)實作環境的快速多目標預測引擎,準確預測下游實作的PPA。RTL Architect能讓RTL設計人員確切地找出原始碼中的瓶頸,以提高RTL品質。

RTL Architect系統是建立在統一的數據模型上,該模型提供了數十億的閘容量(Gate Capacity)和全面性層階設計(Hierarchical Design)的能力,能應付先進製程節點中不斷增加的設計和區塊尺寸(Block Sizes)。該產品直接利用新思科技世界級的實作與金級簽核解決方案,能在設計週期初期即提供準確的結果,且該結果是與建構相關的(Correlate-by-construction)。

RTL Architect使用快速的多維實作引擎,讓RTL設計人員可以預測RTL變更對功耗、效能、面積與壅塞(Congestion)的影響。該產品整合了新思科技PrimePower的金級簽核功耗分析引擎,可進行準確的RTL功耗預估和優化,實現節能設計。RTL Architect提供統一的工作流程環境,可針對重要PPA品質指標進行簡化且易於使用的分析。另外,也為閘層級(Gate-level)的PrimePower既有用戶提供PrimePower RTL功耗預估,從而透過一致的RTL進行功耗分析流程的簽核。

新思針對晶片設計開發AI應用

新思科技(Synopsys)近日推出「設計空間優化AI」(Design Space Optimization AI)—DSO.ai,第一個針對晶片設計而開發出的自主人工智慧應用。新思科技的DSO.ai解決方案受到AlphaZero的啟發,是一種具備人工智慧和推理的引擎,能在較大量的晶片設計解決方案中,尋找優化目標。DSO.ai徹底改變晶片設計,透過大量探索設計工作流程的可能選項同時自動執行後續決策,讓SoC團隊能以專家級的水準運作,並顯著提升整體產能。

三星電子晶圓代工設計平台開發執行副總裁Jaehong Park表示,新的矽晶技術不斷挑戰物理極限,而該公司的客戶也在尋求能實現創新產品的製造解決方案。在設計環境中,新思科技的DSO.ai有系統地找到優於先前功率/效能/空間(Power-performance-area; PPA)表現的良好解決方案。此外,DSO.ai能在短短三天內達成上述成果,而這在以前需要數名專家進行一個多月的實驗才能達成。這種AI導向的設計方法,讓客戶充分利用三星矽晶技術優勢,進行SoC晶片設計。

當前AI可以透過自然語言與人類互動、能辨識銀行詐騙並保護電腦網路安全、能駕車上路,也可以玩西洋棋和圍棋等智慧遊戲。同樣的,基於AI的晶片設計也擁有廣大的潛在解決方案空間(Space of Potential Solutions),其規模可以是圍棋遊戲的數兆倍。

搜尋這廣大空間是較費力的工作,通常需要花上數周的實驗,而且往往要靠過去的經驗值和不為外界所知的知識。晶片設計的工作流程通常會使用並產生萬億位元(Terabytes, TB)的高維度數據,這些數據在許多個別優化的數據孤島(Silo)中進行分區和分段;而為了建立最佳的設計流程方案(Design Recipe),工程師必須獲取大量而高速的運算數據,並在缺乏完整性的情況下,即刻做出複雜的分析與決策,而這往往導致決策疲勞(Decision Fatigue)和設計制約(Design constrain)。

在當今市場競爭異常激烈及嚴苛的矽晶製程要求下,一般的製程方案與最佳的製程方案造成的差異,可能是100MHz的效能、電池壽命時數以及數百萬美元的設計成本。

藉由實現廣大設計空間的自主性優化,新思科技的DSO.ai解決方案為搜尋最佳解決方案帶來革命性的創新。DSO.ai引擎能擷取晶片設計工具產生的大數據,並加以運用以探索搜尋空間,觀察設計如何隨時間變化並調整設計選擇、技術參數與工作流程,藉此引導探索過程朝多面向優化的目標發展。DSO.ai使用新思科技所研發的先進機器學習技術來進行大規模搜索,能即時地自主運作數萬個探索向量,同時獲取十億位元(Gigabytes, GB)的高速設計分析數據。

新思科技正式成立新竹AI設計中心

響應政府推動AI(人工智慧)科技發展的政策,因應當前產業發展趨勢,新思科技(Synopsys)已在新竹交通大學博愛校區增建研發中心,現更進一步延伸全球研發能量成立「新竹AI設計中心」,引進AI晶片設計所需之核心技術,並歡迎具備相關本職學能之優秀人才,加入新思科技的研發團隊,為台灣推動AI科技發展盡一份心力。

新思科技全球副總裁暨台灣區總經理李明哲表示,新思科技致力協助台灣半導體技術的升級,與培育半導體設計軟體人才,而AI技術與應用的發展,不僅是當前政府推動科技產業的主軸之一,更已帶動半導體設計對於創新技術的需求,該公司將積極展開產官學研的合作,協助提升台灣在先進製程與AI技術上的研發能量,進而掌握相關的商機。

新思科技持續支持政府AI on Chip示範計畫的推動。2017年即參與科技部「半導體射月計畫」,與科技部所屬財團法人國家實驗研究院簽訂AI策略聯盟合作意向書,協助建構AI創新生態環境,帶動AI新興產業應用發展;2018年與國研院晶片中心及多所大學研發團隊簽署AI研發深耕計畫合作意向書,共同開發系統晶片與關鍵技術,以誘發學界對於AI晶片的研發能量。

新思科技也於去(2019)年三月間特別針對AIoT晶片設計技術,與台灣大學、清華大學、交通大學、中央大學以及成功大學等學校展開合作,提供各校晶片開發核心套件與人工智慧相關教材,協助這些大學成立AIoT設計實驗室,讓學生們接觸與吸收符合當前產業需求的先進技術。