台積電

Mentor擴展支援台積電5奈米FinFET/7奈米FinFET Plus製程技術方案

Mentor近日宣布,該公司的Mentor Calibre nmPlatform 與Analog FastSPICE(AFS)平台已通過台積電7奈米FinFET Plus與最新版本的5奈米FinFET製程認證。此外,Mentor持續擴展Xpedition Package Designer和Xpedition Substrate Integrator產品的功能,以支援台積電的先進封裝技術。

台積電設計建構行銷事業處資深處長Suk Lee表示,台積電正與Mentor密切合作,藉由提供更多的功能在其EDA解決方案以支援我們新的5奈米與7奈米FinFET Plus製程,Mentor持續在台積電生態系統中帶來更高的價值。Mentor是我們多年來的重要策略夥伴,憑藉著西門子將持續為Mentor的電子設計自動化(EDA)技術進行策略性投資,將可協助雙方的共同客戶更成功地把新一代令人驚豔的IC技術創新帶到市場。

Mentor增強了Calibre nmDRC與Calibre nmLVS工具,以支援台積電7奈米FinFET Plus製程與最新版本的5奈米FinFET製程。Mentor持續提供台積電客戶所需的功能性與效能,以助其達到製造需求。Calibre nmDRC和Calibre nmLVS工具已可提供雲端服務,並且可有效運用於數千個CPU數量的伺服器方案供客戶使用。

Mentor的Caliber YieldEnhancer工具已通過台積電5奈米與7奈米 FinFET Plus製程認證。Mentor和台積電已開發獨特的填充程式庫,可透過緊密控制填充形狀的位置來達到製造要求。結合Calibre YieldEnhancer工具的功能與台積電的Calibre填充設計套件(Fill Design Kit),可把填充率(Insertion Rate)提升至最高。

Calibre...

先進製程才是半導體製造金雞母

根據產業研究機構IC Insights研究顯示,全球前四大晶圓代工廠(台積電、GlobalFoundries、聯華電子和中芯國際)加工晶圓產生的平均收入預計在2018年為1,138美元,用八吋等效晶圓表示,與2017年的1,136美元持平,四大代工廠的平均單位收入在2014年達到1,149美元,然後在去年緩慢下降。

台積電2018年平均每晶圓收入預計為1,382美元,較GlobalFoundries的1,014美元高出36%,聯電2018年每片晶圓的平均收入預計僅為715美元。此外,台積電是四家廠商中唯一一家預計2018年將比2013年產生更高的每晶圓收入的晶圓代工廠。相較之下,GlobalFoundries、UMC和中芯國際2018年每晶圓平均收入預計與2013年相較分別下降1%、10%和16%。

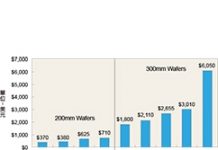

就2018年第二季的統計,晶圓代工廠生產的不同製程和晶圓尺寸創造的營收可見。採用0.5微米的8吋晶圓創造營收370美元,而20奈米(nm)以下製程的12吋晶圓可創造6,050美元營收,兩者之間的差距超過16倍。即使以每平方英寸的方式計算,差異也非常大(0.5微米技術為7.41美元,≤20nm技術為53.86美元)。由於台積電45奈米以下的先進製程比重高,預計該公司每片晶圓的收入將從2013年到2018年以2%的年複合成長率(CAGR)成長。

隨著GlobalFoundries暫緩7奈米先進製程的研發,IC Insights認為,在未來五年內,可能只有三家廠商能提供先進製程技術/產品,即台積電、三星和英特爾。

首款AI加速平台出鞘 Xilinx全面擁抱人工智慧

人工智慧AI發展全面展開,可編程邏輯廠商美商賽靈思(Xilinx)認為,未來已經沒有一個架構可以滿足所有的應用需求,因此該公司正式踏上轉型之路,舉辦賽靈思開發者大會(XDF),並發表未來幾年的技術與產品重點,全面擁抱人工智慧的發展趨勢,以資料中心(Data Center)為發展策略的起點,目標為打造靈活應變、萬物智慧的世界。

一直以可編程技術為發展重點的Xilinx,2018年3月正式啟動策略轉型工作,宣示該公司從元件廠商轉型為平台廠商,提出自行調適運算加速平台(Adaptive Compute Acceleration Platform, ACAP)發展核心,旋即於10月推出第一款產品Versal。Xilinx總裁暨執行長Victor Peng表示,Versal字面上是由Variety與Universal組合而成,希望在技術與應用上可以兼顧多樣性與通用性。

在AI無所不在的時代,AI應用日新月異,晶片設計週期已經落後創新的速度,因此Peng認為,FPGA彈性的特點可以應用在AI的創新上,一般新晶片設計週期高達24個月,透過ACAP平台的協助,可將AI模型加以拆解,變成數個不同的發展(Develop)、優化(Optimize)、部署(Deploy)流程,該平台動態範圍廣泛彈性,可針對不同的應用調整需要的加速範圍。

Versal ACAP結合純量處理引擎(Scalar Processing Engine)、Arm Cortex-A72與Arm Cortex-R5,以及自行調適硬體引擎(Adaptable Hardware Engine),可動態重新配置,即時加速能力最高達八倍;DSP引擎可提供高準確性浮點運算與低延遲;AI引擎具有高傳輸率、低延遲與高效率,可協助AI推論與高階訊號處理,搭配先進記憶體和介面技術,可提供強大的異質加速能力。不管是軟體開發者、資料科學家或是硬體開發者,只須利用符合業界標準設計流程的工具、軟體、函式庫、IP、中介軟體以及框架,就能針對其硬體與軟體進行編程與最佳化。據了解,Versal採用台積電7奈米FinFET製程,正式量產時間為2019年第二季。

Xilinx也以現有UltraScale+ FPGA為基礎,發表Alveo U200與Alveo U250加速卡,就機器學習而言,Alveo U250的即時推論傳輸率比高階CPU高出20倍,甚至在低於2毫秒的低延遲應用方面,也比高階GPU這類固定功能加速器高出4倍。此外,Alveo加速器卡的延遲較GPU減少3倍,在資料庫搜尋等應用方面大幅加速、並提供較CPU高出90倍的效能。

Xilinx總裁暨執行長Victor Peng表示,FPGA靈活彈性將有助AI創新應用發展。

ANSYS獲台積電7奈米製程/先進封裝技術認證

ANSYS宣布,採極紫外線微影(Extreme Ultraviolet Lithography, EUV)技術的7奈米 FinFET Plus(N7+)製程節點的ANSYS解決方案已獲台積電(TSMC)認證,台積電亦驗證最新InFO_MS(Integrated Fan-Out with Memory on Substrate)先進封裝技術的參考流程。對無晶圓廠(Fabless)半導體公司而言,由於模擬工具需通過新製程節點和封裝技術嚴格測試與確認,因此認證與驗證非常重要。

ANSYS RedHawk與ANSYS Totem皆獲得台積電N7+製程技術認證,並且支援極紫外線微影(EUV)功能。N7+認證包含萃取、電源完整性與可靠度、訊號電子飄移(Signal EM)與熱可靠度分析。

台積電拓展領先業界的整合型扇出(Integrated Fan-Out, InFO) 先進封裝技術,整合記憶體子系統(Subsystem)與邏輯晶粒。台積電與ANSYS提升既有InFO設計流程,支援新InFO_MS封裝技術,並運用ANSYS SIwave-CPA、ANSYS RedHawk-CPA、ANSYS RedHawk-CTA、ANSYS CMA與ANSYS CSM驗證相關晶片模式下的參考流程。InFO_MS參考流程包含針對萃取的晶粒和封裝進行共同模擬與共同分析、電源和訊號完整性分析、電源和訊號電子偏移以及熱分析。

台積電設計建構行銷事業處資深處長Suk Lee表示,台積電與ANSYS提供最新的N7+認證與InFO_MS支援,幫助客戶滿足新世代晶片和封裝在效能、可靠度和電源方面的成長需求。

AI on Chip示範計畫籌備小組啟動

根據Gartner預估,2018年AI晶片市場產值將成長至10億美元,至2022年將達132.5億美元。為掌握此數位科技發展趨勢,推升台灣AI晶片在國際上的角色,行政院除於年初通過「台灣AI行動計畫」外,將更強化資源共享與整合,在科技政委吳政忠的協調下,緊密結合經濟部「AI領航推動計畫」與科技部「半導體射月計畫」、「AI創新研究中心計畫」,於近日成立「AI on Chip示範計畫籌備小組」。

本籌備小組由行政院科技會報辦公室執行秘書蔡志宏擔任總召集人,經濟部次長龔明鑫及科技部次長許有進擔任共同召集人,邀集產學研代表共同召開啟動會議,期結合產官學研能量,串聯產業上、中、下游資源,聚焦「半通用AI晶片」、「異質整合AI晶片」、「新興運算架構AI晶片」與「AI晶片軟體編譯環境開發」四大議題,建立起世界領先的AI晶片供應鏈。

行政院科技會報辦公室已召開多次座談會,邀請各界商議我國AI晶片發展機會。由於AI晶片應用領域廣泛,使國內外軟硬體科技大廠如NVIDIA、Intel、Google、Microsoft、聯發科、台積電等皆大量投入資源掌握發展先機。台灣不但具備領先世界的半導體供應鏈,包含IC設計服務、晶片製造、半導體測試與封裝等,亦擁有世界一流的系統設計及製造能力,創造許多產業的隱形冠軍,如能串連台灣AI及半導體/晶片設計產業上、中、下游共同合作並資源共享,將可孕育出全球獨一無二的AI晶片產業生態系。