先進封裝

推進摩爾定律 半導體先進封裝領風騷

半導體效能的提升與「摩爾定律」多年來幾乎成為同義詞,過去製程微縮是達成每兩年同樣單位面積中,塞入兩倍電晶體最主要的手段,然而製程微縮在近年也碰到物理極限瓶頸的挑戰,如何持續透過技術的演進改善積體電路的效能,成為半導體產業最重要的任務,「先進封裝」成為最近幾年提升晶片效能的重要技術,相關技術受市場重視程度也水漲船高。

半導體線寬/線徑的微縮遭遇技術挑戰,晶片或裸晶的整合成為推升半導體效能的另外一個手段,立體堆疊與異質整合(Heterogeneous Integration)則是封測技術發展的核心要項。透過封裝技術整合晶片與製程微縮是不同層面的積體電路整合,但目的同樣都是為了提升電晶體的集積度,從早期的系統級封裝(System in Package, SiP)到晶圓級封裝、3D堆疊等同質整合(Homogeneous Integration)技術,到近期代表性的異質整合概念小晶片(Chiplet)設計帶動的封裝發展都具有高度潛力。

先進封裝成長動能強勁

先進封裝包含覆晶封裝、晶圓級扇入扇出型封裝及內埋式封裝等。根據產業研究機構Yole D'eveloppement研究指出,2018~2024年先進封測產值之年複合成長率(CAGR)高達8.2%,相較非先進封測技術產值CAGR約2.4%,與整體封測業產值成長率約5%,成長動能相對突出,且2024年先進封測產值與其他產值比重將進一步縮小。

隨著電子終端產品朝向低價格、多功能、高效能、高整合度發展,未來幾年5G與AI將引領科技應用發展的腳步,而半導體晶片製程走到3~5奈米,終端產品也要微型化與高度整合的晶片協助,須使用晶圓級封裝(Wafer Level Package, WLP)技術,如2.5D/3D IC、扇出型封裝(Fan-out Package)等,因應用領域或晶片類型不同會採用不同的技術,工研院產科國際所產業分析師楊啟鑫表示,主要目的就是提升效能與降低成本。

扇出型晶圓級封裝(Fan-out Wafer Level Packaging, FOWLP)技術與採用TSV的正統3D IC相較,概念接近2.5D IC,且成本可低於TSV 3D IC,因而逐漸受市場青睞。而在市場需求部分,扇出型封裝晶片具備薄型化與低功耗之優勢,故在產品應用上以可攜式裝置為大宗,預計2021年將消耗363萬片12吋晶圓,相較於2014年台積電推出InFO封裝時之33萬片12吋晶圓消耗量,已大幅成長約11倍。

而扇出型封裝若要能持續降低製作成本以增加應用,擴大製程基板的使用面積是最重要的手段,以12吋(300mm)晶圓來看,其可使用面積僅約為3.5代(620mm×750mm)玻璃基板的15%,突顯玻璃基板在面積上的優勢。相較於晶圓級扇出型封裝技術,投入面板級扇出型封裝若能建立足夠的良率,將可以大幅降低成本,所以面板級扇出型封裝成為封測大廠2020年的發展重點,楊啟鑫指出,面板級扇出型封裝分為先晶片(Chip First)與後晶片(Chip Last)技術類型,各廠也有自己的發展重點。

面板級扇出型封裝成兵家必爭之地

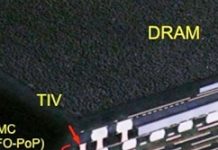

先晶片技術的優勢在於不需凸塊(Bumping)製程成本較低,缺點為若低良率發生時將導致晶片損壞;後晶片的優勢在於可以製作高階晶片,大型且具高密度接腳,缺點為需花費凸塊製程費用導致成本較高。關於主要封裝廠的動態,楊啟鑫說明,日月光積極布局扇出型封裝技術,除了自行開發之外,也與英飛凌(Infineon)及DECA的M-Series技術合作及授權,其他系列技術還包括:eWLB、FOCoS、FOPoP、FOSIP、HD FOCoS、Panel FO等。

另外,全球記憶體封測第一大廠力成,近年積極發展邏輯IC封測,從中低階邏輯IC封測跨入高階面板級扇出型封裝技術,開發各種型態的扇出型封裝技術,符合不同IC的應用需求(圖1)。在低成本部分有不需凸塊的Bump...

各路人馬競逐先進封裝大餅 OSAT產業秩序面臨洗牌

研究機構Yole Developpement估計,2019年全球先進封裝市場的規模為380億美元,且預期在2019年至2025年間,將以6.6%的複合年增率(CAGR)成長,到2025年時,先進封裝的市場規模。

由於摩爾定律減緩和異質整合帶來的強勁動力,加上 5G、AI、HPC、IoT 等大趨勢,先進封裝市場在整個半導體市場中所占的比重正在不斷增加。預估到2025年時,先進封裝將占整個半導體市場的近50%。

在技術方面,先進封裝正在從傳統封裝基板轉向矽基板。這一趨勢為台積電、英特爾(Intel)和三星(Samsung)帶來龐大的發展機會。也因為如此,台積電在先進封裝市場已經成為一家不可忽略的公司,2019年其封裝業務的營收預估可達28億美元,如果將其視為一家OSAT公司,台積電在2019年OSAT營收排行榜上,將排名第四。

技術的轉變將使OSAT產業大者越大的趨勢繼續發展,位居領先群的大型OSAT將繼續投資發展各種先進封裝技術,擴大其領先地位;後段班的OSAT業者將面臨更激烈的市場競爭,倘若無法追上領先業者,又缺乏差異化的技術或IP,恐將有被迫退出市場的風險。

另一方面,先進封裝市場的快速成長,也吸引原本專注於其他領域的電子業者投入,例如許多大型EMS/ODM業者,已經對此市場展現濃厚興趣,並展開相關布局。

兩片全幅光罩拼接 台積/博通聯手寫下CoWoS里程碑

台積電近日宣布,與博通(Broadcom)攜手合作,推出業界首創且尺寸最大的兩倍光罩尺寸(2X reticle size) CoWoS中介層,面積約1,700平方毫米。此項新世代CoWoS中介層由兩張全幅光罩拼接構成,能夠大幅提升運算能力,藉由更多的系統單晶片來支援先進的高效能運算系統,並且也準備就緒以支援台積公司下一世代的5奈米製程技術。

此項新世代CoWoS技術能夠容納多個邏輯系統單晶片(SoC)、以及多達六個高頻寬記憶體(HBM)立方體,提供高達96GB的記憶體容量;此外,此技術提供每秒高達2.7兆位元的頻寬,相較於台積公司2016年推出的CoWoS解決方案,速度增快2.7倍。CoWoS解決方案具備支援更高記憶體容量與頻寬的優勢,非常適用於記憶體密集型之處理工作,例如深度學習、5G網路、具有節能效益的數據中心、以及其他更多應用。除了提供更多的空間來提升運算能力、輸入/輸出、以及HBM整合,強化版的CoWoS技術亦提供更大的設計靈活性及更好的良率,支援先進製程上的複雜特殊應用晶片設計。

在台積電與博通合作的CoWoS平台中,博通定義了複雜的上層晶片、中介層、以及HBM結構,台積公司則是開發堅實的生產製程來充分提升良率與效能,以滿足兩倍光罩尺寸中介層帶來的特有挑戰。透過數個世代以來開發CoWoS平台的經驗,台積公司創新開發出獨特的光罩接合製程,能夠將CoWoS平台擴充超過單一光罩尺寸的整合面積,並將此強化的成果導入量產。

博通ASIC產品工程副總裁Greg Dix表示,該公司很高興能與台積電合作,共同精進CoWoS平台,解決許多在7奈米及更先進製程上的設計挑戰。藉由雙方的合作,我們利用前所未有的運算能力、輸入/輸出、以及記憶體整合來驅動創新,同時為包括人工智慧、機器學習、以及5G網路在內的嶄新與新興應用產品鋪路。

台積電研究發展組織系統整合技術副總經理余振華博士則指出,自從CoWoS平台於2012年問世以來,台積電在研發上的持續付出與努力,讓我們能夠將CoWoS中介層的尺寸加倍,展現我們致力於持續創新的成果。我們與博通在CoWoS上的合作是一個絕佳的範例,呈現了我們是如何透過與客戶緊密合作來提供更優異的系統級高效能運算表現。

CoWoS是台積公司晶圓級系統整合組合(WLSI)的解決方案之一,能夠與電晶體微縮互補且在電晶體微縮之外進行系統級微縮。除了CoWoS之外,台積電創新的三維積體電路技術平台,例如整合型扇出(InFO)及系統整合晶片(SoIC),透過小晶片分割與系統整合來實現創新,達到更強大的功能與強化的系統效能。

2024年先進封裝產業規模將達440億美元

先進封裝製程是當今所有半導體製造技術的核心。對所有半導體公司而言,先進封裝技術在由 5G、人工智慧和物聯網等大趨勢直接影響的產業發展方面具有戰略意義,並能確保其業務的發展。產業研究機構Yole Développement(Yole)表示,2024年先進封裝市場規模為440億美元,2018~2024年的年複合成長率為7.9%。

2018~2024年主要先進封裝製程成長趨勢 資料來源:Yole Développement(12/2020)

面對不斷變化的目標及大趨勢的影響,半導體廠商正在調整各自戰略。而半導體供應鏈及其背後的先進封裝產業也在經歷著不同層次的變革。部分廠商已經成功涉足新的商業領域,顯著影響IC產業鏈,而其他廠商則未成功。不同的廠商有不同的驅動因素轉型或拓展新業務—例如谷歌、微軟、Facebook和阿里巴巴這些軟體公司正在設計自己的處理器,以便在組裝層面獲得系統級整合/定制和供應鏈控制。

最大的變化是代工廠涉足先進封裝業務。儘管他們是該領域的新進者,但帶來的影響是顯著的:台積電在扇出型和3D先進封裝平台方面領先,提供各種產品,如InFO(及其變種)、CoWoS、WoW、3D SoIC 等。對於台積電來說,先進封裝已經成為一項成熟的業務,預計2019年其先進封裝業務的營收將達30億美元,在OSATs中排名第四。

聯電是2.5D封裝矽轉接板的主要供應商。聯電最近與Xperi合作,為各種半導體元件優化並商業化ZiBond和DBI技術。武漢新芯為影像感測器和高性能應用提供3D IC TSV封裝方案。整體而言,這些廠商有助於將封裝從基板轉移到矽平臺。其實,不止代工廠進入先進封裝領域,IC基板和PCB製造商,如SEMCO、Unimicron、AT&S和Shinko,透過板級扇出封裝和有機基板中的嵌入式晶片涉足先進封裝領域。這些公司正在瓜分OSAT的市場,特別是先進封裝業務。

格羅方德策略聚焦 未來布局三大重點出列

近日格羅方德(GlobalFoundries)在台舉辦年度技術論壇,主題聚焦在12奈米FinFET與絕緣層上覆矽(SOI)製程的特殊應用。自從該公司宣布暫停發展7奈米製程,聚焦12奈米以上及SOI製程之後,該公司除了既有的邏輯晶圓代工業務之外,在射頻(RF)、設計服務跟先進封裝上,也有更多投入,並且將組織調整為車用/工業與多重市場、行動與無線基礎建設、運算與有線基礎建設三大部門,顯然退出先進製程的競爭行列,反而讓格羅方德有資源專注在生態系統的培養跟建構上。

格羅方德亞洲區業務開發總裁Americo Lemos(圖)表示,格羅方德雖然宣布退出先進製程的競逐行列,但這不代表公司不再繼續投資未來。事實上,12奈米以上的成熟製程節點,還是有龐大的市場需求跟多樣化的客戶存在,把這個領域耕耘好,還是有很多發展機會。所以,關鍵在於格羅方德是否備妥能滿足這些客戶需求的技術。

格羅方德亞洲區業務開發總裁Americo Lemos表示,SOI等成熟製程,在未來仍將有很龐大的應用潛力。

不管是高效能運算(HPC)或嵌入式物聯網應用,未來市場的需求趨勢其實很明顯--追求更高的能源效率。但現在光靠電路微縮,已不一定能帶來這個效益。從能源效率的角度來看,SOI的表現往往比標準CMOS來得更優異,這也是格羅方德22奈米FDX製程廣獲客戶採用的主要原因。

在這個基礎上,格羅方德將持續投資在12奈米FDX製程上,以滿足客戶對邊緣運算的強勁需求。Lemos認為,由於12奈米FDX的功耗表現可以比其他同業的10奈米FinFET還優異,因此在能源效率更受重視的未來,12奈米FDX會有很長的產品生命週期。

不過,在SOI領域,一些重要的研究機構如CEA-Leti,已經開始研究如何將SOI推向10奈米以下,這是否會影響格羅方德在SOI製程上的領先地位?Lemos認為還不至於。CEA-Leti等SOI技術研發領域的要角,都是格羅方德的長期夥伴,但研究機構的使命是不斷推進科技的極限,商業成功與否則是次要考量,而格羅方德作為一家公司,則必須在商業成功跟帶動科技進步之間取得更好的平衡點。

除了邊緣運算跟高效能運算外,射頻也是SOI一個很重要的應用市場。針對這個應用,格羅方德全球業務資深副總Juan Cordovez補充說,目前RF-SOI已廣泛應用在6GHz以下及毫米波頻段的射頻元件上,有很高的市占率。但格羅方德也在關注寬能隙材料的應用進展,如碳化矽(SiC)、氮化鎵(GaN)等,並計畫在時機成熟時切入市場。不過,目前寬能隙材料除了技術上的挑戰外,也有經濟規模不足的問題。

此外,目前半導體業內受到廣泛討論的Chiplet議題,其實格羅方德也有所準備。不過,不像其他同業或IDM業者推出一條龍的作法,格羅方德只有在必要的情況下才會自行開發跟量產,例如基於矽中介層(Si-Interposer)的先進封裝,就會由公司內部來處理。除此之外,對於大多數的先進封裝技術,格羅方德還是傾向於採取前後段合作的模式,由專業封測廠(OSAT)負責。

整體來說,格羅方德退出先進製程的競爭行列,並不意味著公司將就此停下發展腳步。相反的,由於退出先進製程的軍備競賽,公司可以騰出更多資源來發展配套,例如擴大IC設計服務團隊、開發戰略性的先進封裝技術等。同時,在公司組織上,格羅方德也因應市場變化做了調整,劃分出車用//工業與多重市場、行動與無線基礎建設、運算與有線基礎建設三大部門,以強化團隊戰力。

專訪應用材料副總裁暨台灣區總裁余定陸 搶食AI商機需要材料創新

美商應用材料副總裁暨台灣區總裁余定陸認為,科技業正面臨有史以來最大的AI大戰。在電腦運算處理器部分,人工智慧需要大量、快速的記憶體存取及平行運算,這時繪圖處理器(GPU)及張量處理器(TPU)會比傳統運算架構更適合處理人工智慧的應用。為使人工智慧潛力完全開發,其效能/功耗比需比目前方案提高1,000倍。

另一方面,為了應對大量資料跟高速運算需求,儲存資料用的記憶體、用來傳輸資料的高速介面技術等,也有許多可以發揮跟探索的空間。先進封裝技術的推陳出新,讓異質整合成為可能,不僅讓晶片業者可以在單一封裝內整合更多功能,同時也讓資料傳輸的速度大為提升。

隨著晶片的結構越來越複雜,半導體製程發展的挑戰變得更為艱鉅。但如果在材料科學方面能有新的突破,將可協助半導體製造商解決不少問題。例如在晶片內數量越來越多的矽穿孔(TSV),必須精準地打在正確的位置上,否則會形成短路。但以現在的製程方法,要確保TSV的位置正確,是一大挑戰。為此,應材已發展出可以自動對位的新材料跟對應製程方法。

最後,為了應對未來的挑戰,半導體產業的運作模式也必須跟著改變。當今的半導體產業上下游都是以直線型的方式來運作,但未來必須以網路的思維進行平行發展與學習,運用互連加速創新。每家廠商不只要面對客戶,以後還要跟客戶的客戶、客戶的夥伴攜手合作,才能發展出符合客戶需求的產品跟解決方案。

美商應用材料副總裁暨台灣區總裁余定陸認為,AI為半導體產業帶來巨大商機的同時,也帶來許多新的挑戰。

AI商機/挑戰並存 半導體材料突破將成重點

人工智慧(AI)大行其道,但若要執行相關演算法或模型,需要大量運算能力,因此對半導體產業而言,AI固然蘊含龐大商機,但同時也帶來許多挑戰。在摩爾定律(Moore's Law)逐漸失效,晶片業者不再只能倚靠電路微縮來實現效能更高、成本更低的晶片之際,AI運算需求所帶來的挑戰更形艱鉅。美商應用材料(應材)認為,為了回應這些AI帶來的挑戰,在產業生態面,半導體產業的風貌將從上下游關係分明的直線鏈條轉變成互相交錯的產業網路;在技術面,則必須在運算架構、設計結構、材料、微縮方法與先進封裝這五大領域提出新的對策,而材料工程將在這中間扮演最核心的角色。

美商應用材料副總裁暨台灣區總裁余定陸認為,對整個半導體產業來說,AI是一個完美風暴,但同時也是完美的商機。我們正面臨有史以來最大的AI大戰,不論是傳統科技領導大廠、新創公司或軟體公司,都投入大量的資源、押寶不同的技術領域、聚焦應用的客製化及最佳化,專注於硬體的設計以及投資發展。在電腦運算處理器部分,人工智慧需要大量、快速的記憶體存取及平行運算,才能提升巨量資料處理能力,這時繪圖處理器(GPU)及張量處理器(TPU)會比傳統運算架構更適合處理人工智慧的應用。 為了使人工智慧潛力完全開發,其效能/功耗比(Performance/Watt)需比目前方案提高1,000倍 ,已成為現階段技術層面亟需突破的關鍵。

另一方面,為了應對大量資料跟高速運算需求,儲存資料用的記憶體、用來傳輸資料的高速介面技術等,也有許多可以發揮跟探索的空間。過去幾年,NAND Flash已經率先從2D走向3D,接下來還有許多新興記憶體蓄勢待發。先進封裝技術的推陳出新,讓異質整合成為可能,不僅讓晶片業者可以在單一封裝內整合更多功能,同時也讓資料傳輸的速度大為提升。

而在整個半導體產業面臨如此重大變化之際,市場對半導體產品的需求其實沒有太大改變。對半導體使用者、客戶來說,最注重的還是晶片的效能(Performance)、功耗(Power)、面積成本(Area Cost, AC),也就是應材常說的PPAC這三大指標。為了滿足客戶對產品的需求,應材認為,材料科學的突破是最關鍵的。

隨著晶片的結構越來越複雜,半導體製程發展的挑戰變得更為艱鉅。但如果在材料科學方面能有新的突破,將可協助半導體製造商解決不少問題。例如在晶片內數量越來越多的矽穿孔(TSV),必須精準地打在正確的位置上,否則就會形成短路。但以現在的製程方法,要確保TSV的位置正確,是相當有挑戰性的課題。為此,應材已發展出可以自動對位的新材料跟對應製程方法,可協助半導體製造業者解決這項難題。

最後,為了應對未來的挑戰,半導體產業的運作模式也必須跟著改變。當今的半導體產業上下游都是以直線型的方式來運作,互連性十分薄弱,但未來必須以神經網路形態(Neuromorphic)的思維,進行平行發展與學習,運用互連加速創新。每家廠商不只要面對客戶,以後還要跟客戶的客戶、客戶的夥伴攜手合作,才能發展出符合客戶需求的產品跟解決方案。

先進封裝2023年產值達390億美元

2017年是半導體產業史無前例的一年,市場成長率高達21.6%,促使產業規模膨脹達創紀錄的近4100億美元。在這種動態背景下,先進封裝產業發揮關鍵作用,根據產業研究機構Yole Développement(Yole)最新研究指出,2023年先進封裝市場規模將達到約390億美元。

從2017年到2023年,整個半導體封裝市場的營收將以5.2%的年複合成長率(CAGR)成長。仔細分析其中差異,先進封裝市場CAGR將達7%,另一方面,傳統封裝市場CAGR僅3.3%。在不同的先進封裝技術中,3D矽穿孔(TSV)和扇出型封裝(Fan-out)將分別以29%和15%的速度成長。構成大多數先進封裝市場的覆晶封裝(Flip-chip)將以近7%的CAGR成長;而扇入型晶圓級封裝(Fan-in WLP)CAGR也將達到7%,主要由行動通訊應用推動。

先進半導體封裝被視為提高半導體產品價值、增加功能、保持/提高性能同時降低成本的一種方式。無論如何,更多異質晶片整合,包括系統級封裝(SiP)和未來更先進的封裝技術都將遵循此趨勢。各種多晶片封裝技術正在高階和低階應用同時開發,用於消費性、高速運算和專業應用。