技術頻道

- Advertisement -

有效降低氮化鉭層電阻 鈷助力先進製程效能提升

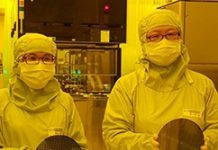

現今隨著摩爾定律,半導體7nm先進製程已經進入量產的階段。從材料工程來看,針對電晶體接點與導線的重大金屬材料變革,是解除7nm以下先進製程效能瓶頸的關鍵。因此,電子產品驗證測試實驗室如宜特科技開始實測已量產的7nm晶片,解析鈷在7nm半導體製程扮演的角色(圖1)。

圖1 IC結構示意圖

降低RC Delay 提升晶片運行速度

在積體電路中,電阻-電容延遲時間(RC Delay)是影響半導體元件的速度或性能的重要參數之一。隨著半導體製程推進至7nm,不僅金屬連線(Interconnect)層數越趨增加,導線間的距離也不斷微縮;當電子訊號在層數多的金屬連線間傳送時,其產生的電阻-電容延遲時間將嚴重減低半導體元件的速度。如何降低電阻-電容延遲時間、增加半導體元件運行速度,是重要課題。

IC製程微縮 阻障層電阻相對增加

銅和鋁(Al)是半導體後段製程(BEOL, Back End Of Line)金屬連線最常使用的金屬材料。銅由於導電性較鋁好,主要被用於先進製程的金屬連線;但銅原子在介電層的擴散係數遠比鋁原子大,為防止銅擴散在介電層造成線路短路,因此在半導體製程上必須使用更緻密的氮化鉭(TaN),取代柱狀晶結構的氮化鈦(TiN)以避免銅擴散。

然而,氮化鉭比氮化鈦的電阻係數大,相差十倍以上(表1),使用氮化鉭為銅的阻障層,將有使金屬連線電阻增加的風險。

金屬線上的電阻為銅線電阻加氮化鉭層電阻的總和。銅線尺寸大時,氮化鉭層引起的電阻增加比例不大,可忽略不計。但當晶片微縮到非常小,使銅線尺寸逐漸縮小時,氮化鉭層貢獻的電阻比例就愈來愈大。當使用並聯電阻簡化計算氮化鉭層電阻貢獻度時,銅線橫截面尺寸由200nm降到20nm,此時氮化鉭層電阻貢獻度增至大於40倍(表2)。

然而在銅製程中,因銅容易擴散的特性,不能藉由降低氮化鉭層的厚度來減少電阻,否則就會失去阻障功能。因此在7nm IC製程中,使用新材料取代銅導線或阻障層成為重要課題。

降低晶片電阻 金屬材料為選用關鍵

如何降低氮化鉭層電阻的關鍵在於調整該層金屬材料。經過研究發現,鈷是加入氮化鉭阻障層的極佳候選材料,不但可以降低阻障層電阻,而且可以降低阻障層的厚度。

雙層接觸窗設計 使鈷發揮最大效能

金屬導線和矽基板上半導體元件間的連結為接觸窗(Contact),靠鎢(W)來連結,其阻障層材料是氮化鈦。

在銅金屬化製程中,為降低W/TiN接觸窗的電阻,鈷成為最佳候選者。但若用鈷完全取代W/TiN直接與銅接觸,則兩者容易固溶在一起,造成金屬導線電遷移性能變差,因此出現雙層接觸窗的製程。在剖析使用鈷的原因後,針對晶片製程進行實測。

前期樣品製備作業

進行測試時,為執行分析7nm製程產品而採購市售手機,取得Kirin980 CPU。因CPU封裝於手機電路板上,因此須先拆解(Tear down)相關部品,以及結構觀察的分析工程,包括X光分析、去錫球、去封裝、去膠、紅外線定位、研磨、吃酸、CPU/DRAM雙晶片分離等技術,最後再取得晶片。

利用TEM實際觀察金屬阻障層

以穿透式電子顯微鏡(Transmission Electron Microscope, TEM)搭配高性能的能量散布X射線譜術(Energy-Dispersive X-ray Spectroscopy, EDS/EDX),藉此解析7nm晶片的前段製程(Front End Of Line, FEOL)及後段製程。

透過TEM及EDS觀察晶片結構中第一層(M1)與第二層(M2)金屬層,解析7nm的鰭狀電晶體(FinFET)、閘極(Gate)、接觸窗(圖2),與相對應鈷及鎢(圖3)的成分分布。

圖2 STEM HAADF影像,顯示鰭狀電晶體、閘極、接觸窗、M1和M2等結構。

圖3 圖中深色區為鈷(Co)成份,淺色區為鎢(W)成份,對照圖二,即可了解鈷和鎢在結構中分布情形。

透過比較觀察到鈷成為接觸窗及阻障層材料,且包覆整個第一層(M1)銅金屬層結構,成為阻障層材料。但Co沒有完全取代接觸窗的W/TiN,可能是因為接觸窗製程與阻障層製程使用不同類型製程,造成Co與周圍材料反應狀況不同,致使接觸窗的Co無法完全取代W/TiN。

將從底材到第八層金屬層的結構圖(圖4)與相對應的成分分布圖(圖5)對照可了解鈷除用在接觸窗下層,也使用在第一層到第四層金屬層的阻障層。除此之外也可發現,鎢除了使用於接觸窗上層,亦用於閘極上。

圖4 STEM HAADF影像,顯示鰭狀電晶體、閘極、接觸窗、M1和M2等結構。

圖5 圖中深色為鈷成份分布,淺色為鎢成份分布。對照圖4,即可了解,除了接觸窗上層,鈷使用在第一層到第四層金屬層。

自平面(Plan-View)觀察接觸窗深入晶片結構

進一步研究平面及俯視影像觀察接觸窗的結構,該實驗室平面式TEM試片製備比一般橫截面TEM試片製備繁複,但皆可用FIB(Focus Ion Beam)機台製備。

從平面影像觀察接觸窗結果(圖6及圖7)可見鈷為長條型,鎢接近圓形或橢圓形狀(圖7)。一個鎢分布在一條縱向長條型鈷上,橫向鈷連接兩條縱向長條型鈷。有些長條型鈷上沒有鎢。此區域長條型的鎢分布在閘極上,非用於接觸窗。

圖6 STEM...

新材質加持 電子產品散熱管理更高效

不言可喻,此趨勢浮現許多必須克服的技術障礙,尤其是如何應對不斷攀升的熱密度。散熱管理從前被認為只是設計過程中最後一個考量的因素,但現正成為需要搏得更多關注的基本要素。在本文中將先研究散熱管理相關問題,進而重點介紹有助於設計師採最小空間實現最大限度散熱的具體創新技術。

通常情況下,散熱管理實施不會在設計早期就得到解決,而是保留到最後一分鐘,主要是透過簡單添加散熱片或風扇處理,以達到可接受結果。由於系統功率需求通常在設計完成之前才會最終確定,上述做法在某種程度上可以理解,但現代產品開發流程則要求對散熱特性給予高優先順序考量。

幾乎所有現代電子設計皆被寄望增加更多功能,並減少設備尺寸及重量;無論是行動裝置、伺服器或無人駕駛飛行器/無人機等皆是。這些產品的核心半導體晶片仰賴新的製程,具更高能效,進而產生更少熱量。此外,採用智慧電源管理系統還可充分利用電源電能,例如在平常多數時間關閉周邊設備僅在實際需要時才開啟電源。然而在許多設計中,還是需要強制性的某種形式散熱管理,這將涉及使用散熱器或類似散熱機構。

使用散熱器時,有兩個關鍵考量因素:

1.將散熱器與生熱裝置進行散熱連接,確保高水準傳熱。

2.最大化散熱器單位體積的表面積,使其更高效散熱,不會增加PCB占位面積或厚度。

填充間隙以改進散熱性能

為了能高效散熱,在發熱點(通常是半導體接面)和周圍環境間必須有良好散熱通道,以消耗多餘熱量。在半導體元件中,從接面到外殼的散熱路徑由製造商最佳化。潛在的薄弱環節是散熱器實際連接到設備主體之處。雖然這兩個接合面肉眼看來可能是平的,但通常會有一些翹曲,尤其是在較大的散熱片中,且每個表面都有微孔(包含小的氣穴)。由於空氣是絕緣體,因此這些微孔應填充更好的導熱材質,進而改進傳熱並消除可能熱點。有許多材質可實現,包括液體、油脂及襯墊。

然而,最方便的高性能解決方案之一是Bergquist的Gap Pad技術,有許多類型襯墊用於不同應用,Gap Pad 5000S35為增強型玻璃纖維填料和聚合物襯墊,具有特別高的熱傳導係數(Thermal Conductivity)。兩側固有的自然黏性有助於將材質應用於表面,允許產品有效填充氣隙以增強整體散熱(圖1)。

圖1 Bergquist的間隙墊有助於顯著提高散熱性能。

這種軟性材質具5W/m-k的高熱傳導係數,可在保持架構完整性時,將襯墊應用於複雜和苛刻輪廓,而不會對易碎的元件引線施加任何應力。增強型玻璃纖維材質便於處置,同時提高抗撕裂性,並將電氣絕緣提高到5000VAC以上。Gap Pad以板材形式提供,也可以提供模切以適合標準設備輪廓。

其他材質也可提供,如Gap Pad EMI 1.0,同樣出自Bergquist,不僅提高熱傳導係數,還可吸收電磁能量,有助於降低電磁干擾(EMI)影響。

微孔架構改進散熱功能

散熱器有多種尺寸和形狀可供選擇,通常設計為適合標準半導體封裝,尤其適合功率元件外形。許多公司委託客制散熱器設計,如果在初始設計流程中沒有解決熱管理問題,不是適合特定應用,就是允許將散熱器安裝到剩餘可用空間。

雖然許多散熱器可與強制空氣冷卻組合使用,以最大限度提高性能,但此方法可能存在缺陷。近年來由於設計及材質改進,以及新驅動技術出現,風扇壽命有所延長;然而與固態電子元件相比,工作壽命仍然相對較短。如果沒有足夠過濾,風扇會將灰塵吸入設備,而導致過早故障。因此,工程師通常傾向被動冷卻,但前提是可達足夠高散熱性能。

總體而言,用於被動冷卻的散熱器體積大且笨重,以便毋須使用強制空氣時也能提供足夠冷卻來散熱。然而,來自Versarien公司的創新材質使被動式散熱器外形尺寸較傳統材質小。由利物浦大學開發的VersarienCu能夠模擬自然界中常見架構,構建具有精細、開放、相互連接微孔的金屬材質,適用於熱傳導應用,可提供達6℃/W的散熱器性能,超越同樣尺寸的傳統散熱器。此外,其固體銅泡沫塗覆有薄硬的高溫氧化銅層,提升熱輻射率、改進熱輻射,於小空間實現更多冷卻。

散熱管理為當代設計流程核心,因尺寸更小、功能更強的設備會產生更多熱量,但卻沒有足夠空間散發熱量。新材質技術將與半導體製程同步運作,滿足尺寸更緊湊、功能更集中的電子設備硬體不斷提高的需求。

(本文作者任職於貿澤電子)

ATE設備需求不斷演進 電源功率/雜訊/重量要求更嚴

也因為ATE橫跨了自動化與測試儀器兩個領域,因此從電源設計的角度來看,ATE是一個相當具有挑戰性的應用。對測試儀器來說,電源的電磁干擾(EMI)常常是無可妥協的規格要求,因為測試儀器往往非常靈敏,儀器內任何元件所發出的電磁波訊號,都可能會影響量測所得的數據。

半導體測試所使用的ATE設備,還有許多其他ATE設備所沒有的特殊設計挑戰。隨著IC的接腳數量不斷增加,出於成本考慮,每分鐘所測試的晶片數量也必須增加。這需要對測試設備的硬體進行大幅調整。測試頭本身必須測試更多接腳,必須更快移動,而且還必須提供不同的測試電壓。

測試頭的尺寸和重量是實現這些改進至關重要的因素。即便電源具有更高效率及更小尺寸的相同拓撲,也會造成元件的更高工作溫度,因而可能會降低可靠性,這是一天24小時全天候運行的系統所無法接受的。

至於在電池化成系統(Battery Formation System, BFS)方面,因為這類設備所面對的電池組容量越來越大,因此在執行電池化成或其他電池測試相關工作時,需要消耗的電力也越來越多。這意味著電池化成系統必須能對電池組輸出更高功率,且必須設法將這些電力回收再利用,否則電池化成或電池測試的成本將會大幅提升。

分比式架構解決效率/EMI難題

分比式電源架構(Factorized Power Architecture, FPA)使客戶減小了負載本身各轉換級的尺寸、重量以及熱量的產生。所謂的分比式電源,是將穩壓(PRM)與變壓(VTM)分開,並在負載點上只提供變壓部件(圖1)。

圖1 分比式電源架構

與傳統電源架構相比,FPA不僅可明顯降低負載點所產生的功耗,而且還可顯著縮小轉換器的尺寸。穩壓模組本身則可配置在遠離負載點的另一端,因為穩壓元件通常會產生比較大的雜訊,若能讓穩壓元件遠離負載點,亦可幫助ATE設備開發者解決棘手的電源雜訊問題。

VTM支援高開關頻率,因而支援極高的功率密度,是非常小巧的羽量級組件。這是用來減輕測試頭(Test Head)重量的主要組件。VTM極高的效率不僅降低了測試頭上所生成的熱量,而且還確保滿足了這種環境下所需的高可靠性及平均故障間隔時間(MTBF)值要求。

FPA透過對PRM母線電壓的調整實現對負載電壓的穩壓。在測試具有不同電壓需求的晶片時,這可避免高昂的設定成本或更換設備。此外,目前絕大多數的半導體ATE設備,內部電源分配網路所使用的電壓都還停留在24V,這意味著從測試設備本體到測試頭之間的電源纜線必須承受相當大的電流,才能滿足測試頭的功率需求。

而隨著晶片設計越來越複雜,待測晶片的接腳數量、測試點持續增加,測試頭所需支援的測試通道數將只會越來越多,功率需求也跟著水漲船高,如果不設法提高電壓,ATE設備商只能換用更粗的電源纜線,才能承受更大的電流。這不只會增加成本,也會增加重量,這是許多ATE設備開發者所不樂見的。

FPA亦可協助設備開發者導入更高的電壓。以Vicor提供的解決方案為例,因為Vicor的PRM輸出電壓可以設定在48V或更高(通常不會高於60V,因為若超過60V,設備需要重新設計才能滿足電氣安規的要求),因此從測試設備本體到測試頭之間的電源纜線可以換用更細的纜線,以降低成本、減輕重量。或是當測試頭的功耗需求增加時,設備業者可以沿用現有的纜線,不必更換更粗的纜線,造成成本跟重量上揚。

圖2是一個基於Vicor解決方案的高速SoC測試設備所採用的電源樹架構。這個電源系統對測試頭提供的總功率約在2.24kW左右,並支援多種不同的電壓/電流組合,展現出Vicor電源模組的效率跟配置彈性優勢。

圖2 基於Vicor電源解決方案的高速SoC測試機內部電源方塊圖

高壓直降挑戰大 SAC拓撲解難題

在維持同樣功率水準的前提下,只要提高傳輸電壓,就能降低纜線上的電流,減少傳輸損耗,這對工程師來說是很基本的電學知識,但事實上,因為負載點需要的輸出電壓是固定的,甚至還有越來越低的趨勢,拉高傳輸電壓反而會使負載點電源的輸入跟輸出壓差變得更大。

在這個情況下,負載點電源如果採用傳統的硬開關切換電源拓撲,反而會出現更嚴重的振鈴現象,不僅降低轉換效率,還會增加電源雜訊。是故,若要在ATE設備內的配電網路採用更高電壓,負載點電源的拓撲必須採用新的設計架構。

穩壓準諧振(ZCS/ZVS)跟正弦振幅轉換(SAC)拓撲,就是為了解決這個問題而產生的拓撲設計。其中,SAC因為是基於正弦波的轉換,因此效率跟雜訊表現比ZVS還要更優異,更適合運用在靠近負載點的負載點電源上。SAC的拓撲架構如圖3所示,與穩壓準諧振ZCS/ZVS轉換器不同,正弦振幅轉換器工作在固定頻率下,該頻率與一次側槽路的諧振頻率相等。

圖3 SAC拓撲架構

一次側槽路的開關FET 鎖定至該電路的自然諧振頻率下,在零交叉點位置切換,消除了切換功耗,帶來效率提高的優勢,並顯著減少了高階雜訊諧波的產生,降低輸出電壓濾波的需求。一次側諧振槽中的電流為純正弦波,而不是前幾代轉換器中的方波或部分正弦波。這不僅有助於降低諧波含量,而且還可提供更乾淨的輸出雜訊頻譜。

在正弦振幅轉換器中,一次側的漏感最小,因為它不是關鍵的儲能元件。因此,SAC可以在更高的頻率下工作,不僅允許使用更小的變壓器,而且還可提高功率密度和效率。Vicor BCM工作在數MHz的頻率下;無論負載如何,該頻率都不變。對於二次側上增加的負載,正弦振幅轉換器的回應方式是增加一次側諧振槽上的正弦電流幅度。

這反過來又能增加耦合在二次側中的能量,抵消增加的負載。當負載電流降低時,在「空載」條件下,正弦幅度降低至接近零。

Vicor匯流排轉換器的輸出阻抗極低,反映了變壓器一次側諧振槽電路的低輸出阻抗,理想情況下,其在諧振頻率下為零阻抗。該阻抗基本上是平坦的,約為諧振頻率的三分之二,約為常規IBC輸出阻抗的一半。

一次側電流的正弦屬性帶來了其在SAC電氣雜訊特性方面的優勢。在切換頻率以及兩倍的切換頻率下,輸出雜訊頻譜非常窄,具有各種元件(由於輸出的全波整流)。輸出濾波很容易透過小型高頻率陶瓷電容實現。

降低電池化成成本 雙向電源至為關鍵

至於在電池化成系統方面,由於電動車、再生能源儲能的蓬勃發展,目前市場上最主要的電池化成系統,都是針對鋰電池設計。鋰電池芯的化成是電池的初使化,使電池芯的活性物質活化,是一個非常複雜的過程,同時也是影響電池性能很重要的一道工序。

在鋰電池第一次充電時,鋰離子第一次插入到石墨中,會在電池內發生電化學反應。在電池首次充電過程中,不可避免地要在碳負極與電解液的相介面上形成覆蓋在碳電極表面的鈍化薄層,稱之為固體電解質相介面或稱SEI膜(Solid Electrolyte Interface)。當SEI膜穩定之後,電池就可以進行多次充放電循環。

換言之,從電力電子的角度來看,電池化成系統就是一個大型的自動充電系統,且隨著電池組的容量越來越大,進行電池化成時所需提供給電池組的功率也越來越高。

這會衍生出兩個問題:一、化成系統如何提供給電池組足夠的電力?二、化成的主要目的是產生穩定的SEI膜,而不是幫鋰電池充電,因此在化成步驟完成後,如何將儲存鋰電池裡面的電力循環利用,幫下一批電池進行化成,降低化成的成本?

第一個問題其實跟前面提到的ATE設備有些類似,因為電池組內包含的電池芯數量增加,因此化成設備對電池提供的功率必須跟著增加,但在電壓不變的情況下,化成系統內所使用的纜線必須承載更大電流,因此造成成本上升。而且,使用更粗的電源纜線會讓化成系統內的配線變得更困難,因為纜線變粗之後,會更難以撓折,走線設計得花更多功夫。

因此,如果能提高配電網路的電壓,直到要對電池芯充電時才將高壓直流電轉換成低壓、大電流的直流電,會為化成系統設計帶來很高的彈性。圖4是傳統電池化成系統電源架構跟Vicor提出的架構比較,很明顯可以看出Vicor提出的方案,能幫電池化成系統製造商省下許多纜線的成本。

圖4 傳統電池化成系統架構與Vicor提案架構的比較

第二個問題則涉及到電源轉換模組是否支援雙向轉換,不支援雙向轉換的電源解決方案,若要實現電力的循環再利用,會需要另外設計一套電池放電子系統,才能把電力從化成完畢的鋰電池芯裡抽取出來。從圖4可以看出,針對電池化成系統,Vicor提供的轉換模組方案都支援雙向轉換,不像傳統架構僅支援單向轉換,這可以大幅簡化系統設計的複雜度。

提高機台效率/降成本 電源設計需翻新

ATE設備屬於工業設備,在這個行業中,最普遍的配電電壓規格是12V與24V,因此,許多工業用電源解決方案,都是環繞著12V或24V規格而設計,自成一個生態圈。而48V是通訊設備產業的主流配電規格,也有一個屬於自己的生態系統。

但在自動化測試設備或電池化成系統需要更高輸送量,以增加生產效率,降低成本的情況下,ATE設備內部的電源架構,已經到了必須往上再拉高到48V的時刻。類似的轉換過程在資料中心相關設備,例如伺服器領域,已經是現在進行式,有越來越多伺服器業者開始推出基於48V配電的產品,相信類似的情況現在也正在ATE設備領域發生。

(本文作者任職於Vicor)

推動5G部署 多樣射頻半導體技術展妙用

儘管這些令人振奮的發展還未到來,但5G部署正在發生,速度遠超想像。例如,2018年底5G的毫米波頻譜拍賣就已開始,目前仍在進行;5G技術標準制定過程已基本完成;Verizon和AT&T已經在美國特定地區推出使用毫米波的固定無線服務,作為行動毫米波5G的先驅,而中國計畫在2019年部署20萬個5G基站,日本、韓國和瑞士也積極成為早期採用者;此外,5G所需的資料中心、網路基礎設施、用戶端設備(CPE)和行動系統也在大力發展。

因此,預計未來幾年的網路流量將呈指數成長。估計到2024年,行動資料流量的年複合成長率將達31%,年度全球行動資料流量每月約為136艾位元組(Exabyte),其中5G約占25%。此外,隨著新應用需求出現、用戶增加,越來越多的用戶參與傳輸和處理大量資料的活動,如高解析影片,流量不斷成長的同時,複雜性也會增加;體育、音樂會及其他活動的現場直播、串流式影片服務等。

5G催動半導體射頻技術演進

面對流量、複雜性和智慧手機5G化挑戰,架構更改勢在必行。而對於這些應用的晶片設計者來說,必須打造出射頻、功耗和性能優化的設備,才能使產品脫穎而出。隨著5G應用的發展,還必須在設計和製造生態系統中降低這些晶片的生產成本,說明晶片快速上市,從利用現有4G/LTE架構和6GHz以下頻段的初始設計,到針對毫米波頻率架構的設計。

為此,晶圓代工業者如格芯(GlobalFoundries)為智慧手機晶片設計者提供一系列久經考驗的創新型射頻技術,隨時可用於5G部署且具有廣泛的特性、功能和能力,可以不同方式組合,創建5G應用所需的特定屬性。

本文將探討格芯技術對智慧手機和其他移動設備5G部署的貢獻。首先討論6GHz以下頻率應用的晶片設計方法,充分利用部分現有4G頻段(700MHz、2.5GHz等)以及3.3GHz至5GHz頻段來實現5G。該頻率範圍內的晶片開發通常包括設計「改進」,而不是全部重新設計。因此,第一代5G智慧手機主要基於6GHz以下。

本文將探討在24GHz以上頻率毫米波(mmWave)頻段中的5G應用。這些頻段資料傳輸速率極高,但需要將多根天線組合成天線陣列,以擴展毫米波的覆蓋範圍。最後將討論Wi-Fi前端模組,因為Wi-Fi功能如今已包含在與5G系統交互的各種設備中(例如智慧手機、平板電腦、筆記型電腦、桌上型電腦、可穿戴設備和路由器)。

8SW RF SOI技術實現6GHz以下部署

在射頻電路設計中,射頻前端模組(FEM)通常包括天線與射頻收發器(發射器/接收器)之間的所有元件。包括處理從天線接收的訊號所需的開關、濾波器和低雜訊放大器(LNAs),以及透過濾波器和開關放大發送到天線的訊號的功率放大器(PA)。

對於6GHz以下的蜂窩架構,FEM是混合型,意味著使用多種技術,以便為每個元件帶來獨特的優勢,如圖1所示。GaAs用於PA,而RF SOI用於開關,SiGe或RF SOI都可用於LNA。

圖1 6GHz以下智慧手機蜂窩前端和收發器

格芯的8SW RF SOI技術採用300mm晶圓製造的全面認證高容量RF SOI代工解決方案。該解決方案經過優化,可為用於高階4G-LTE和6GHz以下5G應用的FEM中的LNA、開關和調諧器提供優異性能。

該技術基於含有大量陷阱、全銅互連、優化的金屬堆疊和MIM電容的高電阻襯底,提供較佳的導通電阻和關斷電容,可實現高隔離性能,大幅降低插入損耗(IL)和諧波。降低插入損耗是智慧手機原始設備製造商(OEM)和蜂窩網路運營商的關鍵需求,因為更低的IL會產生更強的訊號,進而減少通話斷線/斷開連接現象,提高資料速度,尤其是蜂窩邊緣。使用此一技術製造的開關在隔離性能和線性度上優於其他產品,這意味著更高的接收器靈敏度和更少的干擾,同樣會減少通話斷線/連接/串擾,最終改善用戶體驗。

另外,6GHz以下蜂窩智慧手機架構通常使用獨立收發器,直到最近,這些收發器都建立在28nm的CMOS技術上。現在,業界正在向更高性能的FinFET技術發展,使得5G系統能夠處理更多數位內容,並充分利用功耗較低的類比電路。

45RFSOI 技術滿足毫米波前端模組設計

毫米波頻段中的5G架構正在不斷發展,因此前端模組設計因客戶而異。

以FEM為中心的設計選項之一是部分整合方法,其中整合了毫米波PA、LNA、開關、移相器、功率合成器/分相器,某些情況下還有RF/毫米波上/下變頻轉換器。這些轉換器將毫米波從中間頻率(IF)轉換為高於6GHz但遠低於毫米波水準(反之亦然)。訊號通常處於7~12GHz的範圍內。這被稱為「高IF」架構,利用了IF頻率(而不是毫米波頻率)下FEM和收發器之間的較低互連損耗。選擇IF頻率是為了不干擾同一手機中的其他6GHz以下訊號。

另外一種整合方法是使PA保持獨立,而不是與其他FEM元件(LNA、開關、移相器和功率合成器/分相器)整合在同一晶片上。另一個以FEM為中心的設計選擇是完全整合的方法,其整合了包括收發器在內的整個子系統,但不包括數據機介面。

選擇使用獨立FEM模組的毫米波的客戶需要大功率高RF性能的PA,為此,可使用45RFSOI製程;透過增加以RF為中心的增強功能,利用久經驗證的45nm部分耗盡型絕緣體上矽(PD-SOI)技術的固有優勢,並可提供更佳的毫米波FEM性能。優勢包括:

.用於高線性度開關的高電阻率襯底、LNA以及毫米波頻率下的低損耗互連。

.高High ft/fmax(290/410GHz)和堆疊能力的PA,具有更高的最大輸出功率(Psat)和功率增益,效率更高;高功率容限開關,提供低插入損耗(0.65dB5)

.經優化的低損耗後段制程(BEOL)製程,提供低雜訊係數(NF)LNA(1.3 dB5)和低損耗互連,以及移相器和功率分相器/組合器等被動元件。

另外,使用45RFSOI製程可以實現更高的Psat和更低的NF,進而增加PA的功率附加效率(PAE),減少實現給定等效全向輻射功率(EIRP)輸出所需的天線列陣元件數量。這意味著更少的電池電量消耗和更好的熱管理。PA功率效率和熱管理至關重要,因為電池壽命是行動設備的關鍵要求,同時風扇或散熱器無法適應越來越輕薄的行動設備。此外,所需的陣列元件越少,天線模組就越小,最終降低封裝成本。該技術同樣非常適合毫米波5G小型蜂窩中的整合式FEM,因為它提供獨特功能,可設計Psat高達23dBm且最高效率>40%的晶片。

除了上述所提,還有22FDX製程可實現全整合5G毫米波無線解決方案。

與bulk CMOS技術相比,採用22FDX技術構建的功率放大器可節省34%的發射功耗和14%的總功耗,延長10%的電池使用時間並減少熱量。此外,22FDX不需要PA功率合成器,即可實現PA的完全整合,並縮小元件尺寸,提高效率。

在LNA性能方面,22FDX的雜訊係數比CMOS提高約30%,實現更佳的訊號覆蓋範圍和更少的通話斷線率。據估計,22FDX可將覆蓋距離增加約6%。此外,22FDX的開關性能至少比CMOS提高50%,同樣可增強訊號,減少通話斷線。這相當於將靈敏度提高了0.85dB,鑒於設計人員通常需要爭奪數十分之一dB的插入損耗差異,這一優勢尤為突出。

Wi-Fi 功能增加增添設計難度

多年來,Wi-Fi前端的功能不斷增加,以滿足Wi-Fi設備技術標準(例如802.11 a/b/g/n/ac)不斷成長的性能要求。最新的Wi-Fi標準是802.11ax,涵蓋2.4、5.8GHz以及新興的6GHz頻段,最高可達7.125GHz頻率範圍。

如圖2所示,Wi-Fi無線電架構各不相同。它們可能包括獨立的FEM和收發器,或整合式FEM和收發器,有時還包括整合式數據機。

獨立的Wi-Fi FEM可以是帶開關+PA+LNA的整合模組(圖2中的小點線框),也可以是帶有單獨分立PA的開關+LNA。8SW技術旨在為Wi-Fi開關+LNA提供更佳解決方案,同時實現與前面提到的蜂窩開關相同的性能優勢。此外,8SW經過優化,可在基於RF SOI的LNA中提供令人滿意的低雜訊、高增益和高線性度優勢。

圖2 2×2 MIMO的Wi-Fi模組原理圖

對於高性能分離PA,一些設計人員會選擇砷化鎵(GaAs)。而別的設計人員通常會採用整合方法;而SiGe BiCMOS功率放大器技術可說明他們在性能、整合和成本效率之間取得最佳平衡;而SiGe PA技術則基於矽基板,與砷化鎵替代品相比,性能相似但模組更小,因此具有整合優勢。所有SiGe PA產品均採用經過生產驗證的矽穿孔(TSV),可實現低成本封裝解決方案。

總結來說,晶圓代工者提供廣泛的差異化RF技術,幫助整個5G行業實現強勁成長。無論是6GHz以下應用、mmWave 5G應用,還是先進的Wi-Fi無線電,這些多樣化的技術都能為5G解決方案帶來特定的益處,幫助設計人員打造優化5G性能的設備,並在功率、性能、RF功能和特定應用功能之間取得平衡。

(本文由GlobalFoundries提供)

巧扮連通橋梁 AIB實現晶片/小晶片高速互連

然而,涉及晶片橋、中介層、侵蝕性幾何形狀(Aggressive Geometries)和微米級微凸點連接的新整合技術已經改變了演算法。戈登‧摩爾曾在1965年指出:「使用獨立封裝並彼此互聯的更小功能來構建的大型系統可能更為經濟。」

如今許多SoC在內核處理方面彼此相似,而特定的週邊功能卻有所不同。有的應用可能需要視覺處理;有的應用需要直接從天線獲取訊號;而有的應用需要SoC提供更多的記憶體。將這些功能分離可獲得一定的價值,比如混合搭配不同的功能,但另一個重要價值是每個功能,像是處理、類比、記憶體、數位訊號處理(DSP)等,可以在另一個不同於內核運算所用的流程上得到更好的優化。

鑒於這些功能是相互分離的(在小晶片或Tile上實施),因此我們面臨的挑戰是在保持與單晶片接近的性能和功耗的同時,將這些功能全部整合到單個封裝。透過將高級介面匯流排(AIB)與支援將多個晶片異構整合到單個封裝的封裝技術相結合,可以輕易解決這個問題(圖1)。最近發布的AIB互連方案為晶片和小晶片互連提供了一種快速、靈活且有助於輕鬆布局的方法。本白皮書介紹了AIB的高級特性和用途,並將展示各種AIB功能如何支援大規模設計和實現可靠的高速連接。

圖1 AIB應用的一個示例,其中類比前端、訊號預處理和SERDES全部通過AIB連接到FPGA實現分類和物件追蹤。

AIB目標

在過去25年中,設備到設備介面使用複雜電路透過幾根電纜實現高速傳輸;PCI Express就是其中一個例子。AIB使用全新高密度封裝技術所支援的超寬平行介面,並一舉扭轉了這一趨勢。透過以相對較低的速度運行介面的每條電纜,可以簡化每個發送器和接收器的電路,並占用很少的晶片區域。

AIB將資料從一個小晶片上的微凸塊移動到另一台相鄰設備上的微凸塊。全新高密度封裝微凸塊的間距很小,進而減少了介面所需的空間。與使用間距130或150微米的凸塊的標準倒裝晶片封裝相比,高密度封裝技術通常支援間距為55微米的微凸塊。

與只能合理使用幾百根線路的傳統介面(如採用標準技術的DDR記憶體)相比,這種小間距允許單個AIB介面支援數千個訊號。單個AIB資料線的時鐘頻率為GHz,並具有多個配置和速度選項,以確保AIB可以支援各種應用。

儘管AIB沒有指定最大時脈速率,並且最小速率非常低(50MHz),但AIB卻能夠在高頻寬下運行,每條資料線的典型資料速率為每秒2Gb。每個小晶片都記錄了其預期的時脈速率範圍,以便選擇不同設備的設計人員可以確保它們以相容的速度運行。通常,時鐘的工作頻率常在1GHz或以下,但只要介面的兩端都支援更高的速度,系統便可以支援。

AIB是一種實體層(PHY)規範(圖2);它占據了OSI參考模型中的最低級別。它的一側連接到單獨晶片或小晶片上的相應AIB介面;另一側連接到媒體存取控制器(MAC)。它僅用於從MAC中獲取資料並將其發送到連接的晶片,或者從連接的晶片接收訊號並將訊號傳遞給MAC。

圖2 AIB是一種實體層規範。

焊墊(Footprint)被設計為在微凸塊間距的範圍內盡可能小。訊號被聚集在一起,以便更有效地利用晶片的邊緣(稱為海岸線),並提供快速且較短的低偏差訊號線。對於AIB Gen1,由於AIB介面中每條資料線的資料速率為2Gbps,因此避免了訓練和訊號調節(例如均衡和預加重),以保持較小的電路尺寸。業界常見的微凸塊間距為55微米,隨著技術的發展,未來的AIB支援低至10微米的微凸塊間距。

AIB配置

AIB有兩種基本配置。AIB Base適用於需要最少電路的羽量級實施。AIB Plus可以處理更高速度,並支援高速狀態下的可靠運行。

由於支援DDR功能,所以AIB Plus介面可以在2Gbps範圍內移動資料。但是,在此範圍內保持訊號偏差和收緊時序變得更加困難。延遲鎖相迴路(DLL)可幫助調整相位關係,而工作周期(Duty Cycle)校正(DCC)電路則有助於確保盡可能接近50%的時鐘工作週期。提供這些電路的初始化和校準以確保順利啟動和運行。

這兩種配置之間的最大差異與資料傳輸速率有關。AIB Base使用單倍數據速率(SDR)方案發出訊號;而除SDR外,AIB Plus還支援雙倍數據速率(DDR)訊令。借助DDR,資料可以在時鐘的上下邊緣傳輸,資料速率比SDR提高一倍(圖3)。

圖3 SDR 訊號每隔一個時鐘緣(在本例中為下降緣)進行傳輸。相比之下,DDR在下降緣和上升緣都進行傳輸,從而獲得兩倍的資料速率。

AIB架構

AIB介面包括I/O,這些I/O分組為本身可以堆疊成一列的通道。一列包含1、2、4、8、12、16或24個相同通道。55微米的微凸塊最多支持一個通道160個I/O;這個數字會隨著凸塊間距的減小而增加(圖4)。I/O塊如下所示,顯示了SDR和DDR(僅限AIB Plus)版本中的傳輸(TX)和接收(RX)塊(圖5)。

圖4 一列最多可包含24個通道;每個通道最多包含160個I/O。

圖5 SDR和DDR(僅限AIB Plus)TX和RX塊對比。

I/O方案旨在實現簡化,同時允許兩個主要安排。特定I/O將是TX或RX訊號;沒有雙向訊號。配置通道時,一個通道可以具有所有TX、所有RX或一半TX/一半RX(圖6)。

圖6 通道可以包含全TX、全RX或半TX/半RX訊號。

一方面,這種方案為處理可能正在接受輸入並將其傳遞給另一個晶片的小晶片提供了靈活性。另一方面,如果小晶片通過其接收輸入(例如記憶體)的同一介面返回結果,則可以使用平衡的TX/RX介面。

AIB有兩個介面:一個通過微凸塊連接到附近小晶片中的相應AIB介面,另一個連接到其自身小晶片中的MAC代碼。第一個介面由I/O、轉發時鐘以及初始化和校準過程中使用的控制訊號組成(圖7)。

圖7 連接到另一個AIB介面的AIB介面包含TX、RX、時鐘和控制訊號。

MAC介面則由執行與外部介面相同功能的訊號組成,但這些訊號的詳細資訊和特定電子格式有所不同。舉例來說,從MAC接收一個時鐘訊號作為單端內部訊號,而相應的時鐘訊號將作為兩個SDR訊號,並通過外部介面發送到相鄰的小晶片(即雙端時鐘)(圖8)。

圖8 儘管格式不同,但AIB到MAC介面包含與AIB到AIB介面相似的訊號。

高資料速率功能

在GHz速率傳輸下,時序很緊湊。訊號到訊號的偏移很重要,同樣地,時鐘到訊號的偏移和抖動也很重要。當時鐘的兩個邊緣都用於資料傳輸(DDR)時,工作周期也很關鍵。因此,AIB塊中已包含一些功能,尤其是支援雙倍數據傳輸速率的AIB Plus配置。

轉發時鐘

為確保在接收AIB塊中成功接收資料,用於傳輸資料的時鐘被轉發到接收端,後者可用於捕捉資料。該時鐘將進入到MAC中,因此AIB中不一定有時鐘域變更,但MAC中可能有變更。AIB Base和AIB Plus配置均提供此功能(圖9)。

圖9 兩種AIB配置都提供時鐘轉發,其中TX時鐘以雙端形式發送,以便針對正在傳輸的資料保持低偏移。

時鐘訊號以雙端時鐘的形式轉發,同時發送真實版本和反相版本,以將其重新轉換回接收端的單端時鐘。這樣可以保持時鐘訊號的品質,因為在重新組合雙端時鐘時,時鐘上的共模雜訊會消失。由於使用I/O單元發送時鐘的兩個版本以及資料,因此可確保邊緣對齊。

接收域時鐘

某些小晶片可能沒有自己的獨立時鐘源,而是傾向于利用與其相連的晶片或小晶片的時鐘。例如,記憶體可能只是在訪問該記憶體的CPU晶片的時鐘上運行。

還是以記憶體/CPU為例,當記憶體接收資料時,例如要獲取資料的位址,轉發時鐘將使記憶體與CPU晶片保持同步。但是,當記憶體發送回提取的資料時,它需要一個時鐘,並且轉發時鐘僅影響接收捕捉,而不影響傳輸。因此,可以將CPU晶片時鐘(在本例中為從記憶體中接收資料的時鐘)作為記憶體的傳輸時鐘。該時鐘被稱為接收域時鐘,僅在AIB Plus介面中可用。

在圖10中,可以看到使用接收域時鐘的TX單元。在本例中,該時鐘被發送到MAC。在MAC中,該時鐘將被返回並用於傳輸時鐘,然後將其轉發回接收端。在這種情況下,轉發時鐘實際上與原始接收時鐘相同,因此看上去效率很低。但該圖會讓人產生一些誤解,因為各種時鐘訊號都不完全相同,它們的相位不同。透過獲取接收域時鐘並將其轉發回接收端,可以確保該時鐘與正在傳輸的資料之間的邊緣對齊。請注意,儘管MAC接收了接收域時鐘,但並不需要使用它傳輸資料;它可能有一個單獨的時鐘域用來傳輸資料。以下僅是一種可能的配置。

圖10 AIB Plus介面可以使用接收域時鐘進行傳輸(然後將其轉發回接收域)。

工作周期校正

對於DDR資料交換,根據規範,用於時鐘的工作周期變化幅度不能超過3%,因為兩個邊緣均用於資料計時。在沒有說明的情況下,1Ghz(意味著2Gbps資料)是一個極為嚴格的規範。因此,AIB Plus指定工作周期校正(DCC)模組。從技術上來說,校正塊不是必須的,但是實際使用中極有可能需要它(圖11)。

圖11 工作周期校正電路說明滿足AIB Plus介面上DDR資料交換的嚴格工作周期規範。

前向時鐘相位調整

同樣,在DDR連接的接收端,前向時鐘可能在發送和接收小晶片之間增加額外的偏差。在這樣的速率下,微小的相移可能引發問題,因此需要為AIB Plus指定延遲鎖相迴路。這也是可選的,但是極有可能需要它來確保在系統在所有情況下都能平穩運行(圖12)。

圖12 延遲鎖相迴路可幫助糾正任何鎖相失真,後者會限制AIB Plus介面上的運行速度。

重定時

在雙倍數據速率下,透過AIB介面輸出資料的ASIC或FPGA難以滿足資料路徑時序的要求。AIB Plus實施具有對I/O模組之前的模組進行重定時的選項。使用者可以靈活定義重定時的工作方式。可以簡單地使用一個或兩個寄存器分解資料路徑,以便更輕鬆在完整的電路上實現時序收斂;也可透過增加FIFO添加時鐘相位補償(圖13)。

圖13 可選的AIB Plus重定時塊可幫助簡化ASIC或FPGA時序收斂

例如英特爾的FPGA應用通常使用相位補償FIFO,即使晶片將相同的參考時鐘用於內核和I/O,這些時鐘的相位差也可能差異巨大或未知。相位補償FIFO確保正確的跨時鐘-相位域,一般來說,AIB並不指定重定時的具體方式,但很可能需要至少一個重定時觸發器。

AIB物理布局

AIB的設計簡化了與小晶片的連接,通道內的訊號在凸塊行中消除。凸塊行的數量保持最低,此外,必須滿足線路長度和路由的要求(圖14)。將AIB訊號分配給微凸塊影響了該平衡,凸塊分配也進行了調整,使凸塊之間的線路在長度上大致相等,最大限度減少中介層引發的訊號偏移。

圖14 55微米微凸塊被交錯安排在每一行中。凸塊被分配以確保線路長度較短且相同。

所有訊號均並列,最大限度降低了介面對凸塊布局的影響。例如,其他任何非AIB訊號都不會將凸塊放置於AIB使用的任何區域內。這也規定了如何使用晶片或小晶片端AIB介面的最小海岸線。當然,產生的總海岸線將取決於每通道的訊號數量和一列中的通道數量(圖15)。

圖15 AIB連接可以通過中介層上的線路實現,也可以使用英特爾EMIB橋接等橋接技術實現。

在正常AIB操作期間,介面兩端沒有差別。但是在啟動期間,兩端中的一端需要控制並跟蹤初始化和校準序列。只有在啟動階段,介面的一端做為主控埠,另一端做為從埠。無論介面是主控埠還是從埠,都將記錄在晶片或小晶片資料表中。主控埠必須連接從埠,從埠必須連接主控埠(圖16)。

圖16 AIB主控埠必須連接AIB從埠;AIB從埠必須連接AIB主控埠。

在某些實例中,可能需要一定的靈活性,以便將介面的一端做為主控埠或從埠。這種介面被稱作雙模介面,如果連接主控埠,可以將其配置為從埠;如果連接從埠,可以將其配置為主控埠。

雖然每列的所有通道都是相同的,但為了方便起見,通道都進行了編號。這些編號對AIB來說沒有任何意義,而且所有通道都可以用於任何用途。不過在某些情況下,如果通道在OSI堆疊中以較高的級別連接,那麼對於特定應用來說,不同的通道之間有著順序和重要性之分。根據小晶片的排列方向,通道可以反向連接。

換句話說,如果有12條通道,那麼在某些情況下,一側的通道0可以連接另一側的通道0,而在另一些情況下,通道0可能連接通道11。大多數情況下,通道0和通道11是相同的,因此這種反向連接沒有任何問題。如果這有關係,那麼在通道順序非常重要的情況下,MAC中可能需要反向連接通道。

冗餘

AIB連接可能涉及多達3,840個I/O,在中介層中以軌跡的形式實現。相對於生產線故障的數量來說,中介層成品率可能很高,但線路眾多,也存在單個故障毀掉整個組裝的風險。99.9%的線路成品率仍然可能是0%的模組成品率。為提高模組成品率,AIB支援兩種類型的冗餘。

I/O參與的主動冗餘。如果發現連接錯誤,所有前往介面中心的訊號將轉移至相鄰微凸塊,利用中間的兩個空閒訊號。這種單線路故障可以按通道逐一排除,以提高成品率。

測試時可以啟動這種冗餘,在模組中保存轉移位置,系統上電時,正確的連接將出現在轉移後的位置。兩個訊號會在最早的上電階段—使用主動冗餘之前被使用。對於這兩個訊號,使用的是被動冗餘。這相當於每個訊號會使用兩個凸塊,如果其中一個連接失敗,另一個連接可保持完整。

AIB與SerDes延遲對比則如表1所示。AIB的延遲相比典型串列器/解串器(SerDes)大幅降低。JESD204C實施要求進行傳輸層映射、64B/66B編碼/解碼,以及串列/解串,因此數位延遲較長。SerDes模擬延遲較長,主要因為需要在單端和差分間轉換,以及進行時鐘資料恢復。

AIB未來發展趨勢

直接射頻類比數位轉換器(ADC)/數位轉換器等超高頻寬應用將繼續推動AIB提高頻寬、減少占用空間和降低能耗。借助精心的I/O設計,資料速率將實現翻倍,達到4Gbps。

隨著高密度封裝技術的不斷改進,產業標準的微間距將大幅縮小,目前是55微米,未來可能縮小至1微米。為了將每位能耗降低至0.5皮焦耳以下,I/O電壓擺幅可降低至0.4V。後代AIB與前代AIB元件之間的相容性至關重要,將成為未來實現AIB改進的重要因素。

總而言之,AIB介面可實現晶片和小晶片之間的新型短程高速連接,可將資料傳輸速率提升高達2Gbps(甚至更高);支援超過3,000個收發訊號;採用緊湊型晶片布局,以最大限度地降低晶片占用空間;並運用微凸塊技術,最大限度地縮小凸塊間距;精心設計的訊號布局和時序電路有助於保持高速訊號的微小偏移,而冗餘可幫助確保高成品率。

(本文作者為英特爾可程式設計解決方案事業部研究科學家)

無回饋通道突破電壓限制 返馳控制器空間大精省

傳統隔離式返馳轉換器架構經常用於60瓦左右的電源供應器(圖1),利用一次側開關以及調整過匝數比(Turns Ratio)的變壓器,電源供應器的電壓便可轉換成輸出電壓。有關輸出電壓的資訊會透過回饋通道傳送至一次側PWM產生器,讓輸出電壓維持穩定;若輸出電壓過高或過低,可以調整PWM產生器的工作週期。

圖1 運用光耦合器的傳統返馳控制器連接至回饋通道。

多方並行解隔離電壓調節難題

此回饋通道不僅增加成本,更占用電路板空間,同時也決定電路的最大隔離電壓以及變壓器的隔離電壓。當光耦合器老化後,許多屬性都將隨之產生變化,且一般的設計不允許在超過攝氏85度的溫度下運作。除了光耦合器外,還可利用第三個變壓器繞組提供輸出電壓狀態的資訊。藉由這種機制便得以調節輸出電壓。然而,此額外增加的變壓器繞組會使變壓器成本更昂貴,且輸出電壓調節亦不精準。

較理想的替代方案為運用一個元件取代光耦合器及光耦合器的二次側控制模組。例如隔離式誤差放大器為具備此功能的元件,整合iCoupler隔離技術,可藉由電感耦合轉換回饋訊號—意即不須使用光耦合器且跨過電氣隔離。

甩開電壓限制 無分立通道省空間

尚有另一種簡練的解決方案不用分立回饋通道。例如Analog Devices(ADI)Linear系列LT8300無分立回饋通道返馳式轉換器,能自二次側反射回到一次側的電壓,調節PWM產生器工作週期(圖2)。由於不需用到光耦合器或其他回饋電路,不僅節省成本亦省下空間,因此,回饋通道最大隔離電壓造成的限制便無關緊要。只要採用的變壓器針對特定隔離電壓設計,整個電路便能在此最大隔離電壓下運作。

此概念基於邊界模式穩壓機制,在此模式中,二次側電流在每個週期皆會降至零安培。反射回到變壓器一次側繞組的輸出電壓,則可量測並執行一次側的穩壓。

圖2 返馳式控制器無分立回饋通道,但可藉一次側變壓器繞組調節。

另一方面,此類無分立回饋通道的電路是否能用於特定應用,取決於要求的輸出電壓調節精準度。要注意的是,元件規格雖然顯示精準度小於正負1%,但在特定應用中的偏差可能高於1%。

依據以下公式可算出輸出電壓:

溫度校正機制修整輸出電壓

圖2中顯示的Rfb可用於調整輸出電壓。Nps是變壓器的匝數比,Vf是經過二次側返馳式二極體的壓降,通常會與溫度相關。對於像12V或24V這類高輸出電壓,Vf的絕對效應較低。但對於3.3V或更低的輸出電壓,輸出電壓的溫度效應就相當高。一些未採用光耦合器的系列元件則內建溫度校正機制,用於針對不同溫度狀況修正二極體壓降。欲使調節功能正常運行,通常還會要求輸出端達到最小負載。以LT8300而言,約為最大可能負載的0.5%。

返馳式控制器雖然不具分立回饋通道,但可藉一次側變壓器的繞組控制,造就更簡單的設計,且不須使用易出錯的光耦合器。

(本文作者為ADI電源管理應用工程師)

添加DDR5功能 SDRAM效能/部署能力大增

隨著記憶體密度上升,記憶庫(Bank)的數量也須增加,以容納更高的記憶體密度。新一代的DDR5標準將記憶庫組(Bank Group)的數量擴充一倍,並且同時維持各組的記憶庫數量不變。另外,由於能夠在任一時間點打開更多的頁面(Page),以及提升高分頁命中率(High Page-hit)的統計概率,整體的系統效率應可加強。

記憶庫組到記憶庫組的交錯時序存取(Interleaved Timing)短於特定記憶庫組內記憶庫間的存取。這些時序參數同時有「長」的時序定義(tCCD_L、tWTR_L、 tRRD_L)和「短」的時序定義(tCCD_S、tWTR_S、tRRD_S)。長的時序係指記憶庫組內記憶庫到記憶庫(Bank-to-bank)的存取,而短的時序則是指存取不同的記憶庫組(圖1)。為便於理解,在此補充說明:tCCD_L可接近tCCD_S的兩倍。增加的記憶庫組可提高短時序的使用概率,進而減輕內部時序限制。

圖1 DDR5記憶庫/記憶庫組的時序

資料突發長度增加

DDR5 SDRAM將預設的突發長度從BL8加到BL16,並提高了指令/位址和資料匯流排的效率。以同樣的讀取或寫入CA 匯流排的作業而言,資料匯流排現可提供兩倍的資料,同時還能將對IO/陣列時序限制的暴露侷限於相同的記憶庫內。透過減少存取給定資料量所需的指令數,DDR5 SDRAM還能降低讀寫作業所需功率。

此外,突發長度增加後,存取相同之64B快取行(Cache Line)資料負載所需的IO數也減少。由於預設的突發長度增加,DDR5 DIMM架構得以具備雙子通道(圖2),進而提高通道的整體並行性、靈活性和數量。針對使用128B快取行負載的系統,DDR5亦特別為×4配置的裝備提供突發長度為32位元的選項,而能進一步改善指令/位址、資料匯流排效率及總體功率表現。

圖2 DDR5 40-Pin子通道DIMM範例

刷新指令

除了適用於DDR5和早期DDR SDRAM產品的標準ALL-BANK REFRESH指令(REFab)外,DDR5還導入了SAME-BANK REFRESH(REFsb)指令。當REFsb指令發出時,它會依照記憶庫位元(Bank Bits)透過指令/位址位元所指定的目標,在所有記憶庫組中鎖定同樣的記憶庫。

SDRAM設備的REFRESH指令會要求在指令發出前,被鎖定刷新的記憶庫須處於閒置狀態(預充電,無資料活動);而且,在REFRESH指令執行期間,那些記憶庫均不能重啟後續的寫入和讀取活動(時序參數tRFC)。REFRESH指令以平均週期間隔發送(時序參數tREFI)。對於REFab指令,系統必須於發出指令前確保所有記憶庫均為閒置狀態;針對16Gb DDR5 SDRAM裝置,在「正常」刷新模式下平均每3.9μs發送一次,每次持續295ns。

REFsb指令的效能優勢在於,在指令發出前,各記憶庫組內只需有一個記憶庫保持閒置狀態。當發出REFsb指令時,其餘的12個記憶庫(圖3)不必處於閒置;而且,對於非刷新記憶庫的唯一時序限制是相同記憶庫刷新到啟動的延遲 (Same-bank-refresh-to-activate Delay)(時序參數tREFSBRD)。REFsb指令只能以倍精度刷新(FGR)模式發送,意即各記憶庫平均須每1.95μs接收一次REFRESH指令。針對16Gb DDR5 SDRAM裝置,REFsb則僅持續130ns,這也將系統存取鎖定的對象(tRFCsb)減至主動刷新的記憶庫上(圖3)。使用REFsb時還有一個限制:每個「相同記憶庫」(Same Bank)都須在第二個REFsb指令發出前收到一個REFsb指令,但REFsb指令可以任一記憶庫的順序發送。

圖3 DDR5 REFsb與記憶庫的對應

模擬結果顯示,與REFsb相比,使用REFsb時系統效能吞吐量加大6%到9%(會因讀/寫指令比率不同而異),如圖4所示。另外,REFsb將刷新對平均閒置延遲時間的衝擊從11.2ns減為5.0ns。這些計算乃基於標準排隊理論所得,並適用於具隨機驅動資料流量的單個記憶庫。

圖4 DDR5系統吞吐效能改進

效能改進

以上述特點模擬64B隨機存取的工作負載後發現,與DDR4雙Rank的3200MT/s模組相比,效能顯著提高(圖5)。在此模擬情境中,假設各系統有8個通道與1DPC。

圖5 DDR5 不同速度/記憶庫模組的效能改進

透過從DDR5設備輸出資料前在READ指令期間進行校正,RAS的提升(如on-die...

預防勝於治療 狀態監測確保設備健康

非規劃停機所造成的成本每小時可達數千甚至上萬美元。在2017年曾經進行的一項研究中,發現許多企業遇到停機時每小時平均成本高達200萬美元,非規劃停機造成的成本遠高於計畫性維護,因為機器必須下線進行診斷、訂購替換零件,然後才能進行維修。

機器在規格範圍內持續運轉,以及機器預期的剩餘壽命,都會受到各項變數所影響,包括如運轉時間、負載與運轉環境的變動,以及各種損壞事件等。狀態監測的目的,旨在找出這些影響因素的量化數據,以在需要立即注意時即時提供警訊,並精準預測需要介入的時機。

每部機器都不盡相同,每部機器老化的過程也不一致,而老化的過程通常緩慢且難以察覺。除非長期主動觀察細微變化的徵象,不然即使長時間下來也看不出老化的現象。之後有朝一日機器忽然失效,可能是災難性故障,意謂著機器必須離線進行維修。終端使用者希望針對即將發生的失效提前收到通知,藉以提前進行停機的計畫。他們也會觀察機器細微變化的各種徵象,這些因素可能影響類似紙張與金屬板材這類最終產品的品質。

各界需要更加提早觀測出機器磨耗,以及機器輸出品質的資訊,帶動對於更靈敏與更全面性感測的需求。另外,量測的種類也更加多元,包括溫度與振動等感測模態,如今也透過音響、馬達電流,以及電壓量測等方式提供輔助。這些量測系統匯整之後,即可對設備的狀態得到更全面的認知。因此每部機器上裝設著越來越多的量測通道。個別的量測通常需要妥善協調以顯示彼此的關係,像是x/y/z三個軸向的振動數據。而對於同步化的需求,也導致系統的複雜度更加提高。

量測節點日趨分散以及模態的多元化,意謂著以人力資源進行檢視與量測的方式已無法跟上實際作業的需要(圖1)。系統必須分散部署在廠房的各處或偏僻角落,並使用現有的有線基礎設施或無線網路,運用穩定安全的無線系統進行通訊。龐大且昂貴的感測器以及匯流傳輸設備必須做得更小、低價、省電,才適合裝設在這些環境。為此,許多新元件與子系統型態的新型精準解決方案,具備更高的整合度,讓系統廠商現在就能實現上述的感測功能。

圖1 使用壓電感測器是由掌上型裝置,以人工方式檢測設備。

資料擷取是狀態分析首要任務

想要儘可能提早察知機器耗損的徵兆,就等同於須擁有預見未來的能力。在狀態監測分析方面,方法就是觀察系統中各種最細微的變化,包括系統溫度、振動,或聲響等徵狀。想要感測到這些細微的變化,感測器與資料擷取系統必須能以最小偵測分辨率單位明確觀測到這些細微改變,包括在極高的振動或溫度下也能精準量測。為此訊號鏈必須具備極高的動態範圍,意謂著系統得擁有極低的雜訊,同時還能應付極大的變動。

舉例來說,要對往復式水泵偵測出機件磨損的徵兆,就必須能偵測出活塞死點不到十分之一毫米的磨損差異,而活塞的往復行程則達到300毫米。要確保能看到如此細微的變化,其條件則是系統雜訊必須低至少10倍。因此偵測水平必須達到1:300,000或109dB,須採用18位元或更精準的資料擷取系統。

另一項考量因素,是拓展出更多傳輸頻寬範圍。馬達軸以及許多齒輪系統的振動頻率相對較低,頻率相當接近軸轉速或僅是軸轉速的數倍。然而,系統中其他零件則擁有較高頻率特徵。為此,想要偵測擁有較高頻率特徵的零件因磨損產生的偏移,像是滾珠或油封軸承這類零件,感測機制必須在超過10kHz甚至80kHz的頻率下達到高解析度與高動態範圍(圖2)。

圖2 典型振動頻率特徵

感測系統規格必須包含高動態範圍(DR),以及極低的總諧波失真(THD),才能在系統振動模式(Profile)下解析出這些頻域特徵。在這些系統中,主要是運用最新精準型大頻寬三角積分(Σ-Δ)轉換器來執行類比至數位轉換步驟。這類極精準的類比至數位轉換器能滿足這些系統的關鍵需求。此類轉換器擁有優異的動態範圍以及THD(一般為+108dB DR到120dB THD),能在至少80kHz頻率下覆蓋dc直流頻寬,另外還具備許多簡單易用的特色,像是類比輸入端的預先充電緩衝器、整合式數位濾波器、跨元件同步支援多通道相位匹配,使得這些關鍵元件能用來建構最高效能的CbM資料擷取系統。

功率調整(Power Scaling)功能讓同一個實體硬體經調整後能支援特定功率上限的規範,針對整體功率匹配適合的動態範圍或頻寬。在直流以及較大頻寬條件下提供精準偵測,同一個平台的輸入通道能滿足包括溫度、形變,以及其他直流或低頻寬感測的需求,進而簡化整體條件監控系統的架構並降低複雜度,也就是單一平台即可支援所有種類的CbM感測器。

同步取樣確保相位關係保存

在CbM系統中,同步取樣用來確保各組時域資料之間的相位關係得以保存。舉例來說,兩個正交設定的振動感測器可用來偵測振動向量的方向以及振幅。在理想狀態下,相位會延著每個感測器輸入通道逐漸延遲,並應該和溫度變化相匹配。

對於CbM系統而言,設計上需要更多的彈性,方能因應取樣率、頻寬,或功耗擴充需求方面更寬廣的範圍,因此SAR ADC產品也很適宜。這些元件還提供高動態範圍與THD,吞吐量可達2 MSPS,並融入許多易用特色,除了降低訊號鏈的功耗以及訊號鏈的複雜度,還促成更高的通道密度。具備更高輸入阻抗模式的轉換器能擴展低功耗精準型放大器的範疇,這類放大器能直接驅動這些ADC,並達到最佳的效能。

為讓系統廠商針對更精小或分散式擷取節點可達到最高的通道密度,以及加快上市時程,半導體業者如ADI開發出新的訊號鏈μModule產品,可提供比以往更高的整合度。這些μModule元件結合資料擷取訊號鏈設計常用的關鍵零件,打造出小巧的積體電路(IC)形態。

μModule將類比與混合訊號元件的挑選、最佳化、以及配置等方面的設計負荷從設計者轉移到元件,藉以縮短整體設計時間以及系統除錯工作,最終則加快了上市時程。裝配在微型封裝內的μModule元件非常適合用在分散式少數量通道的微型CbM系統中,或更高通道數量的機架式系統(圖3)。

圖3 μModule組件的3D著色圖

MEMS感測器助力狀態監測執行

光是在訊號鏈的資料擷取部分提供高動態範圍、更廣的頻寬、更高的電源效率,以及更高的通道密度,只能解決CbM系統一部分的系統設計挑戰。傳統整合式電子壓電(IEPE)振動感測器龐大、笨重、昂貴,且供電線路的電壓通常比資料擷取系統還要高。一般而言,壓電式感測器採用24V的單一電源,消耗2毫安培的電流,封裝在金屬外殼內。由於感測器一般裝在資料擷取模組內,因此提高設備內部通道密度,就會衍生電源密度以及元件密度的問題。更糟的是,在以電池供電的無線擷取節點中,傳統壓電式振動感測器已不再能滿足這些設計鏈的需求。

MEMS微機電式振動與慣性感測器現在能滿足這些系統的需求。最新的高頻寬MEMS元件具備的雜訊與頻寬效能適合各種CbM應用,而且在標準的微型化表面黏著封裝就能達到這般的效能,同時功耗還比IEPE感測器低了20倍。這些MEMS感測器的小尺吋與功耗特色,讓業者能開發出超小型電池供電多軸系統,以用來執行永久與持續性狀態監測。

功耗與連結

感測機器的溫度、振動或噪音,之後將訊號轉換成數位資訊,這些都是監控作業的關鍵部分,但這些還不是完整的流程。要建構狀態監測系統,必須注意設計專案中所有類比、數位,以及混合訊號元件。資料擷取鏈要達到低雜訊,需要的不光只有低雜訊感測器以及類比至數位轉換元件,還包含低雜訊電源設計。系統要達到低功耗,電源元件必須有效率地從電池或線路汲取電力,而且不會增加設計的複雜度。

連結需求取決於應用環境。許多工業場所已有完備的布線,用來執行製程控制或現在的環境感測,像是溫度量測。然而,這類現存基礎設施大多數無法因應大規模狀態監測所涉及的龐大原始資料或資料傳輸率。

提高既有布線功能的其中一種方法,就是增加更多資料而且不影響現有的功能。舉例來說,HART技術可用來在常見4mA至20mA類比介面上加入數位格式的診斷資訊。類似的狀況,工業乙太網路能增加既有乙太網路布線的決定性以及即時控制力,反映在控制應用上就是延遲的表現,FFT資料所需的更高頻寬,以及允許每個鏈路設置多個節點。

另一種途徑就是無線傳輸資訊。在工業環境中,需要穩健且安全的無線聯網。最新的智慧網狀網路(Mesh)拓撲無線電產品,包含無線晶片,以及預先認證的電路板模組,即使置於充斥干擾雜訊且持續變動的射頻環境中,也能以低功耗執行通訊並達到超過99.9999%的資料可靠度。對於狀態監測而言,這意謂著失效或瞬變事件都能和host主控端進行通訊,並在最短的時間內做出因應作為(圖4)。

圖4 模組圖顯示典型精準資料擷取訊號鏈的子模組。

CbM角色將愈加吃重

狀態監測對於大型高資本設備是絕對必要的,包括像能源與油氣,在這類環境中,非規劃中的停機會直接影響對生產成本。另一方面,工廠扮演的角色越來越吃重,因為除了能主動執行機器維護之外,還能有一種方法來確保機器在正常運轉下能穩定一貫地生產產品。隨著這些監控功能的價值越來越顯著,這項技術將開始擴展到越來越多我們每天所運用的機器上,而不再是風力發電機或造紙廠的專利,未來,將會看到CbM廣泛地應用在火車、飛機、汽車,最終拓展到洗衣機甚至體積更小的家電中。

系統零件製造商未來必須整合感測器,或甚至整個通道都整合到零件之中。未來的馬達將配備振動與電流感測機制,而軸承與齒輪箱也是如此。未來許多自主性運行感測器節點會向行動裝置通報訊息,這些部署在車庫門上的裝置,能在車被塞在車庫內之前向車主發送警訊。

為因應在這些不同情境中持續增加的感測需求,許多設備製造商未來必須採取平台模式,運用少量的平台因應更多化的需求。量測通道必須支援不同的感測器類型,讓機架式設備能改成支援不同的感測器組合。在較小設備方面,系統必須能對不同供電條件進行調適,讓相同監控節點能用在洗衣機或電池供電工具。

狀態監測大幅減少災難性故障機率

狀態監測針對機器內部感測各項可量測的參數,藉以對機器的健康狀態取得量化數據。提高這些量測結果的精準與靈敏度,以及降低監控設備的尺寸/重量/耗電,即可讓工廠管理者將這類感測機制部署在廠房各角落。

現今的工作都配置健康監視器,就像健身追蹤裝置讓管理人員能對工廠運作有更深一層的掌握,隨時得知機器運轉的每一分鐘變化,並根據這類資訊及早做出有根據的決策。提前排定維護工作,並且僅對有需要維護的機器進行保養將能大幅降低維護成本,而技術人員在下班後的出勤以及待命成本,則能降低至零。

此外,由於工作維持在更嚴密控管的狀態,資本設備成本也能因此降低。早期偵測與替換已磨耗的零件,有助維護機器的整體健康。嚴密監視能減少災難性故障的發生機率。設備的壽命也得以延長,並持續維持到壽命終止。

工廠最終產品的生產成本得以降低。在掌握機器健康狀況下,機器的容錯性(Tolerance)即能維持在可控制的範圍內。最終產品各批次的輸出品質也更加穩定。當機器發生狀況或突然停擺的次數降低時,產品重工與廢料也會隨之減少。

(本文作者為ADI資深應用工程師)

垂直式磁化材料優點多 磁性記憶體儲存/性能增

磁性記憶體(MRAM)具有應用於非揮發性嵌入式記憶體的潛力。相較於傳統的磁場寫入方式之磁性記憶體而言,自旋傳輸磁性記憶體不論是在密度、容量、耗能、速度、尺寸微縮化以及製程成本上都有很大的優點。目前各研究團隊針對自旋傳輸磁性幾乎都已經進展為垂直式磁化材料為主,這種垂直式自旋傳輸磁性記憶體相較於傳統的水平式傳輸磁性材料,可改善水平式傳輸材料無法同時滿足降低元件寫入電流與提高元件的熱穩定性的難題。

以垂直式磁化材料取代水平式磁化材料被認為是解決上述問題最可行的方法。本篇文章將探討垂直式自旋傳輸翻轉的特性,並且介紹目前國際上以及本團隊關於垂直式自旋傳輸磁性記憶體與其他相關熱門磁性研究的發展現況。

STT MRAM發展潛力佳

磁性記憶體於1980年代首次被提出。1984年Honeywell以異向性磁阻(AMR)技術為基礎開發了最早期的MRAM,由於其抗輻射特性以及製作成本高昂,主要應用於軍方以及航太用途。1988年發現巨磁阻(GMR)現象後,開始吸引了許多人投入MRAM相關的研究。

而到了1995年,實驗證實穿隧式磁阻(TMR)的現象,而其後的研究證實其磁阻變化率可高達220%以上,至此確定了MRAM的發展趨勢。MRAM基本架構為1個電晶體搭配上一個稱為MTJ(Magnetic Tunnel Junction)的磁性多層膜元件,簡稱為1T-1MTJ架構。

傳統的MRAM寫入方式為利用兩條正交的導線所產生的磁場將被選取之MTJ結構磁性自由層(Free Layer)磁化向量翻轉,使得磁性自由層與被固定層(Pinned Layer)的磁化向量呈現平行(低阻態)或反平行(高阻態)而達到寫0或1。

這種寫入方式會遭遇到兩個主要的技術瓶頸,第一是只有單軸導線通過而非雙導線交叉選擇的MTJ,容易因為導線磁場干擾而造成錯誤寫入;第二是當MTJ尺寸隨著技術節點持續微縮時,磁性自由層磁化向量翻轉所需要的磁場大小或寫入導線電流會急劇升高。這樣不僅耗電,而且會使得寫入電流超過導線可容忍之範圍而產生失效。

新一代的MRAM寫入方式為利用自旋力矩傳輸(Spin-torque-transfer, STT)效應翻轉磁性自由層的磁化向量。這種寫入方式電流僅通過被選擇的記憶單元,所以不會有因導線磁場干擾,而造成寫入錯誤的問題。同時,由於磁性自由層翻轉取決於電流密度,因此隨著記憶單元持續微縮,翻轉所需要的電流不僅不會升高,反而會下降。

除此之外,STT MRAM在製程上也比傳統MRAM簡化許多,如此不僅可以減少製程費用,也可大幅提升記憶體密度。傳統MRAM的Cell Size大約在20~30F2,而STT MRAM可將Cell Size降至6F2。另外,STT翻轉寫入速度可達4ns,因此STT MRAM不論是在密度、容量、耗能、速度、尺寸微縮化以及製程成本上都有很大的優點,使得STT MRAM具有應用於非揮發性嵌入式記憶體的潛力。

追求更高儲存密度 SOT成新解方

目前STT MRAM的產品主要都是以水平式磁化材料作為MTJ結構之磁性層,例如Co、Fe、CoFe、NiFe,以及CoFeB等磁性材料。不過,這種水平式STT MRAM所遇到最大的挑戰,即為降低MTJ磁性元件寫入電流密度的同時,還需要提高元件對於熱擾動的穩定度,並且提高寫入與讀取資料的準確度。

預估在進入45奈米技術節點後水平式STT MRAM將面臨寫入電流與熱穩定性無法同時兼顧的問題,除非在磁性材料的特性上有所突破;而以垂直式磁化材料取代水平式磁化材料之STT元件被認為是解決上述問題最可行的方法。

磁性材料除了應用在磁性記憶體上,在感測器領域亦有相當的發揮空間。利用微小外在磁場即可使磁感測器靈敏做出判別的特性,做為生物感測器的主要元件再適合不過。而除了感測微小的外加場變化,磁性感測器當然也能改以較硬磁如CoFeB、CoFe等做為主要材料,涉足大場感應市場。由於可針對使用領域變化感測場的範圍及靈敏性,磁感測元件勢必大有可為。

而在已然形成的磁性記憶體市場中,下個目標除了繼續增加磁性記憶體的儲存密度,更希望改善耗電情況以及提升記憶體讀寫壽命,旋軌道轉矩型(Spin-orbit-torque RAM, SOT-RAM)這樣的磁性記憶體結構,利用自旋電子流來影響記憶層的磁矩排列,較之STT MRAM有著更節能的優勢,目前世界上各個研發團隊紛紛投入SOT的開發中,是現今磁性記憶體中炙手可熱的新星。

克服磁矩以達到小尺寸/高密度

磁紀錄依磁化狀態的不同可分為水平記錄和垂直記錄,水平記錄之記錄媒體的磁化方向是平行基板的表面,而垂直記錄之記錄媒體的磁化方向則是垂直基板的表面。水平記錄由於Pattern承受的去磁場大,因此不利於達成高的記錄密度;垂直記錄則因為磁化方向垂直於磁頭移動方向及記憶媒體表面,去磁場小,因而可以得到較高的記錄密度。

利用上下電極間的磁性多層膜,不同磁性膜層間交互作用影響之下,通過電流時因磁矩排列方式的不同而得到的磁阻值變化。為了能夠達到小尺寸高密度記憶元件的發展,垂直式磁矩排列的記憶元件將會是一個大有可為的發展方向。若要能讓垂直式磁性記憶元件發展順利,首要克服的便是其磁矩的排列方式,如何能在記錄膜層鍍製時,便讓其有整齊並且可完美控制的磁矩排列。

水平記錄膜層堆疊主要如圖1所示,底電極之上為提供各膜層良好織構(Texture)的種子層材料,接下來是固定未進行讀寫時磁矩排列方向的反鐵磁層(Anti-ferro),反鐵磁層與SAF被固定層決定了交換場的大小,當交換場越大就表示該膜層結構能承受的外界場影響越大,當記憶元件在進行讀寫之時表現也會越穩定。

圖1 水平記錄膜層堆疊示意圖

若變化不同的MTJ結構如下類型(圖2),膜層排列的方式不再因為反鐵磁層來決定,而是利用磁性層Co以及金屬層Pt交互堆疊,利用兩種材料間的交互作用力,在Co極薄的情況下可以讓磁矩完全垂直膜面排列,這就是垂直式磁性元件所設計的被固定層。

圖2 變化不同的MTJ結構示意圖

並且,利用Ru金屬層的RKKY特性,使得Ru上下的Co/Pt多層膜雖然是垂直膜面排列,但依著不同的Ru在RKKY Peak的厚度,一樣可以依需求製備出不同大小的交換場,當然,交換場越大也就表示元件對於外在環境影響下的穩定度越高。

在這樣的膜層結構下,利用MgO做為Tunneling材料,調變MgO的厚度以及製程參數,可以得到MR 40~90%;變化Free Layer的材料為CoFeB、CoFeB/Ta/CoFeB Composited結構等,可使讀寫層的翻轉更迅速,Hc能大於200Oe。不同的上下電極材料(Ta、TaN、Ru等),所影響的P-STT MTJ之PMA特性也不同,利用Modified...

加速打造邊緣智慧應用 整合/開放/多元為關鍵

邊緣運算市場需求大增 將成IoT主流架構

傳統物聯網系統架構,多半將資料直接上傳至雲端,經過運算、分析後,再下達指令給終端設備,或是將分析結果呈現在終端使用者眼前。然而,隨著物聯網應用範圍越來越大,越來越多的終端設備,造成資料快速累積,龐大的資料通通上傳至雲端,不只浪費了雲端資源,也影響資料處理效率。

舉例來說,一個偵測空氣品質的感測設備,在偵測到污染物,如二氧化碳、PM2.5等超過標準值時,會跟換氣設備連動,改善現場的空氣品質。如果這類設備的安裝數量擴增,代表雲端需處理大量資料,並進行邏輯運算,才能決定是否啟動換氣設備,這將對雲端造成負擔。

客戶當然可以藉由增加伺服器的方式,提升雲端的運算能力,但問題是當運算需求變得複雜時,雲端的運算能力必須是幾何倍數的成長,才能滿足物聯網的資料處理需求。因此,比較有效率的做法是讓邊緣端負責資料處理、設備管理、連網等基礎工作,而雲端則負責動態學習,對邊緣端的運算結果進行大數據分析,持續修正資料處理的邏輯、異常判斷、標準值等。

因此,研華推出邊緣智慧伺服器(EdgeIntelligence Servers, EIS)並受到市場的廣大迴響。且根據IDC調查報告,至2019年IoT所建立的資料,有45%的儲存、處理、分析會發生在邊緣端及其所建構的網路上,透過EIS進行初步分析工作,減少雲端運算資源運用,進而提高效率,將成為未來物聯網傳輸架構的主流。

軟硬整合實現一次到位解決方案

因應IoT邊緣運算的需求,研華EIS涵蓋軟硬整合解決方案,包括嵌入式無風扇電腦、WISE-PaaS/DeviceOn設備維運管理軟體及預整合微軟Azure雲端服務。

考量到物聯網應用的獨特性,研華在開發邊緣智慧伺服器時,以開放、多樣化為核心精神,從硬體到軟體都提供各種不同選擇,希望能滿足IoT 系統整合商的多元需求。首先從硬體端來看,EIS系列提供3種不同類型的嵌入式無風扇電腦,涵蓋不同體積大小、接口種類、及運算處理能力(即CPU),方便物聯網SI依需求做選擇。其次軟體端,EIS預載了WISE-PaaS/DeviceOn設備維運管理軟體,透過介面的簡化與優化設計,全面提升物聯網終端設備的管理效能。

WISE-PaaS/DeviceOn設備管理維運軟體套件, 提供不只針對操作系統上的管理,設備系統硬體和I/O狀態監控,和確保受管理的週邊系統能24小時正常維運,其中遠端監控及管理、軟體更新(OTA)、更資料與系統保護功能的集中式安全管理等功能降低管理維修人員的工作負擔,創造出全新的智慧化設備管理型態。

第二是WISE-Agent中介軟體,協助進行設備資料的搜集與格式整合。WISE-Agent支援各種工業通訊協定,可以將底層感測器或設備的資料,整合成MQTT標準通訊協定,傳輸到WISE-PaaS平台。WISE-Agent也提供完整開發工具,包括SDK與範例程式碼,幫助SI更快落實物聯網應用的開發。而Azure雲端服務的整合,則讓SI不必煩惱資料如何上雲的問題,可以專注在App或儀表板的開發。

另外,研華也與第三方業者合作,提供各種不同功能的軟體模組,例如:資料備份與復原,客戶可依需求直接在WISE-PaaS Marketplace線上軟體市集加購。EIS就像一隻手機,SI可以透過不同的APP去強化它的功能,進而實現IoT在邊緣端連網、進行資料管理與分析的目標。

以EIS實踐設備預防性維護 維護成本/停機風險大減

透過研華EIS可以大幅簡化SI的系統開發過程,如此一來,系統整合商只要專注在「定義數據」這件事上,將物聯網的應用和需求,融入到開發情境裡,不必處理過多物聯網系統整合的問題,平均可以縮短50%的開發時間。

某半導體業者便應用研華EIS成功地發展出「設備預防性維護」機制。該半導體業者在轉型智慧工廠過程中,發現有些製程中的關鍵資料無法被蒐集,所以導入研華EIS解決方案,透過EIS在邊緣端進行數據的整合與管理、邏輯運算和流程處理,並針對機器和設備蒐集來的運作資料進行大數據分析,以而建立模型,在機器設備已屆使用期限前預先進行維護,結果維修經費降低60%、停機時間由1~3天縮減為4~10小時,連帶讓稼動率也獲得改善,大幅提升生產的效率。

除了半導體廠之外,傳產設備藉由導入EIS,實踐預防性維護,也能創造很大的效益。舉例來說,廣泛運用在各種工業領域的空氣壓縮機,若能藉由預防性維護來避免無預警故障或耗材未即時更換,就能幫使用者降低產線停擺的風險。

空氣壓縮機是一種藉由壓縮空氣,將機械能轉換為氣體壓力能的裝置,在工業上使用十分廣泛,例如用來升降搬運、輪胎充氣、清潔除塵、噴漆塗裝、真空包裝、切割等。

東正鐵工廠是台灣首屈一指的空壓機製造商,自行研發設計並生產空壓機,行銷國內外超過半世紀。由於意識到預防性維護的重要性,東正與研華合作尋求解決方案,針對該公司所生產的空壓機(主要是復式空壓機及螺旋式空壓機等常見機型)進行空壓設備資訊收集,透過物聯網平台將資訊送至邊緣伺服器和雲端進行運算和分析,因而可得知空壓機運作狀況和零件健康情形,而能透過「雲服務」事先通知空壓機經銷商及其用戶,進行即時維護或設備保修,避免因故障停機所造成的生產停滯。

在這個應用案例中,主要監控的數據包括空壓機的溫度、壓力、空氣、油、油氣分離濾清器及傳動皮帶、軸承等空壓機關鍵零組件之健康狀況,在故障發生之前即主動通知保修人員進行耗材更換。

由於研華在資訊收集、設備管理方面皆能提供完整軟硬體解決方案和平台,東正研發團隊透過與研華攜手合作,完成空壓機預防性維護雲端管理系統之設計,不但提升空壓機產品附加價值,引領業界潮流;且空壓機用戶也可享受到物聯網所賦能之工業4.0所帶來的種種便利。

本案重點為針對該公司所生產之空壓機進行機台狀況之資料採集與分析、並進行分析結果之可視化即時呈現和歷史資料庫之建立;廠商同時希望系統能透過電子郵件及Line等方式,發送空壓機警告訊息通知用戶和相關人員,並納入倒數機制,在耗材保修期將屆或產品使用壽命到期之前主動提醒用戶。

現場需要建置邊緣運算系統進行有效率之資料蒐集、分析,並將有意義之資訊傳送至雲端平台,以方便設備製造商和代理商了解設備狀況(用戶亦可選擇資料僅限於工廠管理單位得悉,不上傳設備供應商)。

由於螺旋式空壓機屬於較高階機種,本身具有數位控制器,只需透過一條線路連結控制器和電腦並透過無線/有線網路即可進行設備資訊收集;往復式空壓機本身沒有控制器,則必須加裝外掛式資料收集模組,再傳送到電腦進行判讀。

在這個案例中,採用了研華的EIS-D210邊緣智慧伺服器。該產品體積小巧、內建英特爾(Intel)Celeron N3350中央處理器,可擺放進客戶生產的螺旋式空壓機機台內部或外部配置,並透過Wi-Fi無線網路與空壓機控制單元建立連結、取得設備運作資訊。

除了Wi-Fi模組,EIS同時提供序列埠,用戶亦可選擇以線路連接控制器完成網路連線。序列埠同時可用於連接電表,取得電壓/電流/功率(KW)/瓦時(KWH),傳送至電腦進行估算,可讓使用空壓機產品的用戶得知產品帶來的節電效果。

更重要的,每一台研華EIS-D210皆預建研華物聯網裝置管理平台WISE-PaaS/DeviceOn,不管客戶的機台設備及周邊裝置使用何種工業現場通訊語言,皆可透過WISE-PaaS/DeviceOn立即轉換為物聯網通訊格式,而能透過邊緣運算或雲端分析了解機台狀況並進行設備管理。WISE-PaaS/DeviceOn更提供各種豐富之API,可用來開發儀表板,針對資料運算分析結果進行可視化呈現,並產生客製化之訊息;強大的跨平台能力,透過雲端連結電子郵件或Line社群軟體應用程式,讓用戶走到哪兒都可輕鬆了解機台狀況,一目了然。

物聯網雖然不是新技術,卻是全新的系統架構,研華希望透過EIS邊緣智慧伺服器,協助系統整合商解決發展IoT時可能遇到的種種問題,讓SI能夠專注在自身專長領域,加速實踐物聯網邊緣智慧應用。

(本文作者為研華IoT嵌入式平台事業群產品經理)