RISC-V

看準算力供不應求 全球RISC-V聲勢喊漲

由於算力、邊緣、人工智慧(AI)等需求暴增,如供應鏈針對軟體及IP需求提升,加上新興應用/場域亦需更高階的算力才得以實現。同時,RISC-V的成本、技術及策略風險亦為業界關注的焦點,因此,考量到諸多優點,越來越多全球業者逐步採用RISC-V架構,如市場調研機構Tractica便預估其全球市場營收至2025年將達11億美元。

全球RISC-V生態系的發展,不難想像從開源軟體、硬體到CPU核心的延伸,如何用同一架構且較低成本的方式達到差異化,為各方首重的課題。拓墣產業研究院資深分析師姚嘉洋以中國為例,指出中國RISC-V發展動態值得留意,他認為雲端服務供應商(CSP)會扮演推動發展趨勢的要角,以阿里巴巴旗下半導體商平頭哥為例,其致力於推動開源架構提供給晶片及系統業者進行差異化開發,因此中國晶片及系統業者皆能因此受益。另一方面,姚嘉洋以芯來科技為例,該公司於2019年與兆易創新合作,推出首款RISC-V MCU晶片,並於2020年獲小米投資,可望加速中國RISC-V生態系的拓展。

拓墣產業研究院資深分析師姚嘉洋表示,中國CSP業者將為驅動RISC-V趨勢的推手

台灣RISC-V聯盟副會長兼晶心科技總經理林志明則引述NVIDIA執行長黃仁勳的說法指出,AI提供動力的矽晶片,其性能將每兩年增加一倍以上;若以曲線圖表示,從摩爾定律與市場需求曲線相距越來越大,不難看出整個產業針對算力的供應及應用嚴重缺乏。據此,RISC-V基於開源指令集的諸多特點,如設計簡單、可模組化等特性,可以企及更高的算力,因此已然成為SoC在設計時納入考量的選項。若以應用發展來看,目前最早進入量產的領域包含指紋辨識及藍牙等應用,無論是邊緣、AI、IoT等領域皆有市場需求,因此未來林志明預估,全球採用RISC-V的晶片將會越來越多。

台灣RISC-V聯盟副會長兼晶心科技總經理林志明表示,期許台灣企業投入RISC-V聯盟,進而可於國際場域凝聚話語權

放眼RISC-V近期發展,根據市場調研機構Semico的預測,2025年全球市場將有超過624億顆採用RISC-V的處理器核心。林志明補充,全球RISC-V聯盟在近一年內增加超過220個會員,目前總數已來到750個。放眼聯盟成長曲線斜率越來越高,顯示全球參與RISC-V聯盟以及採用RISC-V設計方面越來越積極,因此他對此樂觀表示,將RISC-V將可望成為ISA主流選擇趨勢。不過針對台灣現階段參與狀況,林志明坦言,以現階段參與全球聯盟成員數僅有六個的景況,於國際影響力較有限,因此他也期待各界可踴躍加入,進一步掌握話語權。

瑞薩採用晶心科技RISC-V 32位元CPU核心

瑞薩電子日前與晶心科技(Andes Technology)進行技術IP合作。晶心科技提供以RISC-V為基礎的嵌入式CPU核心,以及相關系統單晶片(SoC)開發環境的供應商。瑞薩選擇AndesCore IP之32位元RISC-V CPU核心,嵌入其全新的ASSP中,該產品將於2021年下半年開始為客戶提供樣品。

瑞薩採用晶心科技RISC-V 32位元CPU核心

晶心科技總經理林志明表示,MCU供應商瑞薩電子已經將晶心的RISC-V核心設計到其預燒錄的特殊應用標準產品中。瑞薩和晶心都有相同的願景,就是RISC-V將成為SoC的主流CPU指令集架構(ISA),並欣然迎接RISC-V時代。這不但是晶心科技代表性的里程碑,也代表開放原始碼RISC-V ISA作為主流運算引擎時代的來臨。瑞薩的客戶將會得益於為21世紀運算需求而建構的現代化ISA。

瑞薩物聯網與基礎設施事業部執行副總裁兼總經理Sailesh Chittipeddi則認為,晶心科技的RISC-V核心IP,提供可擴展的性能範圍,可選擇的安全功能,以及客製化的選項,讓瑞薩能夠對未來的特殊應用標準產品,提供創新的解決方案。客戶如果正在為現有或新興的應用產品,尋找經濟的替代方案,就會因此而得益於上市時程縮短與開發成本降低。

瑞薩以RISC-V核心架構為基礎的預燒錄設計ASSP晶片,在交貨時還結合專用的使用者介面工具,來設定應用產品的可程式參數,可提供客戶完整、最佳化的解決方案。這項功能可消除初期對RISC-V開發和軟體的投資障礙。此外,由瑞薩在各地具有特殊專業知識的合作夥伴所組成的大規模網路,將可提供集中化的客戶支援。

Microchip發布RISC-V開發套件

免費和開放式的RISC-V指令集架構(ISA)的應用日益普遍,推動了經濟、標準化開發平臺的需求,該平臺嵌入RISC-V技術並善用多樣化的生態系統。為滿足這一需求,Microchip推出基於RISC-V的SoC FPGA開發套件。這款Icicle Kit開發套件專為業界領先的低功耗、低成本、基於RISC-V的PolarFireSoC FPGA打造,彙集了眾多的Mi-V合作夥伴,協助多樣產業客戶加速設計部署和商業應用。

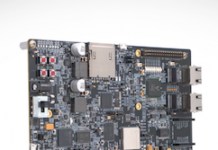

Microchip發布RISC-V之SoC FPGA開發套件

Microchip FPGA業務部副總裁Bruce Weyer表示,隨著 RISC-V 軟體和矽晶片在市場上的廣泛應用,Microchip正在引領處理器設計的革命性轉型。我們正在透過一個低成本評估平臺消除進入門檻。藉由這一平臺,嵌入式工程師、軟體設計人員和硬體開發人員可以同時利用開放式 RISC-V ISA 的優點與 Microchip業內最佳尺寸外型、散熱和低功耗特性的PolarFire SoC FPGA 進行設計。

RISC-V國際董事會副董事長、2017 年圖靈獎獲得者David Patterson指出,售價不到 500 美元的低功耗RISC-V開發板讓人眼前一亮。Microchip Icicle工具套件內置 PolarFire SoC,將加速 RISC-V 軟體生態系統的發展,對需要低功耗中階 SoC FPGA 的應用來說是個好消息。

設計人員現在可以開發和評估即時操作系統(RTOS)、除錯器、編譯器、模組化系統(SOM)和安全解決方案等廣泛的RISC-V生態系統產品,進而輕鬆部署基於RISC-V的可程式設計SoC FPGA。Mi-V RISC-V合作夥伴生態系統是Microchip和眾多協力廠商為全面支持RISC-V設計而開發的一個不斷擴展、全面的工具套件和設計資源。

Icicle工具套件以擁有25萬個邏輯元件的 PolarFire SoC 為中心,包括 PCIe連接器、mikroBUS插槽、雙 RJ45 連接器、Micro-USB 連接器、CAN匯流排連接器、Raspberry Pi 插針連接器、JTAG埠和SD卡介面,為開發人員提供了功能齊全的開發平臺。Microchip 經過設計、驗證和測試的功耗管理和時脈設備、Ethernet PHY(VSC8662XIC)、USB 控制器(USB3340-EZK-TR)和電流感測器(PAC1934T-I/JQ)為開發板提供支援。

PolarFire SoC FPGAs 的總功耗比同類競爭產品低 50%。透過使用SoC FPGAs,開發人員還可以通過元件固有的升級能力和在單個晶片上整合功能的能力,獲得更多的客製化和差異化機會。PolarFire SoC FPGA 系列提供多種封裝和尺寸,更容易平衡應用的效能與功耗,使客戶能夠在小至11×11毫米的封裝尺寸上實施解決方案。Microchip的Polar...

RISC-V Taipei Day邊緣智慧嵌入式設計應用論壇

台灣RISC-V聯盟(RISC-V TAIWAN ALLIANCE, RVTA)將於9月25日在台北南港展覽館舉辦【RISC-V Taipei Day】引領EDGE AI設計新革命─邊緣智慧嵌入式設計應用論壇。

近幾年來人工智慧(AI)邊緣晶片已進入高速成長階段,根據德勤(Deloitte)預測,2020邊緣AI晶片的成長速度將遠高於整體晶片市場。預估到2024年出貨量可能超過15億顆,年複合成長率達20%以上,比起整體半導體產業長期的年複合成長率9%高出許多。

一般而言,AI需要較大的算力來進行大量的數據資料分析,但是其執行的效能則取決於所針對的資料型態與演算法的優化程度,而RISC-V的彈性與靈活性剛好可以滿足AI的設計需求,目前已有越來越多的晶片應用商,轉而尋求RISC-V的解決方案。例如GPU晶片大廠NVIDIA就為了突破在高性能運算的瓶頸,而改採RISC-V的指令集,並預計在2020年之後,廣泛地採用新架構。

除此之外,終端裝置也開始有越來越多的AI需求,如「邊緣智慧」等於是物聯網設備的強化版,更進一步增強了RISC-V的市場動能。看好RISC-V的產業支持者,例如CEVA就宣布與SiFive合作,布建其Edge-AI的解決方案;Western Digital希望藉由RISC-V指令集架構,讓記憶體存取與運算更有效率;Microchip已開發出RISC-V微處理器子系統;三星也將RISC-V應用在Exynos Modem通訊晶片和Isocell影像處理器晶片,並擴展至自動輔助駕駛系統(ADAS)與安全監控使用。

市調機構Semico樂觀預測,2025年全球市場將有超過624億顆採用RISC-V的處理器核心。市調機構Tractica也預估,RISC-V全球市場營收至2025年將高達11億美元,營收來源包括採用RISC-V架構之IP、軟體和開發工具,且亞太地區獲利將佔據半數。

客製化CPU竄起 設計驗證需求重新回溫

在RISC-V指令集架構(ISA)的帶動下,處理器客製化的風潮有復甦的跡象,但由於過去十多年來,Arm架構已經在嵌入式處理器市場取得絕對主流的地位,目前CPU設計驗證工具幾乎都是針對Arm架構設計,熟悉CPU驗證工作的第一線工程師,很多也只熟悉Arm架構。如何驗證不是Arm架構的CPU設計,變成一門越來越少人熟悉的技藝。

但需求總會創造供給,在RISC-V的聲勢看漲之際,其生態系統也在快速茁壯。許多EDA業者已經成為RISC-V社群的一員,試圖填補這個空白,並掌握相關商機。

CPU設計驗證沒有標準答案

天底下幾乎找不到沒Bug的CPU設計,特別是通用型CPU,因為在CPU上執行的軟體或應用程式太過多樣化,設計驗證工程師幾乎不可能用窮舉法把CPU會遇到的各種可能狀況都模擬一遍,抓出設計上的Bug,因此通用型CPU的設計驗證,不僅是技術問題,同時也是風險管理問題。因為資源有限,驗證團隊往往只能捉大放小,把不可接受、高風險的重大Bug抓出來修正。然而,漏網之魚總是存在,本以為無關痛癢的小Bug,也可能導致災難性後果。所以,設計驗證要做到什麼程度,驗證項目要如何規畫,不只是技術問題,也考驗團隊的風險評估能力。

主流CPU的架構變得日益複雜,也讓CPU設計驗證變得更困難。英特爾(Intel)出身的SiFive總裁暨執行長Naveed Sherwani就表示,如果要對當代的主流處理器進行設計驗證,一定要有龐大的團隊,而且團隊成員必須是有三到五年以上設計經驗的資深工程師,否則很難做好這項工作。相較之下,從教育需求中誕生的RISC-V,因為其架構相對單純很多,所以CPU的設計驗證也比較容易進行。如果是學生專案作業的水準,一個學習RISC-V架構大約半年左右的大學生,就有能力為自己設計的RISC-V核心進行驗證。

當然,學生作業是一回事,商用等級的CPU還是要用更嚴謹的態度來面對。SiFive的研發團隊擁有15年以上的SoC設計經驗,並且對RISC-V有非常深入的研究跟知識,所以能獲得大量知名客戶的信任跟委託,為其實現RISC-V核心的設計跟SoC整合。統計數據會說話,在2020年上半,SiFive設計定案的SoC創下了不良率為0的傲人成績,遠優於公司創立以來的平均值25DPPM,以及業界平均值100~200DPPM。

EDA工具商擴大接觸RISC-V社群

除了公司研發團隊本身的實力之外,EDA工具的支援逐漸到位,也是RISC-V品質提升一個很重要的原因。由於RISC-V的使用族群跟開發者越來越多,許多EDA公司,如新思(Synopsys)、益華(Cadence)與明導(Mentor),都開始對RISC-V提供更多支援。據了解,晶心科技所使用的設計驗證工具,大多都來自明導,但益華近來也很積極地與RISC-V社群有所接觸。

一般來說,要為客製化CPU進行設計驗證,需要用到指令集模擬器(ISS)、RTL模擬器,以及基於FPGA的硬體模擬系統(Emulator)與原型(Prototyping)建構系統這四種工具。在Arm全面主導嵌入式處理器市場的年代,很多EDA業者對指令集模擬器的布局都慢慢淡化,因為Arm的指令集是標準化的,沒有客製化空間,因此指令集模擬器變成無用武之地的技術。至於FPGA Emulator跟Prototype系統,則因為客戶希望壓縮產品開發時程,要用更快的速度完成硬體除錯,並導入軟硬體同步開發的作業流程,還有一定的需求存在。

Cadence資深產品行銷經理Zaid Rodriguez解釋,在IC設計的作業流程中,有兩個環節會涉及到FPGA,一個是設計模擬,另一個則是原型建構。雖然這兩個步驟都會用到FPGA,但使用的目的不同。

設計模擬是設計驗證的一個階段,IC設計工程師將晶片設計的原始碼移植到FPGA上,主要目的是為了進行除錯,晶片的運作效能則不是重點。因此,對模擬工具來說,重點在於提供完善的移植跟除錯工具,讓工程師可以快速地把RTL碼轉換成可以移植到FPGA上的格式,展開硬體除錯作業。

至於原型建構,主要目的則是為了爭取時效,讓韌體/軟體開發工程師可以在還沒有拿到ASIC、SoC的工程樣本時,就開始為晶片撰寫軟體。是故,原型建構工具的使用者,除了同樣需要快速將設計移植到FPGA上之外,對晶片的效能要求會比模擬來得高很多,還需有完整的軟體除錯工具,以及基本的硬體除錯。理論上,當IC設計進行到原型建構這個階段時,硬體本身應該已經沒有太多Bug,但實務上還是難免會遇到有漏網之魚的情況。

但在RISC-V興起與Arm有限度地開放自訂義指令集之後,EDA工具業者應該會加快腳步,填補這些年客製化CPU需求不足,導至CPU驗證工具出現缺口的情況。

可控軟體環境減輕驗證負擔

然人才需求依然急迫

換個角度來看,CPU的設計驗證之所以困難,跟設計團隊無法預知CPU上將執行什麼軟體有關。但如果設計團隊在開發CPU時,就已經知道在該CPU會執行什麼軟體,情況將大不相同。這正是RISC-V目前的實際應用狀況。

目前大多數的RISC-V應用,都屬於深度嵌入(Deeply Embedded)應用,亦即CPU上不會(或鮮少)執行第三方軟體,而是IC供應商自己開發的軟體或韌體,例如NVIDIA GPU內嵌的Falcon處理器、三星(Samsung)的5G毫米波射頻前端模組,就是典型案例。這使CPU開發團隊面對的是一個「可控」或「可預期」的軟體環境,因此在進行設計驗證的時候,究竟要把哪些項目納入驗證範圍,變得相對明確,進而讓設計團隊有機會窮盡各種可能出現的情況,徹底抓出所有可能存在於CPU設計中的Bug。

但即便如此,要驗證一款客製化CPU,還是一項相當吃重的工作,導致相關人才在客製化CPU蔚為話題的今天,變得非常搶手。例如蘋果(Apple)就持續在台灣開出CPU驗證工程師的職缺,晶心也有相關人才需求。加上EDA產業急於填補過去十多年淡出市場所留下的空白,可以想見的是,擁有CPU設計驗證知識的專業人才,在人力市場上,將變得奇貨可居。

天時/地利/人和俱足 開放處理器來勢洶洶

在摩爾定律逐漸走向尾聲,處理器效能提升速度趨緩的情況下,為了榨出更多效能,以滿足人工智慧(AI)等應用對運算能力的需求,晶片設計者開始在主流的處理器IP之外,探索其他的可能性,例如異質運算、異質整合封裝概念的興起,都與CPU效能成長趨緩,有著密不可分的關係。

領域專用運算架構(Domain Specific Architecture)的觀念,為許多IC設計團隊帶來新的靈感。在標準處理器之外,利用客製化的指令集跟邏輯電路,提高特定某幾類運算任務的執行效率,以便讓處理器在功耗、晶片面積沒有大幅增加的前提下,執行特定任務時能有更高的效能,是領域專用運算架構的核心概念。而開放式CPU架構具有自由、可擴充等特性,正好與領域專用運算架構的想法一拍即合,也促成RISC-V在短時間內爆紅。

開放架構處理器的概念並非RISC-V首創,自2005年起,產業內便曾陸續提出OpenSPARC、OpenRISC、OpenCores等開源指令集架構,但始終面臨相關生態系不易建立,難以受到市場廣泛採用的難題。直到2010年加州柏克萊分校的Krste Asanović教授在其實驗室中開始一系列的開放原始碼研究,RISC-V即是他的RISC CPU研究計畫中的一項。隨後2015年,RISC-V基金會在瑞士成立,以非營利組織的形式推動RISC-V生態系進展,才奠定了RISC-V的基礎。

柏克萊掛保證 RISC-V成功引起產業興趣

晶心科技(Andes)技術長暨執行副總經理蘇泓萌(圖1)提及,柏克萊大學原先為了教學目的而開發出RISC-V,而柏克萊大學作為電腦科學人才培育的重鎮之一,其響亮的名聲,是初步吸引廠商對RISC-V產生興趣的原因。

圖1 晶心科技技術長暨執行副總經理蘇泓萌

與其他的開源硬體相比,RISC-V具有兩方面的優勢,一是簡單易學,二則是良好的商業模式。原本就是為了教學而發展出來的RISC-V,跟其他主流CPU或開源CPU相比,很容易學習上手,有些比較年輕的工程師,很可能在學生時代就已經接觸過RISC-V,因此開發團隊的培養、建構,跟採用主流CPU架構開發晶片相比,難度比較低。而商業模式方面,RISC-V是開源硬體,開發者不用支付授權費、權利金,免於承擔龐大的資金壓力,也讓許多廠商更願意嘗試在晶片中採用RISC-V架構。

SiFive總裁暨執行長Naveed Sherwani(圖2)則從天時、地利、人和的角度,來分析RISC-V快速竄起的原因。在人和方面,Sherwani的觀點與蘇泓萌類似,認為從學術教育需求中誕生的RISC-V,其單純易學、容易客製化的特性,讓RISC-V在推廣時占了很大優勢,這也讓半導體大廠與EDA工具業者看到RISC-V的發展潛力,進而提供支持。這是其他開源或可組態(Configurable)CPU所不曾享有的待遇,也是RISC-V聲勢快速上漲的原因。

圖2 SiFive總裁暨執行長Naveed Sherwani

各國追求半導體自主 RISC-V來得正好

至於在地利方面,由於國際政治的對立加劇,許多國家都需要在談判桌上累積更多籌碼,而半導體作為重要的戰略物資,自然是各國爭相投入扶植的產業。事實上,SiFive在2019年曾經在埃及、巴基斯坦等根本沒有半導體產業的國家舉辦RISC-V論壇,結果動輒吸引數百人、上千人出席,原因也在於各國都想要在半導體領域掌握一定的自主權。對於沒有半導體或資訊科學基礎的國家來說,RISC-V是一個很好的起點。

中國為了追求半導體產業自主,在RISC-V上所投入的資源,更是不在話下。近期中國開放指令生態聯盟才剛舉行CRVS 2020研討會,會中探討了中國RISC-V生態系的未來發展方向,以及中國本土業者在RISC-V處理器設計、驗證、矽智財(IP)與軟體工具等的發展成果,顯示中國有很強烈的企圖心,欲利用RISC-V創造出屬於自己的處理器生態系統。

摩爾定律走向尾聲 運算效能提升要靠客製化

而在天時部分,摩爾定律的進展趨緩,導致處理器效能提升速度大不如前,加上AI應用蓬勃發展,都使得晶片業者必須設法在既有的CPU架構外另闢蹊徑,以滿足客戶對運算效能的需求。

Sherwani就指出,如果處理器的效能提升速度,還能保持十多年前的水準,業界恐怕不會對RISC-V產生這麼大的興趣,因為標準CPU就能滿足應用需求,就算有些電晶體閒置不用或工作效率不彰,對晶片公司跟使用者來說也無所謂。但在摩爾定律走向尾聲,客戶對運算效能的需求卻因為AI暴增之際,晶片業者必然要想辦法讓處理器上每個電晶體都能發揮到極致。針對特定應用進行客製化設計,則是實現這個目標必然要走的路。

蘇泓萌也認為,RISC-V的發展,跟AI有很密切的關係,當AI應用不斷更新,以聲音、人臉辨識與資料中心為主的應用發展比通用的處理器開發更快,須要彈性靈活的解決方案,允許客戶自行修改指令集,才能透過硬體加速滿足AI的效能需求。

應用廣泛的RISC-V便是AI加速的解決方案之一,藉其彈性修改的特性,可依照不同客戶的需求客製化處理器,縮短產品從開發到上市所需的時間。目前RISC-V架構以中低階產品為主,並以美國及中國發展最快。未來RISC-V將走向高階產品,同時持續與學界合作拓展整體生態系。

生態系建立仍為RISC-V最大考驗

基於精簡、可擴充、易於客製等優勢,讓許多廠商對RISC-V躍躍欲試。具代表性的科技公司如英特爾(Intel)、三星(Samsung)及高通(Qualcomm)三大廠商皆對RISC-V處理器IP/解決方案商SiFive投入資金;而聯發科除了是RISC-V基金會的成員之一,也是晶心最大的股東,令市場更加看好RISC-V的發展前景。面對處理器開放架構應用的討論,處理器大廠Arm則選擇部分開放自家處理器架構,因應日益增加的客製化需求。

主流的處理器IP與開放式架構兩陣營各有支持者,而RISC-V架構的出現,提供處理器設計人員在現有IP之外,另一個更具彈性的選擇。基於開源的核心宗旨,RISC-V的開放性可加速創新。然而硬體架構仍須搭配編譯器與軟體工具支援,才能發揮其作用。因此RISC-V的挑戰便在於建立一套完整的支援系統,藉由建立生態系來穩固市場定位,期望未來與主流處理器並駕齊驅。

為了建立RISC-V生態系,學界與業界人士成立基金會共同推動,RISC-V社群中的處理器廠商之間除了各自的策略布局,同時反映了半導體產業的競合關係。蘇泓萌表示,RISC-V社群的廠商間呈現合作性競爭(Co-opetition)關係,競爭對手與合作對象間並沒有明顯的界線。生態圈中存在競爭,但是上下游廠商,甚至競爭對象還是可以合作把餅做大,透過互相支援拓展RISC-V生態系。

定義/邏輯驗證精準又簡單 客製化指令加速特定領域應用

隨著從邊緣設備到雲端服務的應用需要處理越來越多的數據,現今對於SoC運算能力的要求也越來越高。此外,系統也必須在非常短的時間內對這些數據(聲音、影像、動態影片、光學雷達、紅外線雷達以及聲納等)進行分析、處理並在一定時間內採取相對的回應。儘管這些應用對硬體常要求大量的運算能力,但它們卻也同樣受到功耗和成本的限制,而一般標準的CPU通常很難滿足這些要求。如果想在特殊的應用或演算法上加快運算的速度,SoC需要一種更好的方法來達到這些目標。

客製化指令加速運算

在運算加速的方法和演進中,主要可以歸納成三種方式。一種是透過外部的硬體加速器,最好的例子之一是加密引擎;第二種是指令集架構(ISA)的標準擴充集,例如RISC-V ISA中的M、P和V擴充集;最後一種是用戶自定義的客製化指令,如RISC-V ISA開放給設計工程師添加他們自己的客製化指令。

表1比較了這三種類型的運算加速。可以看到自定義的客製化指令沒有啟動延遲(Start-up Latency),同時擁有指令專有的優勢,並能夠共用較多的硬體資源來節省大小。在過去將新的指令整合到現有的標準CPU IP較麻煩的是設計流程。這種整合除了要求設計工程師要了解CPU的架構和其工具鏈,以便有效地定義所需的指令之外,工程師更要了解如何將新設計的邏輯電路整合到現有的SoC、仿真和驗證的流程中。廠商如晶心科技提供的Andes Custom Extension(ACE)和客製優化指令開發工具(COPILOT)之EDA等級的客製化指令開發工具來幫忙客戶解決這些問題,使設計工程師可以快速依照他們的需求定義客製化指令,而ACE和COPILOT支援晶心RISC-V V5全系列的核心。

如果將數據密集型運算的加速加以分析,可以將其分為兩部分:數據I/O和運算加速。針對第一部分,設計工程師可以用適當的DMA引擎加上Double Buffers,以減少將數據傳送到加速單元或從加速單元傳送出的等待時間。第二部份運算加速則可以用ACE開發自定義的客製化指令來增強效能,例如定義一個指令來完成矩陣卷積或兩個64×8向量的內積。另外,ACE還可以從CPU生成客製化接口,來控制現有的硬體引擎進行快速的資料交換,例如,在一個週期內向外部硬體引擎發送90位元的訊號。

在這邊也列舉了三種典型的演算法來展示客製化指令所帶來在效能及功耗上的改善。表2列舉了有限脈衝響應(FIR)過濾器、32位循環冗餘校驗(CRC32)和三重數據加密標準(3DES)這些演算法。他們透過ACE添加客製化指令後,得到從20倍到300倍不等的效能提升及功耗降低。

ACE流程設計指令簡易

在ACE的流程設計指令,工程師只需要提供少許的資訊,例如指令名稱、屬性、客製化的硬體資源、運算本身的C語義以及ACE其他和客製化指令相關的參數。ACE自動整合開發工程師所提供的Concise Verilog,該Verilog只需提供客製化指令本身的邏輯而不必擔心與CPU Pipeline相關的接口訊號和控制邏輯。像晶心EDA等級的COPILOT工具會依照這些資訊自動生成擴展的RTL、高精確的模擬器以及工具(編譯器、彙編器/反彙編器和調試器);這些擴展元件和基礎元件結合後,就產生一個新的CPU及其所有相關工具。此外,COPILOT可以產生測試環境來交叉檢查擴展的Instruction Set Simulator(ISS)和RTL,以幫助工程師驗證其設計的客製化指令邏輯是否正確。

COPILOT因為與晶心Eclipse-based的Integrated Development Environment(AndeSight IDE)高度整合,開發工程師可以容易地利用AndeSight中的現有提供給標準RISC-V的功能,這些包括高精確的模擬器、程式的編譯、除錯和軟體效能Profiling工具,來在新產生的RISC-V核心上更快進行應用軟體的開發和驗證。

ACE提供的多種功能可以讓工程師設計適合其特定需求的客製化指令,例如ACE支援單週期或多週期的純量(Scalar)指令、For循環或Do-while循環的向量(Vector)指令、以及可立即Retire並在後台持續執行客製化指令的Background選項。此外,ACE支援多種Operands類型:(1)一般CPU都有的標準Operand,像是Immediate、通用暫存器(GPR)和從CPU存取的Baseline Memory;(2)具有任意寬度和數量的客製化暫存器(ACR)、客製化記憶體(ACM)和客製化端口(ACP),以及(3)隱含Mnemonic在指令中的Operand,進而減少客製化指令所需要的編碼空間。另外,根據設計工程師在ACE Script中定義的資訊,ACE會自動決定分配Opcode,然後生成新的工具和SystemC的模擬器。ACE也提供可以優化硬體資源的邏輯共享選項,並自動產生用於模擬時的波形控制文件。而COPILOT自動生成並整合Concise Verilog的邏輯包括指令解碼、Operand Mapping、Dependence檢查、輸入參數的對接和輸出參數的更新等。

ACE開發流程如圖1所示。如果開發工程師己經確定應用軟體中需要加速的代碼,就可以直接定義ACE指令來替換此段代碼。接下來,設計工程師再用Profiling評估新客製化指令增加的效能,以確定其是否已達到所需的週期預估值。如果目標尚未達到,則重複進行此步驟,直到帶有客製化指令的應用程式達到預定的目標為止。一旦應用程式已經達到預期的效能,設計工程師就可以進到下一步去實現ACE客製化指令邏輯的RTL,並進行評估以確保最終的功耗、效能和面積滿足整體系統的要求。如果沒有,則可以透過再次分析應用程式並以添加或修改客製化指令來重複之前的步驟,直到滿足所有的條件為止。

圖1 ACE開發流程

透過設計客製化指令來減少執行週期,除了可以提高性能外,還可以進一步降低功耗。因為多條指令需要多次重複執行獲取、解碼和退出的運算過程,而客製化指令僅需執行一次獲取、解碼和退出週期即可。此外,透過設計專用的邏輯電路來執行客製化指令也能更加優化功耗。

設計ACE指令相當簡單。如圖2所示,ACE定義文件madd32.ace Script提供設計一道客製化指令所需的資訊:「insn」、「Operand」、「csim」和「Latency」。在這個例子中,ACE Script包含客製化指令的名稱「madd32」外,它也列出客製化指令中Operand的名稱和其屬性:輸入、輸出、輸出入、通用暫存器或immediate等;另外它還包括客製化指令在執行過程中所需週期的估計值,而此文件還用C語言來描述客製化指令集在模擬器csim會需要的指令語義。ACE也會自動生成如圖2中的Intrinsic Function「acc_madd32()」。此外,ACE設計者只需要在Concise Verilog的//ACE_BEGIN和//ACE_END之間提供客製化指令本身的邏輯,即可不必提供流水線控制、ACE和CPU接口等細部的電路邏輯,這些都會由COPILOT自動處理。在原來的應用程序代碼(如圖3代碼所示)中,本來用於執行演算法的C代碼中的For循環可以用新的函數「ace_madd32()」以及Operand來替換。

圖2 ACE...

IAR Systems在台營運 就近提供原廠服務

愛亞系統(IAR Systems)是全球嵌入式系統開發工具商,總公司位於瑞典烏普薩拉,全球有超過46,000公司、150,000以上的用戶。IAR Systems日前宣布台灣分公司正式直接營運,以回饋用戶長期的信任與支持,同時為客戶提供更有效率的服務、更優惠的價格以及原廠技術支援。這是IAR Systems亞太區繼日本、南韓、中國後的第四間辦公室。

長期以來,IAR Systems 透過亞洲其他分公司與本土經銷商提供產品與服務給台灣客戶。如今,在公司全球化策略以及台灣MCU市場的強大淺力下,決定在台成立直接分公司。除了全球的好表現外,IAR Systems在亞太區的表現也不遑多讓。在日本,前50大的製造公司有47間利用IAR的產品進行編譯與程式碼優化,創造出了非常多享譽國際的高品質產品。亞太區負責人上村清史表示,在過去的代理銷售下,該公司與客戶建立了深厚的關係。台灣對IAR來說是非常重要的市場,很期待藉由台灣分公司的成立,進一步擴大IAR亞太市場的版圖。

IAR Systems台灣業務經理林其禹表示,在台灣,很多消費者知道IAR,但卻不清楚IAR能帶給企業怎麼樣的價值。更直接的跟客戶溝通也是IAR Systems在台灣成立分公司的主要目的之一。IAR Systems專注於提供用戶高品質的體驗,除了產品本身能編譯出業界較優化的程式碼之外, 也發行了取得國際認證的功能安全版本,能夠大大減輕車用電子、醫療器材等高安全要求產業的認證負擔。另外,該公司看中RISC-V架構在亞太區的成長性,發行了目前市場上商業級RISC-V的系統開發工具。進入台灣後,也將提供更完整的原廠技術支援以及定期的教學課程給台灣的客戶。

IAR Systems 希望藉由在台設立分公司,更加貼近台灣客戶的需求,利用自身優異的產品性能幫助台灣企業創造更優質的產品、躍上國際舞台以取得成功。更多IAR請洽官網https://www.iar.com/

晶心新推Superscalar處理器

晶心科技日前宣布將推出AndesCore 45系列處理器內核,配備高效的循序執行及超純量管線(In-order, Superscalar Pipeline)設計,可針對各種需高性能且低功耗的即時嵌入式系統,如5G、車載訊息娛樂系統(IVI)、先進駕駛輔助系統(ADAS)和固態硬碟(SSD)提供解決方案。晶心計畫於2020年第一季向早期採用的客戶提供45系列的內核。

晶心科技總經理林志明表示,45系列是晶心在發展高性能領域的重要里程碑,特別是現有的RISC-V指令集以及隨之而來的市場驅動力,該公司很多已簽約客戶都在詢問何時會將雙發射的專業技術引入到RISC-V內核,很高興研發團隊已成功將這項技術導入產品中。

高性能嵌入式系統已經有不少的應用,但是客戶在既有微處理器架構和固定指令的處理器生態系統上依然希望能有更多的自由度,AndesCore 45系列就是專門為此類需求提供的解決方案。

45系列中將推出32位元A45/D45/N45和64位元AX45/DX45/NX45,其分別衍生於晶心成熟的25系列內核,並支援所有最新的RISC-V規格、系統平台組件、以及晶心14年來所研發的生態系統。45 A-系列可支援Linux作業系統並最多可擴展到四個內核;45 N-系列則支援RTOS的應用,而45 D-系列則支援RISC-V的SIMD/DSP指令集(P擴充指令集草案)。所有45系列內核均採用循序執行的8級雙發射超純量技術,並透過晶心的儲存流水線設計,可在不犧牲執行速度的情況下執行ECC,並且可選擇符合IEEE754的單精和雙精度浮點運算單元(FPU)。AX45內核在ECC開啟的情況下,依然可以在28nm製程的PVT邊界條件下達到1.2GHz的頻率,使其成為該性能級別上最佳的CPU設計之一;而極為優越的流水線技術還使其達到良好的5.4 Coremark/MHz高性能水準。這些循序執行處理器,可增強代碼執行的即時準確性,當與具有向量優先序的平台級中斷控制器(PLIC)配合使用時,45系列內核適於對響應時間和即時準確性要求高的嵌入式應用。

晶心RISC-V平台獲Amazon FreeRTOS資格

RISC-V基金會創始白金會員晶心科技,為提供32及64位元高效能、低功耗、精簡RISC-V CPU處理器核心的供應商,日前宣布其Corvette-F1 N25平台成為取得Amazon FreeRTOS資格的RISC-V平台之一。Amazon FreeRTOS是適用於Amazon Web Services(AWS)雲端平台微型控制器的開放原始碼作業系統,可使小型、低功率的邊緣裝置易於進行程式設計、部署、保護、連接及管理。透過晶心科技的RISC-V平台,開發者可以善用Amazon FreeRTOS的功能和優勢。

晶心科技技術長暨執行副總經理蘇泓萌表示,物聯網(IoT)和結合人工智慧的AIoT將成為RISC-V CPU核心的重點市場,借助Amazon FreeRTOS和晶心RISC-V平台的優勢,提供使用Amazon FreeRTOS的開發者更多開發平台選擇,並為客戶推出更強大的RISC-V物聯網解決方案。

隨著更多技術在網際網路活躍發展,物聯網市場的多元應用日增月益。RISC-V指令集架構(ISA)提供更佳的靈活度、延展性、擴充性,為物聯網帶來更多新的可能性,也幫助開發者在持續成長的市場中能更輕易設計精簡的物聯網硬體裝置。晶心科技藉由將RISC-V平台與Amazon FreeRTOS、AWS IoT Greengrass、AWS IoT Core等解決方案結合,可以幫助開發者創建基於RISC-V全面且具競爭力的物聯網系統。