ISA

看準算力供不應求 全球RISC-V聲勢喊漲

由於算力、邊緣、人工智慧(AI)等需求暴增,如供應鏈針對軟體及IP需求提升,加上新興應用/場域亦需更高階的算力才得以實現。同時,RISC-V的成本、技術及策略風險亦為業界關注的焦點,因此,考量到諸多優點,越來越多全球業者逐步採用RISC-V架構,如市場調研機構Tractica便預估其全球市場營收至2025年將達11億美元。

全球RISC-V生態系的發展,不難想像從開源軟體、硬體到CPU核心的延伸,如何用同一架構且較低成本的方式達到差異化,為各方首重的課題。拓墣產業研究院資深分析師姚嘉洋以中國為例,指出中國RISC-V發展動態值得留意,他認為雲端服務供應商(CSP)會扮演推動發展趨勢的要角,以阿里巴巴旗下半導體商平頭哥為例,其致力於推動開源架構提供給晶片及系統業者進行差異化開發,因此中國晶片及系統業者皆能因此受益。另一方面,姚嘉洋以芯來科技為例,該公司於2019年與兆易創新合作,推出首款RISC-V MCU晶片,並於2020年獲小米投資,可望加速中國RISC-V生態系的拓展。

拓墣產業研究院資深分析師姚嘉洋表示,中國CSP業者將為驅動RISC-V趨勢的推手

台灣RISC-V聯盟副會長兼晶心科技總經理林志明則引述NVIDIA執行長黃仁勳的說法指出,AI提供動力的矽晶片,其性能將每兩年增加一倍以上;若以曲線圖表示,從摩爾定律與市場需求曲線相距越來越大,不難看出整個產業針對算力的供應及應用嚴重缺乏。據此,RISC-V基於開源指令集的諸多特點,如設計簡單、可模組化等特性,可以企及更高的算力,因此已然成為SoC在設計時納入考量的選項。若以應用發展來看,目前最早進入量產的領域包含指紋辨識及藍牙等應用,無論是邊緣、AI、IoT等領域皆有市場需求,因此未來林志明預估,全球採用RISC-V的晶片將會越來越多。

台灣RISC-V聯盟副會長兼晶心科技總經理林志明表示,期許台灣企業投入RISC-V聯盟,進而可於國際場域凝聚話語權

放眼RISC-V近期發展,根據市場調研機構Semico的預測,2025年全球市場將有超過624億顆採用RISC-V的處理器核心。林志明補充,全球RISC-V聯盟在近一年內增加超過220個會員,目前總數已來到750個。放眼聯盟成長曲線斜率越來越高,顯示全球參與RISC-V聯盟以及採用RISC-V設計方面越來越積極,因此他對此樂觀表示,將RISC-V將可望成為ISA主流選擇趨勢。不過針對台灣現階段參與狀況,林志明坦言,以現階段參與全球聯盟成員數僅有六個的景況,於國際影響力較有限,因此他也期待各界可踴躍加入,進一步掌握話語權。

瑞薩採用晶心科技RISC-V 32位元CPU核心

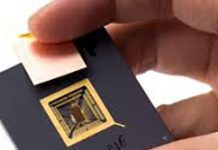

瑞薩電子日前與晶心科技(Andes Technology)進行技術IP合作。晶心科技提供以RISC-V為基礎的嵌入式CPU核心,以及相關系統單晶片(SoC)開發環境的供應商。瑞薩選擇AndesCore IP之32位元RISC-V CPU核心,嵌入其全新的ASSP中,該產品將於2021年下半年開始為客戶提供樣品。

瑞薩採用晶心科技RISC-V 32位元CPU核心

晶心科技總經理林志明表示,MCU供應商瑞薩電子已經將晶心的RISC-V核心設計到其預燒錄的特殊應用標準產品中。瑞薩和晶心都有相同的願景,就是RISC-V將成為SoC的主流CPU指令集架構(ISA),並欣然迎接RISC-V時代。這不但是晶心科技代表性的里程碑,也代表開放原始碼RISC-V ISA作為主流運算引擎時代的來臨。瑞薩的客戶將會得益於為21世紀運算需求而建構的現代化ISA。

瑞薩物聯網與基礎設施事業部執行副總裁兼總經理Sailesh Chittipeddi則認為,晶心科技的RISC-V核心IP,提供可擴展的性能範圍,可選擇的安全功能,以及客製化的選項,讓瑞薩能夠對未來的特殊應用標準產品,提供創新的解決方案。客戶如果正在為現有或新興的應用產品,尋找經濟的替代方案,就會因此而得益於上市時程縮短與開發成本降低。

瑞薩以RISC-V核心架構為基礎的預燒錄設計ASSP晶片,在交貨時還結合專用的使用者介面工具,來設定應用產品的可程式參數,可提供客戶完整、最佳化的解決方案。這項功能可消除初期對RISC-V開發和軟體的投資障礙。此外,由瑞薩在各地具有特殊專業知識的合作夥伴所組成的大規模網路,將可提供集中化的客戶支援。

Microchip發布RISC-V開發套件

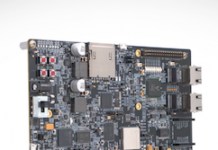

免費和開放式的RISC-V指令集架構(ISA)的應用日益普遍,推動了經濟、標準化開發平臺的需求,該平臺嵌入RISC-V技術並善用多樣化的生態系統。為滿足這一需求,Microchip推出基於RISC-V的SoC FPGA開發套件。這款Icicle Kit開發套件專為業界領先的低功耗、低成本、基於RISC-V的PolarFireSoC FPGA打造,彙集了眾多的Mi-V合作夥伴,協助多樣產業客戶加速設計部署和商業應用。

Microchip發布RISC-V之SoC FPGA開發套件

Microchip FPGA業務部副總裁Bruce Weyer表示,隨著 RISC-V 軟體和矽晶片在市場上的廣泛應用,Microchip正在引領處理器設計的革命性轉型。我們正在透過一個低成本評估平臺消除進入門檻。藉由這一平臺,嵌入式工程師、軟體設計人員和硬體開發人員可以同時利用開放式 RISC-V ISA 的優點與 Microchip業內最佳尺寸外型、散熱和低功耗特性的PolarFire SoC FPGA 進行設計。

RISC-V國際董事會副董事長、2017 年圖靈獎獲得者David Patterson指出,售價不到 500 美元的低功耗RISC-V開發板讓人眼前一亮。Microchip Icicle工具套件內置 PolarFire SoC,將加速 RISC-V 軟體生態系統的發展,對需要低功耗中階 SoC FPGA 的應用來說是個好消息。

設計人員現在可以開發和評估即時操作系統(RTOS)、除錯器、編譯器、模組化系統(SOM)和安全解決方案等廣泛的RISC-V生態系統產品,進而輕鬆部署基於RISC-V的可程式設計SoC FPGA。Mi-V RISC-V合作夥伴生態系統是Microchip和眾多協力廠商為全面支持RISC-V設計而開發的一個不斷擴展、全面的工具套件和設計資源。

Icicle工具套件以擁有25萬個邏輯元件的 PolarFire SoC 為中心,包括 PCIe連接器、mikroBUS插槽、雙 RJ45 連接器、Micro-USB 連接器、CAN匯流排連接器、Raspberry Pi 插針連接器、JTAG埠和SD卡介面,為開發人員提供了功能齊全的開發平臺。Microchip 經過設計、驗證和測試的功耗管理和時脈設備、Ethernet PHY(VSC8662XIC)、USB 控制器(USB3340-EZK-TR)和電流感測器(PAC1934T-I/JQ)為開發板提供支援。

PolarFire SoC FPGAs 的總功耗比同類競爭產品低 50%。透過使用SoC FPGAs,開發人員還可以通過元件固有的升級能力和在單個晶片上整合功能的能力,獲得更多的客製化和差異化機會。PolarFire SoC FPGA 系列提供多種封裝和尺寸,更容易平衡應用的效能與功耗,使客戶能夠在小至11×11毫米的封裝尺寸上實施解決方案。Microchip的Polar...

洞悉環境空氣腐蝕程度 電子產品使用可靠性有解

一般來說,空氣污染通常有許多來源,其污染物含有豐富的氧化物、氯化物與硫化物能導致許多工業元件上其各種合金材料的嚴重腐蝕。

而含硫的氣體,如硫化氫(H2S)與二氧化硫(SO2)是一般最主要造成電子設備腐蝕的腐蝕性氣體。然而,在日趨嚴重的環境污染與2003年歐盟頒布管制有害物質禁用指令(Restriction of Hazardous Substances Directive, RoHS)後,對於高階電子設備相關材料的選擇更是非常關鍵。

即使在惡劣環境下,也要確保電子設備的可靠性需求是足夠的。因此,了解電子產品所處現場/終端環境的空氣腐蝕程度就顯得非常重要。

如何掌控空氣腐蝕程度?有實驗室如宜特提供了解決方案,藉監控空氣品質(Air Quality Monitoring, AQM)量測現場/終端的空氣腐蝕程度(圖1),並將其結果反饋至加速腐蝕試驗,如混合流動性氣體(Mixed Flowing-Gas, MFG)與硫磺蒸氣(Flower of Sulfur, FoS)試驗,藉此有效驗證產品保固期間是否將腐蝕失效。

圖1 現場/終端環境空氣腐蝕程度監控

本文將介紹何謂ANSI/ISA 71.04及其測試方法為何,以及產品驗證實驗室時常替客戶執行的兩項加速腐蝕試驗—混合流動性氣體與硫磺蒸氣試驗。

國際標準界訂空氣腐蝕程度

ANSI/ISA 71.04是空氣腐蝕等級的標準。由美國國家標準協會(American National Standards Institute, ANSI)認證的國際自動化協會(International Society of Automation, ISA)71.04-2013標準,將現場/終端環境的空氣腐蝕嚴重性分類為四個等級,其包含G1/G2/G3與GX。

測試方式為藉由使用一預處理的純銅和純銀的金屬試片,曝露在現場/終端的環境一個月的時間後,從其金屬試片所測得的空氣傳播污染物的腐蝕厚度/速率,來區分不同的嚴重性程度(表1)。

一般而言,當現場/終端環境的空氣腐蝕程度大於或等於G2等級時,其腐蝕影響的程度是可以被測量的,且腐蝕可能會是決定電子設備可靠度的一項關鍵因子。而腐蝕的失效模式可區分為兩類,包括銅與銀的腐蝕(圖2)。

圖2 在資料中心的訊息設備故障中,兩種常見的腐蝕失效模式

高階旗艦型加速腐蝕試驗:混合流動性氣體

MFG測試是一種實驗室的環境應力測試,其目的是在於模擬受污染的工業環境。一般來說.有許多可控制的參數,包括溫度、相對濕度、腐蝕性氣體種類(如硫化氫、氯氣、二氧化氮、二氧化硫、氨氣與臭氧等)、氣體濃度和氣體流速等。

此外,試驗箱體內的腐蝕性氣體不斷被新鮮的腐蝕性氣體所替換。由於可控制的試驗參數眾多,複雜的試驗設備架設和持續不斷的腐蝕性氣體流動。因此,MFG具備有很高的可用性來模擬現場/終端環境的腐蝕。然而,MFG試驗的缺點是測試成本高,並且不能被業內的所有供應商廣泛採用。

由於氣體反應性限制(硫化氫),且必須存在氯氣或臭氧來驅動爬行機理,MFG測試適合複製銅的腐蝕和爬行/蠕變腐蝕(Creep...

定義/邏輯驗證精準又簡單 客製化指令加速特定領域應用

隨著從邊緣設備到雲端服務的應用需要處理越來越多的數據,現今對於SoC運算能力的要求也越來越高。此外,系統也必須在非常短的時間內對這些數據(聲音、影像、動態影片、光學雷達、紅外線雷達以及聲納等)進行分析、處理並在一定時間內採取相對的回應。儘管這些應用對硬體常要求大量的運算能力,但它們卻也同樣受到功耗和成本的限制,而一般標準的CPU通常很難滿足這些要求。如果想在特殊的應用或演算法上加快運算的速度,SoC需要一種更好的方法來達到這些目標。

客製化指令加速運算

在運算加速的方法和演進中,主要可以歸納成三種方式。一種是透過外部的硬體加速器,最好的例子之一是加密引擎;第二種是指令集架構(ISA)的標準擴充集,例如RISC-V ISA中的M、P和V擴充集;最後一種是用戶自定義的客製化指令,如RISC-V ISA開放給設計工程師添加他們自己的客製化指令。

表1比較了這三種類型的運算加速。可以看到自定義的客製化指令沒有啟動延遲(Start-up Latency),同時擁有指令專有的優勢,並能夠共用較多的硬體資源來節省大小。在過去將新的指令整合到現有的標準CPU IP較麻煩的是設計流程。這種整合除了要求設計工程師要了解CPU的架構和其工具鏈,以便有效地定義所需的指令之外,工程師更要了解如何將新設計的邏輯電路整合到現有的SoC、仿真和驗證的流程中。廠商如晶心科技提供的Andes Custom Extension(ACE)和客製優化指令開發工具(COPILOT)之EDA等級的客製化指令開發工具來幫忙客戶解決這些問題,使設計工程師可以快速依照他們的需求定義客製化指令,而ACE和COPILOT支援晶心RISC-V V5全系列的核心。

如果將數據密集型運算的加速加以分析,可以將其分為兩部分:數據I/O和運算加速。針對第一部分,設計工程師可以用適當的DMA引擎加上Double Buffers,以減少將數據傳送到加速單元或從加速單元傳送出的等待時間。第二部份運算加速則可以用ACE開發自定義的客製化指令來增強效能,例如定義一個指令來完成矩陣卷積或兩個64×8向量的內積。另外,ACE還可以從CPU生成客製化接口,來控制現有的硬體引擎進行快速的資料交換,例如,在一個週期內向外部硬體引擎發送90位元的訊號。

在這邊也列舉了三種典型的演算法來展示客製化指令所帶來在效能及功耗上的改善。表2列舉了有限脈衝響應(FIR)過濾器、32位循環冗餘校驗(CRC32)和三重數據加密標準(3DES)這些演算法。他們透過ACE添加客製化指令後,得到從20倍到300倍不等的效能提升及功耗降低。

ACE流程設計指令簡易

在ACE的流程設計指令,工程師只需要提供少許的資訊,例如指令名稱、屬性、客製化的硬體資源、運算本身的C語義以及ACE其他和客製化指令相關的參數。ACE自動整合開發工程師所提供的Concise Verilog,該Verilog只需提供客製化指令本身的邏輯而不必擔心與CPU Pipeline相關的接口訊號和控制邏輯。像晶心EDA等級的COPILOT工具會依照這些資訊自動生成擴展的RTL、高精確的模擬器以及工具(編譯器、彙編器/反彙編器和調試器);這些擴展元件和基礎元件結合後,就產生一個新的CPU及其所有相關工具。此外,COPILOT可以產生測試環境來交叉檢查擴展的Instruction Set Simulator(ISS)和RTL,以幫助工程師驗證其設計的客製化指令邏輯是否正確。

COPILOT因為與晶心Eclipse-based的Integrated Development Environment(AndeSight IDE)高度整合,開發工程師可以容易地利用AndeSight中的現有提供給標準RISC-V的功能,這些包括高精確的模擬器、程式的編譯、除錯和軟體效能Profiling工具,來在新產生的RISC-V核心上更快進行應用軟體的開發和驗證。

ACE提供的多種功能可以讓工程師設計適合其特定需求的客製化指令,例如ACE支援單週期或多週期的純量(Scalar)指令、For循環或Do-while循環的向量(Vector)指令、以及可立即Retire並在後台持續執行客製化指令的Background選項。此外,ACE支援多種Operands類型:(1)一般CPU都有的標準Operand,像是Immediate、通用暫存器(GPR)和從CPU存取的Baseline Memory;(2)具有任意寬度和數量的客製化暫存器(ACR)、客製化記憶體(ACM)和客製化端口(ACP),以及(3)隱含Mnemonic在指令中的Operand,進而減少客製化指令所需要的編碼空間。另外,根據設計工程師在ACE Script中定義的資訊,ACE會自動決定分配Opcode,然後生成新的工具和SystemC的模擬器。ACE也提供可以優化硬體資源的邏輯共享選項,並自動產生用於模擬時的波形控制文件。而COPILOT自動生成並整合Concise Verilog的邏輯包括指令解碼、Operand Mapping、Dependence檢查、輸入參數的對接和輸出參數的更新等。

ACE開發流程如圖1所示。如果開發工程師己經確定應用軟體中需要加速的代碼,就可以直接定義ACE指令來替換此段代碼。接下來,設計工程師再用Profiling評估新客製化指令增加的效能,以確定其是否已達到所需的週期預估值。如果目標尚未達到,則重複進行此步驟,直到帶有客製化指令的應用程式達到預定的目標為止。一旦應用程式已經達到預期的效能,設計工程師就可以進到下一步去實現ACE客製化指令邏輯的RTL,並進行評估以確保最終的功耗、效能和面積滿足整體系統的要求。如果沒有,則可以透過再次分析應用程式並以添加或修改客製化指令來重複之前的步驟,直到滿足所有的條件為止。

圖1 ACE開發流程

透過設計客製化指令來減少執行週期,除了可以提高性能外,還可以進一步降低功耗。因為多條指令需要多次重複執行獲取、解碼和退出的運算過程,而客製化指令僅需執行一次獲取、解碼和退出週期即可。此外,透過設計專用的邏輯電路來執行客製化指令也能更加優化功耗。

設計ACE指令相當簡單。如圖2所示,ACE定義文件madd32.ace Script提供設計一道客製化指令所需的資訊:「insn」、「Operand」、「csim」和「Latency」。在這個例子中,ACE Script包含客製化指令的名稱「madd32」外,它也列出客製化指令中Operand的名稱和其屬性:輸入、輸出、輸出入、通用暫存器或immediate等;另外它還包括客製化指令在執行過程中所需週期的估計值,而此文件還用C語言來描述客製化指令集在模擬器csim會需要的指令語義。ACE也會自動生成如圖2中的Intrinsic Function「acc_madd32()」。此外,ACE設計者只需要在Concise Verilog的//ACE_BEGIN和//ACE_END之間提供客製化指令本身的邏輯,即可不必提供流水線控制、ACE和CPU接口等細部的電路邏輯,這些都會由COPILOT自動處理。在原來的應用程序代碼(如圖3代碼所示)中,本來用於執行演算法的C代碼中的For循環可以用新的函數「ace_madd32()」以及Operand來替換。

圖2 ACE...

施耐德成為ISA全球網路安全聯盟創始成員

施耐德電機(Schneider Electric)日前以首位創始成員的身分加入國際自動化協會(ISA)所成立的全球網路安全聯盟(Global Cybersecurity Alliance),成為參與制定全球網路安全規範的標竿企業,在原有的基礎上,更進一步保障客戶的資訊安全。

施耐德電機明瞭資訊安全的重要性,主動與ISA接洽,表達其對資安的重視與關心,期望在國際網路安全貢獻心力。為積極應對近年來不斷增長、變化的網路威脅,國際自動化協會遂成立了全球網絡安全聯盟,成員包括終端客戶公司、技術及系統供應商、IT基礎架構供應商、服務提供商、系統整合商和其他組織,以提高全球製造業和關鍵基礎設施及流程對網路安全危機的意識與防備。

施耐德電機Schneider Electric工業自動化事業部資深副總裁Nathalie Marcotte表示,我們一直致力以安全、高效及可靠的方式協助客戶實現利潤最大化,這也表示施耐德電機Schneider Electric會盡一切努力保護客戶免於日益增長的網絡攻擊。全球網路安全聯盟規模龐大,且其開放的主張與我們不謀而合,施耐德電機Schneider Electric以創始會員的身分加入此聯盟,將增強我們進行共同偵測、預防和應對網路威脅的能力,同時進一步協助不同產業的客戶保護其資產及業務並提升營運績效。

ISA執行董事Mary Ramsey表示,隨著資訊科技的進步,產業開始面臨不斷升級、創新又危險的網路攻擊,每個致力於保障全球基礎架構的組織都應該合作以改善終端用戶的自我保護。我們很高興施耐德電機Schneider Electric能夠成為我們的第一位創始成員,施耐德電機Schneider Electric及其他的創始成員皆承諾並致力使客戶營運安全有保障,同時提升績效。未來,我們更期待與各種不同的組織合作以推動必要的改革。

具效能/安全/成本優勢 RISC-V躋身晶片製造新利器

穩定性為ISA發展關鍵

RISC-V之目標是從其他處理器ISA錯誤中汲取教訓。關鍵是穩定性,包括指令集和內核,以及晶片設計人員、編譯器製造商、作業系統架構師和開發工具提供商等。這對於鼓勵工程師盡可能多在產業鏈中使用這種開源技術,使更強大處理器內核得到更多獲取和使用至關重要。特定應用開發人員可以使用最小記憶體和功耗來優化其固化的ISA代碼,但仍可擴展並與未來設備相容。這允許處理器內核開發人員應對指令集的各種不同實施方式,從簡單管線到具有多階和無序執行管線。這些會具有不同的延遲、尺寸大小和功耗,但彼此之間都具有底層相容性,以及生態圈中包含的工具。

在整個生態圈中提供這種穩定性是新指令集的關鍵。它的設計考慮了32位元、64位元和128位元位址空間,因此可以保持它們之間的相容性。該架構還專門設計具有可延伸性,以便為晶片製造商提供差異化和未來應用場景所需的客製化服務,但ISA的基礎仍然是絕對不受影響。

ISA開放性使軟體架構更有影響力

128位元ISA依然未確定,因為在嵌入式系統中,如此之大儲存容量幾乎沒有實際意義。但是,該體系架構將支援更大的位址空間這一事實凸顯了其前瞻性思維方式。這意味著為RISC-V編寫或移植到其上的軟體將永遠能夠在所有類似的RISC-V內核上運作,為軟體管理員提供了堅實的基礎,可以保護他們的軟體投資。由於ISA是開放的,因此可以開發多種硬體實施方案,因此軟體架構可以在最終硬體實施中變得更有影響力。

對於硬體設計人員之輸入會使RISC-V內核更加以軟體為中心,這導致出現了許多採用ISA的處理器內核,以及大量基於這些內核的系統單晶片(SoC),Codasip、Syntacore、Hex Five和T-Head都開發相應的內核,而SiFive則推出了一系列32位元和64位元SoC。

SiFive由Yunsup Lee(RISC-V最初創建者之一)共同創立,作為SoC平台家族,於2017年推出首個RISC-V內核,並增加了對內核和晶片支援(圖1)。這些元件採用28nm製程,用於64位元多核Linux實施,或者採用180nm製程,適用於具有多種周邊設備的32位元低成本物聯網市場。

圖1 SiFive的U500 64位元多核開源處理器。

該公司的Freedom平台包括完整的軟體規格、用於開發作業系統的板級支援包(BSP)、開發板和基礎晶片等,允許客戶創建自己的晶片增強型設計和客製化產品。Freedom U500家族是一款完全支援Linux的嵌入式應用處理器,採用多核RISC-V CPU,運作速度為1.6GHz甚至更高,支援加速器和快取記憶體一致性,適於機器學習、儲存和網路等應用。它支援標準的高速周邊設備,包括PCIe 3.0、USB 3.0、Gb乙太網路和DDR3/DDR4。

Freedom E300家族為設計用於物聯網和可穿戴設備市場的嵌入式微控制器(圖2)。基於Freedom E310的HiFive1相容Arduino的RISC-V開發套件採用SiFive的E31 CPU Coreplex,是一款高性能32位元RV32IMAC內核,能夠以超過320MHz的頻率運作(圖3)。

圖2 採用RISC-V ISA的E300開源32位元MCU家族。

圖3 HiFive1 RISC-V開發套件。

SiFive還將RISC-V指令集用於據稱是世界上最小嵌入式處理器內核。S2內核IP家族是一個可配置內核,可以小到只具有13,500個邏輯閘(在RV32E 32位元版本狀況下)。S21 64位元嵌入式內核具有獨立指令和資料匯流排,以及兩組緊密整合的記憶體(TIM),這使SoC能夠擁有一個始終開啟的低功耗32位元CPU,可與高階64位元CPU結合使用,當某些應用需要更高性能時(例如語音啟動智慧型設備),該CPU可以開啟。這種開發配置有助於滿足機器學習和物聯網連接設備日益成長之需求,其中即時載荷已經產生了對邊緣處明顯增強的嵌入式智慧之巨大需求。

RISC-V的開源特性已經為Kendryte、efabless和low RISC等新創公司開闢了SoC設計,但更多主流晶片提供商也在使用該技術。Microsemi(現為Microchip一部分)已經為SiFive生產了一些開發板,而NXP則擁有自己的RISC-V晶片。Andes Technology和Greenwave也開發了基於ISA的多種IC。Faraday Technology已將ISA用於ASIC平台,目標是下一代邊緣人工智慧(AI)和物聯網SoC的設計和批量生產。其彙集了RISC-V內核IP整合和SoC設計驗證,以及全功能參考設計套件,其中包括即時作業系統(RTOS)和周邊設備驅動程式,所有這些都採用55nm制程,適用於電池供電的邊緣設備。這突顯了硬體製造商可以在標準ISA基礎上實現差異化。Faraday Technology在其平台中整合有動態電壓和頻率調節(DVFS)、功率模式切換和快速系統喚醒等功能,也可以安全地整合軟體庫和驅動程式,以確保晶片在實現特定的介面、感測和電源管理功能時能夠無縫工作。

RISC-V ISA可與各種工具共同使用

RISC-V ISA的另一個優勢是它能夠與各種工具一起使用。Microsemi在其FPGA產品中使用了ISA,其中包括Express Logic的ThreadX、華為LiteOS和Micrium µC/OS-II等多種嵌入式作業系統。主機板包括RTG4開發套件和PolarFire評估套件等,其中還包括Microsemi和Olimex的除錯硬體鑰匙(Debug...