5nm

TrendForce估第三季全球晶圓代工產值年增14%

根據TrendForce旗下拓墣產業研究院最新調研結果顯示,由於年底為歐美消費旺季,加上中國十一長假及雙11促銷活動,帶動下游客戶端拉貨動能旺盛,使晶圓代工產能與需求連帶穩定提升,預估第三季全球晶圓代工業者營收將成長14%。

2020年第三季全球前十大晶圓代工業者營收預測排名

台積電(TSMC) 2020年第三季營收年成長預估21%,營收主力為7nm製程,受惠於5G建設持續部署、高效能運算和遠距辦公教學的CPU、GPU等強勁需求,產能維持滿載;而5nm製程在2020年第三季開始計入營收,在全年度台積電5nm營收占比以8%為目標的情況下,預計第三季5nm營收占比將達16%。

三星(Samsung)今年雖然受到旗艦手機S20系列銷售下滑影響,使其調整自家AP的晶圓代工業務量;然而客戶止防晶片斷料的庫存儲備的心態,帶動其他晶圓代工業務成長,推估第三季營收年成長約4%。而格羅方得(GlobalFoundries)在2019年分別出售8吋、12吋晶圓廠,且受車用晶片需求衰退影響,其第三季營收表現不如預期,年減3%。

聯電(UMC)因大尺寸面板DDI、PMIC需求上升,推估8吋晶圓產能吃緊狀況可能持續到2021年,目前透過調漲部分代工價格的策略,將有助於推升其第三季整體營收,年成長可望達23%。中芯國際(SMIC)九成以上收入來自14nm、28nm以上的成熟製程產品,由於2019年的基期較低,預估2020年第三季營收年增率將達16%,然仍須持續關注華為寬限期(2020年9月15日)後,其14nm的接單情況。

高塔半導體(TowerJazz)致力於發展RF-SOI與SiGe,第三季8吋產能利用率估計將維持近70%,而12吋產能也正持續擴增,預估2020年第三季營收年成長約3%。力積電(PSMC)晶圓代工業務持續擴展,DDI、TDDI、CIS、PMIC、功率離散元件(MOSFET、IGBT)等代工需求增加,透過調升代工價格與提高產能利用率,其第三季營收年成長以26%為前十名之最。

世界先進(VIS)因新加坡廠加入營運,帶動晶圓出貨增加;加上大尺寸DDI、PMIC需求大幅成長,在8吋產能滿載之下,預估第三季營收年成長可達21%。華虹半導體(Hua Hong)產品類別中,以長期占六成以上的消費電子最大宗,其中又以中低階手機相關晶片產品為主。然因疫情導致營收下滑,目前則採用降低平均售價並提升產能的營運策略,預估第三季營收年減1%。

受惠於市場CIS與DDI需求大量提升,東部高科(DB HiTek)產能滿載,目前不排除調漲代工價,將拉升其第三季整體營收,年成長率微幅上升2%。拓墣產業研究院指出,整體而言,雖然目前下游客戶端需求上升,仍需隨時關注其在大量拉貨後的庫存水位消化狀況,廠商密切掌握動態,方可快速調整策略布局。

半導體先進製程超限戰 5nm成下一個金雞母

半導體先進製程已經與晶片效能畫上等號,因此,除了品牌與功能之外,對於晶片商來說,採用先進製程也是技術行銷的一大重點,晶片的成功與擴散很大程度上取決於IC製造商能否繼續提供更多的性能和功能。隨著主流CMOS製程達到其理論、實用和經濟極限,降低IC成本不可避免地與不斷成長的技術和晶圓廠製造能力相提並論。台積電已經正式量產的5奈米(nm)製程將成為下一個製程爭奪重點,並為該公司創造更多營收。

2015~2021年主要晶圓廠製程發展進度 資料來源:IC Insights(2/2020)

根據產業研究機構IC Insights最新研究指出,許多IC公司現在正在設計10nm和7nm製程的高階微處理器、應用處理器和其他高級邏輯設備。在半導體製造領域,採用先進製程具有明顯的優勢。在2019年,台積電是唯一使用7奈米製程技術的晶圓代工廠,也成為各家晶片廠商的「名牌」,台積電的先進製程創造大量營收,7奈米製程也出現排隊狀況,一線大廠才能優先取得產能,搶先量產產品,並為廠商拿來作為產品行銷的重點技術。

也由於IC設計廠商排隊採用7奈米製程製造最新設計,推升台積電單片晶圓總收入。台積電2019年每片晶圓收入高於2014年13%,也是全球唯一一家達成此目標的晶圓廠。相較之下,GlobalFoundries、聨電UMC和中芯國際(SMIC)2019年每片晶圓收入,與2014年相較分別下降了2%、14%和19%,這三家廠商的最先進製程約在12/14奈米。

除了代工和邏輯IC製造外,三星、美光、SK Hynix和Kioxia/WD等記憶體供應商都在使用先進製程來製造其DRAM和快閃記憶體(Flash)元件。無論設備類型如何,IC產業都已經發展到只有極少數的公司可以開發前瞻製程技術並製造前瞻IC的地步。日益成長的設計和製造挑戰以及成本已經將積體電路領域門檻變的越來越高。

高通推5G數據機射頻系統 5奈米晶片再受矚目

去年三星及台積電陸續宣布使用極紫外光(EUV)微影技術的5奈米製程備受矚目,台積電也表示將在2020年投入量產。而日前高通推出的Snapdragon X60 5G數據機射頻系統即使用5奈米晶片,再次引發市場對5奈米製程高度的關注。

高通Snapdragon X60 5G數據機射頻系統。

半導體製程從7奈米進展到5奈米,其所使用的EUV技術不只提升晶片的性能、減少功耗及縮小面積,同時透過減少光罩層數協助設計者簡化設計流程,為產業提供更高的經濟效益。

5奈米製程在通訊的應用上,有助於5G技術的普及。高通推出的Snapdragon X60採用5奈米5G基頻晶片,能加快行動裝置平均的5G連線速度,並且加強電信產品的效能與容量,此項5G數據機至天線解決方案,可達到7.5 Gbps下載以及3 Gbps上傳的速度。

在技術層面,X60的主要優勢在於,作為業界第一個支援頻譜聚合的5G數據機射頻系統,涵蓋主要的5G頻段與組合,其中包括使用分頻雙工(FDD)與分時多工(TDD)的毫米波與sub-6頻段,能夠運用片段頻譜資產提升5G效能。此外,X60內建的5G FDD-TDD sub-6載波聚合解決方案,除了支援5G FDD-FDD和TDD-TDD並搭配動態頻譜分享(DSS),讓電信營運商擁有更多部署選擇,包括將LTE頻譜重新規劃供5G使用。

X60同時搭載高通第三代的QTM535毫米波天線模組,可望用於設計更輕薄的智慧型手機。高通預期,2020年第一季Snapdragon X60與QTM535將開始送樣,搭載這兩款方案的智慧型手機,則可望在2021年初上市。

滿足先進製程 ASML持續強化EUV微影系統

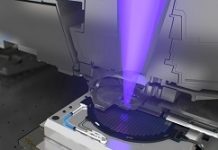

AI、5G應用推動晶片微縮化,要實現5nm、3nm等先進製程,意味著需要更新穎的技術支援以進行加工製造,半導體設備商遂陸續推出新一代方案。AI、5G應用推動晶片微縮化,要實現5nm、3nm等先進製程,意味著需要更新穎的技術支援以進行加工製造,為此,艾司摩爾(ASML)持續強化極紫外光(EUV)微影系統效能。

艾司摩爾(ASML)資深市場策略總監Boudewijn Sluijk表示,VR/AR、自動駕駛、5G、大數據及AI等,持續推動半導體產業發展,為滿足各式應用、資料傳輸,以及演算法需求,晶片效能不斷提高的同時,還須降低成本,而極紫外光(EUV)在先進製程中便扮演關鍵的角色。

ASML資深市場策略總監Boudewijn Sluijk。

Sluijk進一步指出,過往採用ArFi LE4 Patterning或是ArFi SAQP進行曝光的話,要實現7nm、5nm,須經過許多步驟。例如用ArFi LE4 Patterning需要4個光罩、4次曝光,用ArFi SAQP需要6個光罩、9次曝光,而EUV只需一個光罩、1次曝光(圖2)。相較之下,採用EUV技術不但可有效簡化製程,加快產品設計時程,也因為曝光次數明顯減少,因而可有效降低成本,滿足晶片設計高效能、低成本的需求,因此,市場對於EUV的需求有增無減。

據悉,ASML的EUV系統現在可用於7nm生產,滿足客戶對可用性、產量和大量生產的需求。到了2019第2季季末,目前半導體領域已經有51個EUV系統(包含NXE:33xx、NXE:3400B),而該公司在2019年的銷售目標為30台EUV,目前已出貨11台,而在第2季再度接獲10台EUV極紫外光系統的訂單,顯示市場對於EUV設備的需求相當強勁。因此,ASML的出貨計畫將著重於2019年下半年和第4季,而2019年的整體營收目標維持不變。

然而,隨著晶圓產能不斷增加,ASML也持續推出生產力更高的EUV設備。Sluijk透露,目前EUV系統在晶圓廠客戶端每天生產的晶圓數量超過1,000片,為此,ASML持續強化EUV微影系統「NXE:3400C」的量產效能,不僅在ASML廠內展示每小時曝光超過170片晶圓的實力,在客戶端實際生產記憶體晶片的製造條件下,也成功達到每天曝光超過2,000片晶圓的成果,甚至達到2,200片的紀錄。另外,ASML也計畫在2020上半年推出生產力更高的設備,將NXE:3400C的生產率提升至> 185 wph。

同時,除了提升設備生產量之外,因應未來先進節點,ASML也計畫推出全新EUV設備,名稱為EXE,不僅擁有新穎的光學設計和明顯更快的平台,且數值孔徑更高,為0.55(High-NA),進一步將EUV平台延伸至3nm節點以下,擴展EUV在未來先進節點中的價值。

Sluijk說明,此一產品將使幾何式晶片微縮(Geometric Chip Scaling)大幅躍進,其所提供的分辨率和微影疊對(Overlay)能力比現有的NXE:3400高上70%。EXE平台旨在實現多種未來節點,首先從3奈米開始,接著是密度相近的記憶體節點。另外,EXE平台有著新穎的光學設計,並具備更高的生產力和更高的對比度,以及更高的生產量,每個小時> 185 wph,且Reticle stage比NXE:3400快上4倍;Wafer stage比NXE:3400快上2倍。

Sluijk指出,該公司的EUV平台擴展了客戶的邏輯晶片和DRAM的產品路線圖,透過提供更好的分辨率、更先進的性能,以及逐年降低的成本,EUV產品將會在未來十年到達一個經濟實惠的規模。