3D封裝

因應先進封裝需求 EV GROUP成立異質整合技術中心

晶圓接合暨微影技術設備廠商EV Group(EVG)宣布,該公司的異質整合(HI)技術中心已建立完成,未來將協助客戶透過EVG的製程解決方案與專業技術,打造全新且更強勁的產品與應用,包含高效能運算與資料中心、物聯網(IoT)、自駕車、醫療與穿戴裝置、矽光子及先進感測器所需的解決方案與應用。

異質整合技術中心結合了EVG的晶圓接合、晶圓薄化處理、微影製程產品與專業技術,以及EVG奧地利總部最先進無塵室中的試產生產線設備與服務,同時獲得EVG全球各製程技術團隊的支援。透過HI技術中心,EVG將協助客戶加速技術開發、將風險降至最低,並透過異質整合和先進封裝開發出與市場區隔的技術與產品,同時確保客戶針對即將推出的產品採用最高等級的智財權保護標準。

EV Group技術開發和IP總監Markus Wimplinger表示,異質整合推動全新封裝架構的發展,並且需要新的製造技術來支援更強大的系統與設計彈性,以及提高系統的效能和降低設計成本。EVG全新的HI技術中心為我們微電子供應鏈的客戶與合作夥伴,提供一個開放取用的創新育成中心來協同合作,同時結合我們的解決方案與製程技術資源,縮短異質整合打造的創新裝置與應用所需的開發週期與產品上市時程。

EVG在異質整合領域具有廣泛的技術背景,並在過去20多年來針對此關鍵技術趨勢提供各種解決方案,其中包括永久性晶圓接合,包含3D封裝與金屬接合的直接融合與混合接合、III-V化合物半導體與矽的整合使用或不使用聚集載體的方式來完成晶片到晶圓接合,以及高密度的3D封裝;暫時性接合與剝離,包含機械式、滑動分離/ 上掀剝離與UV雷射輔助的剝離方式;晶圓薄化傳送處理技術;創新微影技術,包含曝光機、塗佈機與顯影機,以及無光罩曝光/ 數位微影。

圖 透過聚集載體晶圓實現晶片對晶圓混合接合的整合晶片。

在永久性接合領域,EVG早在20多年前就率先推出具專利的SmartView晶圓對晶圓對準系統,並且多年來持續強化此技術以支援突破性的技術精進,例如背照式CMOS影像感測器(BSI-CIS),以及近期針對混合接合展示了第一個100奈米以內晶圓對晶圓重疊對準度,此技術催生出如3D BSI-CIS與記憶體晶片和邏輯電路的堆疊(Memory-on-logic)等裝置。EVG也早在2001年便針對超薄晶圓開發出第一個暫時性的接合系統,這套系統對於3D/ 堆疊式晶片的封裝不可或缺,同時也為超薄與堆疊扇出型封裝的低溫雷射剝離技術帶來革命性的進展。

在微影製程領域,EVG憑藉十多年前推出的第一套供晶圓級光學量產用的UV壓印成型解決方案,鞏固了備受各界肯定的技術領先地位,自此之後帶領業界擴大奈米壓印微影(NIL)的量產。EVG持續突破用於先進封裝的光罩對準曝光機在速度與精準度上的界線,近期更推出全球首個具高度擴充性的無光罩曝光技術,解決後段微影製程量產日益凸顯的需求。

全新3D X-ray方案亮相 蔡司讓3D封裝量測變簡單

3D封裝為目前半導體產業熱門議題,然而,3D封裝技術的出現,雖說可明顯提升晶片效能,卻也為量測、檢驗帶來新的挑戰。為此,蔡司(ZEISS)近日宣布推出微米解析度3D非破壞性的成像解決方案「Xradia 620 Versa RepScan」,與現有的物理橫切面、2D X-ray及microCT等量測方式相比,能提供更精準的量測結果,以縮短先進封裝的開發與良率學習週期,加速先進IC封裝的上市時程。

蔡司半導體製造技術(SMT)資深行銷總監Raleigh Estrada表示,行動與高效裝置對於體積微縮以及傳輸效能的需求不斷提高,使得晶片製造走向高密度、多架構的創新設計,而這些技術也帶動封裝技術邁入立體化;不過,這些技術的製程寬容度(Process Margin)通常較低或較難被控制,也因此,製程量測技術也成為是否能推出新穎且先進技術的關鍵。

蔡司半導體製造技術資深行銷總監Raleigh Estrada。

Estrada說明,現今先進封裝中因目標物太小,已無法用2D X-ray與microCT這類非破壞性的方法來觀測。此外,物理橫切面除了無法提供3D立體資料之外,還屬於破壞性量測,較為耗時,通常也只能處理少量樣本,就統計層面來說,改進製程控制的成效有限,也因此,需要更先進、精細的檢測設備。

蔡司半導體製造技術業務發展總監Thomas Gregorich則指出,半導體封裝技術正出現明顯的改變。過去50年來,晶圓廠已將最小的電路板尺寸從微米縮小至奈米,這個轉變部分是透過精密的檢驗與量測系統所達成。不過,現今的技術幾乎已達Dennard微縮定律與摩爾定律的極限,使得產品效能提升的關鍵從晶片轉至IC封裝。

蔡司半導體製造技術業務發展總監Thomas Gregorich。

Gregorich進一步解釋,而封裝技術的改變,也連帶影響了封裝量測技術。舉例來說,未來的記憶體與「小晶片(Chiplet)」技術預計將使封裝互連間距降至20微米或更小,使得互連密度達到每平方公厘2,500~10,000 I/O。這類封裝會需要後段製程(BEOL)般的互連密度與晶圓廠級的組裝良率。但是,近50年來IC封裝產業高度倚賴物理橫切面來檢視、量測並定義深埋在內的結構,此方式對這些先進封裝來說並不足夠,因此需要新的檢驗與量測的技術。

為此,蔡司推出全新3D非破壞性的成像解決方案620 Versa RepScan,該產品內含經驗證過的Versa 3D XRM功能,能用次微米解析度以非破壞性方法成像並量測深埋在結構內的晶片,並運用重建的3D資料集擷取出關鍵的3D資訊。

除了能執行各種線性及體積量測之外,該產品亦能對矽穿孔與微凸塊、銲料體積與形狀、接合線厚度、晶粒翹曲(Warpage)、3D空隙分析與其他的量測進行各方面的分析,且僅需準備最少的樣本。半自動化的工作流程提供可重複的量測,確保不會因橫切面誤差導致成像遺失,並將手動操作導致的量測變異性降至最低。

2023年2.5D/3D封裝產業規模達57.49億美元

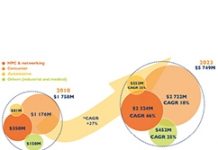

根據產業研究機構Yole Développement(Yole)的研究指出,像HBM和CIS這樣的硬體創造了TSV的大部分收入。2023年整體堆疊技術市場將超過57億美元,年複合成長率(CAGR)為27%,2.5D/3D TSV和晶圓級封裝技術中,消費市場是最大的貢獻者,市場比重超過65%。高效能運算(HPC)是立體構裝技術的真正驅動力,並且將呈現高度成長到2023年,市場占有率從2018年的20%增加到2023年的40%。汽車、醫療和工業等領域的應用將是主力。

而消費性、高效能運算與網路(HPC & Network)、汽車、工業與醫療則是最主要的應用領域,其中消費性應用還是占據最大的規模,市場將從2018年的11億7600萬美元,成長至27億2200萬美元,CAGR 18%,而高效能運算則將從3億5000萬美元成長至23億3200萬美元,CAGR高達46%,是成長率最高的應用,車用市場8100萬美元成長至2億5200萬美元,CAGR 25%,工業與醫療應用合計將從2018年的1億5000萬美元,成長至2023年的4億5200萬美元,CAGR也是25%。