嵌入式系統

萊迪思推出SWA方案 簡化嵌入式系統設計

萊迪思半導體公司(Lattice)為低功耗、可程式化設計元件的供應商,日前宣布推出單線聚合(SWA)IP解決方案,在工業、消費和運算等應用中縮小系統整體尺寸並降低BOM成本。該解決方案為開發人員提供了快速、簡便、創新的方式,透過使用低功耗、小尺寸的萊迪思FPGA來大幅減少嵌入式設計中電路板之間和元件之間連接器的數量,從而提升穩定性、縮小系統整體尺寸並降低成本。

在電子系統中連接各電路板和模組的連接器不僅價格高昂,還會占用設備有限的寶貴空間,且長期使用下其效能也會大打折扣,影響系統的穩定性。在空間有限的電路板上連接多個連接器,其之間的訊號傳輸也會帶來設計方面的挑戰,延長產品的整體上市時間。

萊迪思市場經理Hussein Osman表示,開發人員希望找到創新方法來簡化和加速嵌入式系統的開發,並盡可能降低BOM成本。全新SWA解決方案能透過減少系統中連接器的數量滿足以上三個需求。該解決方案非常適合FPGA開發新手和專家。它的預配置位元流(bitstream)可幫助FPGA設計新手快速配置SWA應用,毋需HDL程式設計經驗;同時該解決方案支援擴展參數(expanded parameterization),因此FPGA專家可以輕鬆地將萊迪思SWA位元流與自己寫的HDL程式碼結合使用。

機器學習邁向物聯網終端 神經網路加值MCU邊緣智慧

基於各方考量,如延遲、耗電量、成本、網路頻寬、可靠性、隱私與安全等,機器學習(ML)演算法正朝物聯網(IoT)終端的應用發展。因此,廠商對於開發類神經網路(NN)解決方案,並將它們部署在微控制器系統這類低功率終端裝置的興趣與日俱增。為促成這類部署,Arm提出CMSIS-NN。這是一種經優化的軟體核心開放原始碼函式庫,可極大化其產品Cortex-M核心的NN效能,而且只需使用最小的經常性記憶體。本文進一步提出NN架構探索的方法,以CIFAR-10數據集的影像檔分類為例,開發適用在條件受限的裝置模型。

MCU降低運算延遲 演算法提升NN準確性

聯網裝置或物聯網過去幾年內快速擴展,到2035年,各區市場的聯網裝置總數預測將達到1兆個。這些物聯網終端裝置通常包含數個可以搜集數據的感測器,包括音訊、視訊、溫度、溼度、GPS位置與加速度等。通常大多數感測器搜集到的數據由雲端的分析工具進行處理,以便運作各式的應用,如工業監控、家庭自動化與健康照護。不過隨著物聯網節點數目增加,對網路的頻寬帶來相當的負擔,同時也增加物聯網應用的延遲性。此外,對雲端的依賴也造成在網路連線不穩定或有限的區域,部署物聯網應用相當具有挑戰性。這個問題的解決方案之一是終端運算,這種運算在數據的源頭、也就是物聯網的終端節點進行,因此可以降低延遲,並節省數據通訊消耗的能源。

類神經網路架構的解決方案,針對如影像分類、語音辨識與自然語言處理等複雜的機器學習應用,已經展現出與人類一樣水準的準確性。有鑑於運算的複雜性與資源的需求,NN的執行絕大多數都局限於高效能的伺服器CPU,或專用硬體(如GPU或加速器)的雲端運算,但會讓物聯網應用增加延遲。而如果在數據的源頭(通常是微控制器)立即進行分類,可以降低整體的延遲以及物聯網終端與雲端間數據通訊的能源消耗。不過在微控制器部署NN,有下列挑戰:

・有限的記憶體使用量:微控制器系統通常只有10幾到100多KB的可用記憶體。整個類神經網路模型,包括輸入/輸出、權重與啟動,都必須在如此小的記憶體上限內運行。

・有限的運算資源:許多分類任務都有不斷線啟動與即時的要求,這會限制每個類神經網路推論的總運算次數。

這些挑戰可以從裝置與演算法的角度加以應對。一方面在執行類神經網路工作負載時,可以靠優化低階運算核心來達成更佳的效能與更小的記憶體使用量,並藉此提升這些微控制器的機器學習能力,協助微控制器處理更大型與更複雜的NN。另一方面,類神經網路可以靠NN架構的探索設計與優化目標硬體平台。此方法可以在固定的記憶體與運算配置上限內,提升NN的品質,也就是準確性。

下一個段落中,筆者提出CMSIS-NN的概念。CMSIS-NN是大量的高效類神經網路核心,開發目的是讓鎖定智慧物聯網終端裝置的Arm Cortex-M處理器核心上的類神經網路,極大化效能並極小化記憶體的使用量。架構在CMSIS-NN核心基礎上的類神經網路推論,可以達成4.6倍的Runtime/數據傳輸量提升,以及4.9倍的能源效率提升。文章的第三個段落則以使用CIFAR-10數據集的影像分類應用為例,針對微控制器記憶體/運算限制,提出搜尋類神經網路架構的技巧。

CMSIS-NN提升核心Runtime/傳輸量

CMSIS-NN類神經網路核心的總覽(圖1),核心編碼包含兩個部分:NNFunctions與NNSupportFunction。NNFunctions包含實作常見的類神經網路層類型的函數,如卷積、深度可分離卷積結構、全連接(也就是內積)、池化與啟動。這些函數可以讓應用程式碼使用,以實作類神經網路的推論應用。核心API則刻意保持簡單,以便針對TensorFlow、Caffe或PyTorch等所有機器學習框架輕鬆重新鎖定。NNSupportFunctions包含公用的程式函數,例如NNFunctions使用的數據轉換與激勵函數表。應用程式碼也可使用這些函數來建構更複雜的NN模組,如長短期記憶(LSTM)或閘控再流裝置(GRU)單元。

圖1 CMSIS-NN類神經網路核心總覽

對於某些核心,如全連接與卷積的核心,本文會實作不同版本的核心函數。提供一個針對所有網路層參數不必改變就可以通用的基本版本。同時也實作包括進一步優化技巧的其它版本,它們可能具有變形輸入,或是對網路層參數有某些限制。

固定點量化

研究顯示,即便是低精密度定點表示法,NN的運作依然良好。固定點量化可以協助避免進行昂貴的浮點運算,並降低儲存權重與啟動的記憶體使用量,這對資源受限的平台極為關鍵。儘管不同網路或網路層的精密度需求可能不同,CPU很難運行帶有不同位元寬度的資料類型,因此筆者的團隊開發了同時支援8位元與16位元數據的核心。

核心採用跟CMSIS-DSP裡使用的資料類型格式相同,也就是把q7_t當作int8、把q15_t當作int16,並把q31_t當作int32。執行量化時,假定固定點格式具有兩次方的定標。量化格式以Qm.n代表,而代表值是A×2-n,其中的A是整數值而n是Qm.n的一部分,代表該數字針對分數部分使用的位元數,也就是顯示數基點的所在地。跳過偏差用的定標因素,並把它以參數輸出至核心;因為是二次方定標的關係,定標的實作按位元移位操作。

在NN的運算期間,代表不同數據,也就是輸入、權重、偏差與輸出的固定點可能不同。bias_shift與out_shift這兩個輸入參數,則為用來替運算調整不同數據的定標。

下列方程式可以用來估算移動值:

其中的ninput、nweight、nbias 與 noutput,分別是輸入、權重、偏差與輸出中的分數的位元數。

軟體核心優化

這個段落突顯了在CMSIS-NN裡已進行的優化工作,以提升效能並降低記憶體的使用量。

1.矩陣乘法:矩陣乘法是類神經網路中最重要的運算核心。這個工作的實作,是使用CMSIS-DSP內的mat_mult核心。如圖2所示,矩陣乘法核心是以2×2核心實作,與CMSIS的實作類似。因此可以允許部分數據再次使用,也可以節省載入指令的總筆數。累積是使用q31_t資料類型完成,而兩個運算單元都屬於q15_t資料類型。筆者使用相對應的偏差值,讓累加器初始化。運算的執行則是使用專用的SIMD MAC指令_SMLAD。

圖2 具有2×2核心的矩陣乘法的內迴圈。每個迴圈運算兩行與兩列點乘積結果,也就是產生四個輸出

2.卷積:卷積網路層藉由在輸入特徵映射中運算過濾器權重與小型接受區域之間的點乘積,擷取新的特徵映射。通常來說,CPU架構的卷積實作可以解構成輸入紀錄、擴展(也就是im2col與Image-to-column)以及矩陣乘法操作。im2col是把類影像的輸入轉化成「行」,而「行」則代表每個卷積過濾器需要的數據。圖3即為im2col的一個範例。

圖3 具3×3核心、填充1與步數2的im2col的2D影像範例

im2col主要的挑戰之一是記憶體使用量的增加,因為輸入影像中的畫素在im2col輸出矩陣中重複。為了紓解記憶體使用量問題、同時維持im2col的效能優點,卷積核心實作了部分的im2col。核心一次只會擴展兩行,這已經足夠從矩陣乘法核心取得大幅的效能提升,同時把記憶體負擔維持在最小。影像數據格式也會影響卷積的效能,特別是im2col的效率。兩種最常見的影像數據格式是頻道為第一的CHW(頻道-高度-寬度),與頻道為最後的HWC(高度-寬度-頻道)。維度的順序則與數據步數的順序一樣。在HWC格式中,頻道的數據以步數1儲存,沿著橫向寬度的數據則是以頻道數的步數儲存;沿著縱向高度的數據,則以(頻道數×影像寬度)步數儲存。

只要權重與影像的維度順序一樣,數據的布局對於矩陣乘法的運作就沒有影響,im2col只會與寬度及高度的維度一起運作。HWC式樣的布局可以促成高效率的數據移動,因為每個畫素的數據(也就是同樣的x與y位置)是連續地儲存,並且可以用SIMD指令有效率地進行複製。為了驗證這一點,筆者實作CHW與HWC版本,並比較它們在Arm Cortex-M7的Runtime。圖4顯示了實作結果,把HWC輸入固定為16×16×16,並很快輸出頻道數目。當輸出頻道值為零時,代表軟體只執行im2col,並沒有進行任何矩陣乘法的運作。與CHW布局相比,HWC擁有較短的im2col Runtime,但矩陣乘法效能卻相同。因此,本文用HWC數據布局來實作卷積核心。

圖4 CHW與HWC數據布局卷積執行時間的比較。兩種布局都有同樣的矩陣乘法runtime,但HWC的im2col runtime比較短

CMSIS-NN結果

測試卷積神經網路(CNN)的CMSIS-NN核心,CNN則利用CIFAR-10數據集進行訓練。數據集包含6萬個32×32的彩色影像,並分為十個輸出類別。網路拓撲是基於Caffe內提供的內建範例,具有三個卷積網路層與一個完全連結的網路層。所有網路層的權重與激勵數據都量化成q7_t格式。Runtime則是用具有一顆時脈216MHz的Arm Cortex-M7核心的意法半導體(ST)NUCLEO-F746ZG Mbed開發板進行測量。

整個影像分類中的每個影像,大約花費99.1微秒(相當於每秒10.1張影像)。CPU在這個網路運行的運算吞吐量,大約是每秒249百萬運算(MOps)。預先量化的網路針對CIFAR-10測試集達成80.3%的準確率。用Arm Cortex-M7核心運行的8位元量化網路,則達成79.9%的準確率。使用CMSIS-NN核心的最大記憶體使用量約為133KB,此時用部分的im2col來實作卷積以節省記憶體。接下來則進行矩陣乘法。少了部分im2col的記憶體使用量,大約為332 KB,此時神經網路無法在開發板上使用。為了量化CMSIS-NN核心對既有解決方案帶來的優點,選擇使用一個1D卷積函數(來自CMSIS-DSP的arm_conv)、類Caffe池化與ReLU,實作一個基準線版本。

針對CNN應用,表1總結基準線函數與CMSIS-NN核心的比較結果。與基準線函數相比,CMSIS-NN核心的Runtime與吞吐量分別提升2.6倍與5.4倍,節能方面的提升也與吞吐量的提升相近。

硬體條件限制NN模型

這個段落裡,比較使用影像分類應用為範例,說明為部署應用的硬體平台,也就是微控制器選擇正確類神經網路架構的重要性。為此,需要先瞭解微控制器的硬體限制。微控制器通常包含處理器核心、一個當成主記憶體的靜態隨機存取記憶體(SRAM),以及用來儲存編碼與數據的嵌入式快閃記憶體。表2顯示具有Arm Cortex-M核心的一些市售微處理器開發板,它們擁有不同的運算與記憶體容量。

微處理器系統中的記憶體數量,會限制系統可運行的類神經網路模型的大小。除了記憶體限制,類神經網路的龐大運算需求也會為在微控制器上運行NN,帶來另一個關鍵限制:為了維持低耗電,通常都以低時脈運行。因此,必須選擇對的NN架構,來配合部署NN模型的硬體在記憶體與運算上的限制。為了評估在不同硬體限制條件下神經網路的準確性,筆者選擇三個不同尺寸的系統配置,並導出每個配置需要的類神經網路需求(表3)。假定每秒標稱可進行10個影像的分類推論(也就是每秒10幀),以便導出神經網路的需求。

影像分類用神經網路架構

1.卷積神經網路:CNN是電腦視覺應用最受歡迎的類神經網路架構。CNN包含多個依規格化散布的卷積網路層、池化與非線性激勵網路層。卷積網路層將輸入的影像解構到不同的特徵映射,從初始網路層中如邊緣、線條與曲線等低階特徵,到後面網路層的高階/抽象特徵。當代最頂尖的CNN包含100多個到1,000多個這種卷積網路層,而最後擷取的特徵則由完全連結的分類網路層分類至輸出類別。卷積運作是CNN最關鍵的運作,並且非常耗時,有超過九成的時間都花在卷積網路層上。

2.近期的高效NN架構:為了降低CNN的運算複雜性,有人提議用深度可分離卷積網路層當成標準卷積運作的高效率替代品。也有人提出利用2-D深度卷積接著1-D逐點卷積,取代標準的3-D卷積,並提出名為MobileNets的高效率NN類別。ShuffleNets利用混合 頻道上的深度卷積以及群組軟體1×1的卷積,來提升緊湊模型的準確性。MobileNets-V2藉由增加捷徑連接進一步提升效率,並協助深度網路的收斂。整體來說,已經有許多高效率的神經網路架構提案,可以用來開發符合特定硬體預算的NN模型。

硬體條件受限的NN模型的搜尋

筆者使用具捷徑連接的MobileNet架構,它類似讓硬體條件受限的類神經模型,進行搜尋的ResNet模型裡的架構。網路層的數量、每層網路層的特徵數量、卷積過濾器的維度與步數,被當成這次搜尋的超參數。訓練這些超參數的所有組合相當耗時,並且不太實際。因此需要反覆執行超參數的竭盡式搜尋、計算模型的記憶體/運算需求,並且只訓練能配合硬體預算限制的模型。隨後從之前的集用場選擇超參數,以縮小搜尋空間,並繼續下一更新的模型搜尋。圖5為超參數搜尋的範例,這個範例顯示準確性、運算的數量,以及每個模型的參數。

圖5 利用CIFAR-10數據集進行影像分類的類神經網路超參數搜尋vs以泡泡尺寸顯示的運算及參數數量

經過幾個更新後,表4顯示於硬體條件限制內具有最高準確性的模型。請留意,由於這並不是對所有超參數進行的極盡式搜尋,因此在搜尋期間可能會漏掉一些符合硬體條件限制、且準確度極高的類神經網路模型。結果顯示這些模型擴大規模沒有問題,且針對不同的硬體預算,準確性在不同層級出現飽合。例如,針對200KB與每秒20百萬次運算的記憶體/運算預算,模型的準確性大約在85%左右飽合,並且受到硬體的運算能力限制。瞭解類神經網路的準確性是否受運算或記憶體資源限制,對於硬體平台選擇的各種利弊得失,可提供關鍵的洞察。

強化神經網路效能

機器學習演算法已證實可以實現一些人類能力等級的效能,所執行的複雜認知任務。在全新高效類神經網路架構與優化的NN軟體協助下,這些演算法正慢慢地朝物聯網的終端移動,以便類神經網路在這些終端裝置高效運作。在微控制器裝置常見的記憶體/運算限制下,提出執行NN模型搜尋的技巧,並使用影像分類為例,進一步提出優化CMSIS-NN內的NN核心的方法,以便在最小的記憶體使用量下,極大化Cortex-M核心的神經網路效能。

(本文作者Naveen Suda為Arm主任工程師;Danny Loh為Arm機器學習總監)

意法揭2020十大科技新趨勢

2020年CES展已在上個月圓滿落幕,消費電子展不僅展現大量的創新概念和原型設計,亦是一個可以探索創新動力,以及引領未來科技的發展方向。意法半導體(ST)表示,2020是一個新十年的開始,對於未來十年改變人類生活的產品來說,2020年將是影響深遠的一年,因此分享未來十大新趨勢。

首先為現實世界中的預測性維護應用,過去十年見證預測性維護興起。因為機器學習的出現,預測性維護能夠預測故障並建議更好的維護計畫。不過,2020年對於預測性維護應該是具有象徵意義的一年,因為開發預測性維護解決方案將變得越來越容易。例如,工程師可以買到開發板,幾分鐘後就可以開始編寫配套應用,而無需擔心雲端安全問題、伺服器農場或運算傳輸量。關於預測性維護,製造業者不再只是考慮,而是在積極地實現。

至於邊緣機器學習,過去十年,機器學習需要大型的伺服器、複雜的模型,還有罕見的專業團隊,其需要投入大量的時間和資源。如今,機器學習可以放入動作感測器中,而且該公司將會在邊緣裝置中看到更多的智慧功能。邊緣運算永遠不會取代雲端運算,但可以快速完善雲端運算的功能。透過在感測器內創建決策系統,工程師可以優化資源,節省大量能源和時間。

而談到數據科學,缺乏數據和缺少數據科學家是阻止機器學習應用的主要障礙之一。建立神經網路需要乾淨、準確和巨量資料,這意味著始機器學習普及的前提是需要大量可自由使用的資料。然而,意法半導體的合作廠商,如Cartesiam,正進而從另一個角度解決此問題,使用一種能夠在同一嵌入式系統上執行訓練和推理運算的系統來代替資料科學家。

隨著Sub-G網路的普及以及5G到來,嵌入式裝置連線互聯網變得越來越容易。人們將會看到更多的基礎建設,以及更好用、更便宜的聯網方案。現在開發這些解決方案變得更加實際,而且不需花費太多成本。即使是新創公司也計畫使用LoRa、Sigfox或其他的Sub-G網路。因此2020年意法半導體推出STM32WL以因應此一趨勢。

至於資料安全要求將更加嚴格,過去曾有評論家表示IoT為「威脅之網」(Internet of Threats)。但在走完一段長遠路程後,企業更加明白保護嵌入式系統、資料資訊及更新機制的重要性。隨著消費者提出更嚴格的網路攻擊防護需求,意法半導體預計企業將會更加地保護產品的資料安全。幾年前,資料外洩只是一種幾乎無間接負面影響的教育學習,當今,此為一場公關噩夢,可能危害公司利益,甚至危及生命安全,而STM32Trust正是ST提供合作夥伴保護嵌入式系統的方法之一。

另一方面,區塊鏈是過去十年出現之具有重大意義的熱門技術之一。不過,企業現在開始意識到,這些系統的用途遠不止於貨幣。透過IOTA和X-CUBE-IOTA1等專案,ST看到整個科技界都在利用分散式帳本技術來促進機器間的通訊,尤其是IoT節點間的通訊。目前該專案本身進展順利,2020年資訊傳播方式可能會發生變化。

在很長的一段時間裡,嵌入式系統是有幾個按鈕的黑盒子,如今,變成征服新產業和新應用的人機互動式系統。這也導致產品的成功對易用性的依賴程度越來越高,開發人員往往需要在圖形化使用者介面上花費很多時間。意法半導體TouchGFX等解決方案的出現讓使用者介面設計相較從前要簡單很多,同時最新的優化設計讓低功耗微控制器(MCU)也能支援60 FPS的動畫,以及多種顏色和細節。

電動汽車的售價越來越便宜,某方面歸功於ST研發的SiC元件。然而,崛起於2019年的更高效、更實用的充電器市場,2020年應會全面爆發。假設電動汽車充電器無處不在,城市街道到處都是充電樁,且家裡安裝也不用花太多的錢,電動汽車續航問題將會成為歷史。正如Enel X於2020年CES中所展示的應用,ST最新IGBT產品有助於創造出更高效的充電系統。

此外,意法半導體與重點大學合作,在未來工程師教育方式上發揮作用。如為了讓學生更快速地掌握控制系統知識,加州大學洛杉磯分校(UCLA)的教授Kaiser示範一個價格適中,而且每個學生都能買得起的旋轉倒立擺實驗平台。ST亦展示如何用透過無人機套件幫助學生瞭解嵌入式系統。隨著教育工作者為未來十年的熱點應用培養人才, 2020年將繼續上演大規模的教育學術創新。

回顧過去十年,嵌入式系統真正觸及人們的生活。從監測心率的智慧手錶,到追蹤運動量的健身手環,再到看護銀髮族的跌倒偵測器,嵌入式技術為人們帶來實質益處。2020年應該會讓此一趨勢崛起,未來十年可能提升生活品質。嵌入式電子產品正在從小工具變為對人們生活有深遠影響的智慧產品,而且在機器學習的協助下,人們可以獲得有關如何改善健康、減輕壓力、安全駕駛,以及如何用心交流的資訊和建議。2020年將提煉我們從過去十年學到的知識經驗,並開始應用,使其更有意義。

聯發科選用Mentor Nucleus RTOS開發蜂巢式數據機技術

西門子(Siemens)旗下業務Mentor宣布聯發科技(MediaTek)已選用NucleusRTOS平台的ReadyStart版本來開發其下一代數據機晶片組。Nucleus RTOS能獲得聯發科技青睞,因為其成熟、穩定、可擴展和最高品質的商用即時作業系統之一。Nucleus ReadyStart RTOS平台把整合的軟體IP、工具和服務帶到一個單一的「即用型」解決方案中,可加速嵌入式系統的開發。

聯發科技無線通訊事業部總經理李宗霖表示,身為無線通訊和數位多媒體的創新SoC市場領導者,聯發科技積極投資創新與研發下一代技術。Nucleus ReadyStart RTOS平台已是該公司數據機開發的重要組成,為通過市場驗證的可擴展解決方案,具有可用原始碼、較小佔用空間、即時效能以及優異技術支援等優點,是該公司蜂巢式數據機晶片組的理想選擇。

聯發科技需要硬親和性(Hard Affinity)的對稱多重處理器(SMP)用來最佳化於關鍵效能任務核心上的快取效能,以及軟親和性(Soft Affinity)用來最大化單核心的快取效益,並以(BCDBound Computational Domain)來隔離關鍵的單核心任務。Nucleus RTOS現已部署於全球超過30億台裝置中,聯發科技將使用Nucleus RTOS開發其一系列的數據機晶片組。

西門子旗下業務Mentor的嵌入式平台技術總經理Scot Morrison表示,Mentor是嵌入式產業中擁有廣泛嵌入式軟體解決方案與服務的供應商,聯發科技選用Nucleus ReadyStart RTOS平台來開發其下一代蜂巢式據機晶片組,對該公司來說至關重要。聯發科技持續投資於5G等新興技術,而該公司嵌入式解決方案將有助於聯發科技推動其智慧技術和創新的使命,讓該公司感到十分自豪。

Nucleus ReadyStart RTOS平台可提供單一發行版本,以加速嵌入式系統開發,並支援系統和應用程式工作流程,擁有廣泛的硬體支援(MCU、DSP、FPGA、MPU),並包含完備的中介軟體組合,其工具鏈已與Mentor屢獲殊榮的Sourcery軟體工具整合在一起,適用於所有階段的開發工作。完備的嵌入式解決方案可協助聯發科技輕鬆、快速且高效建構從簡單到複雜的各種系統。

英飛凌聯手各界強化聯網及ICT安全防護機制

聯網機器與ICT系統尤其需要強大安全防護機制,並且在其長期使用週期中維持高度安全性。面對長期的承受攻擊意味著必須透過更新機制維持最先進的防護狀態。歐洲ALESSIO聯合專案的目標旨在研究和評估此種可更新的安全機制,專案成員於自動化產業的主要貿易展SPS的VDMA論壇中展示其研究結果。

在英飛凌(Infineon)領導下,佛朗霍夫應用及整合安全研究院(AISEC)、Giesecke+Devrient Mobile Security、西門子(Siemens)、慕尼黑工業大學(TUM)及WIBU-SYSTEMS等公司,自2016年以來持續針對聯網運算應用及嵌入式系統,開發晶片式解決方案與原型。ALESSIO獲得德國聯邦教育與研究部(BMBF)約390萬歐元的資助,並計畫於2019年12月31日結束。

每個新聯網裝置都是潛在的網路攻擊閘道。敏感的公司資料與資訊可能會被擷取並遭到惡意使用,以進一步攻擊。因此裝置上任何攸關安全的重要資訊,都必須倚賴軟硬體的雙重防護,才能獲得可靠的保障。雖然軟體仍可透過後續修改,硬體或安全晶片一旦整合,就能受到防止被遠端操控的保護。安全晶片可比擬為保護嚴密的區域,在其中,資料及安全相關資訊會與軟體分開存放。儘管如此,安全區域本身仍必須有更新的方法,因為攻擊手段會隨著時間日新月異。

ALESSIO專案成員展示兩種不同技術方法實現可更新的安全解決方案,包括使用具有可更新軟體的晶片式安全元件,以及實作於稱為FPGA可程式邏輯裝置的可更新安全元件,其中的硬體元件可在運作期間安全更新。上述兩種方法皆可長期有效地管理並確保ICT網路與安全相關資料的安全。

具效能/安全/成本優勢 RISC-V躋身晶片製造新利器

穩定性為ISA發展關鍵

RISC-V之目標是從其他處理器ISA錯誤中汲取教訓。關鍵是穩定性,包括指令集和內核,以及晶片設計人員、編譯器製造商、作業系統架構師和開發工具提供商等。這對於鼓勵工程師盡可能多在產業鏈中使用這種開源技術,使更強大處理器內核得到更多獲取和使用至關重要。特定應用開發人員可以使用最小記憶體和功耗來優化其固化的ISA代碼,但仍可擴展並與未來設備相容。這允許處理器內核開發人員應對指令集的各種不同實施方式,從簡單管線到具有多階和無序執行管線。這些會具有不同的延遲、尺寸大小和功耗,但彼此之間都具有底層相容性,以及生態圈中包含的工具。

在整個生態圈中提供這種穩定性是新指令集的關鍵。它的設計考慮了32位元、64位元和128位元位址空間,因此可以保持它們之間的相容性。該架構還專門設計具有可延伸性,以便為晶片製造商提供差異化和未來應用場景所需的客製化服務,但ISA的基礎仍然是絕對不受影響。

ISA開放性使軟體架構更有影響力

128位元ISA依然未確定,因為在嵌入式系統中,如此之大儲存容量幾乎沒有實際意義。但是,該體系架構將支援更大的位址空間這一事實凸顯了其前瞻性思維方式。這意味著為RISC-V編寫或移植到其上的軟體將永遠能夠在所有類似的RISC-V內核上運作,為軟體管理員提供了堅實的基礎,可以保護他們的軟體投資。由於ISA是開放的,因此可以開發多種硬體實施方案,因此軟體架構可以在最終硬體實施中變得更有影響力。

對於硬體設計人員之輸入會使RISC-V內核更加以軟體為中心,這導致出現了許多採用ISA的處理器內核,以及大量基於這些內核的系統單晶片(SoC),Codasip、Syntacore、Hex Five和T-Head都開發相應的內核,而SiFive則推出了一系列32位元和64位元SoC。

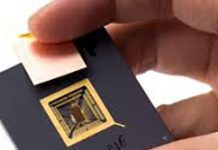

SiFive由Yunsup Lee(RISC-V最初創建者之一)共同創立,作為SoC平台家族,於2017年推出首個RISC-V內核,並增加了對內核和晶片支援(圖1)。這些元件採用28nm製程,用於64位元多核Linux實施,或者採用180nm製程,適用於具有多種周邊設備的32位元低成本物聯網市場。

圖1 SiFive的U500 64位元多核開源處理器。

該公司的Freedom平台包括完整的軟體規格、用於開發作業系統的板級支援包(BSP)、開發板和基礎晶片等,允許客戶創建自己的晶片增強型設計和客製化產品。Freedom U500家族是一款完全支援Linux的嵌入式應用處理器,採用多核RISC-V CPU,運作速度為1.6GHz甚至更高,支援加速器和快取記憶體一致性,適於機器學習、儲存和網路等應用。它支援標準的高速周邊設備,包括PCIe 3.0、USB 3.0、Gb乙太網路和DDR3/DDR4。

Freedom E300家族為設計用於物聯網和可穿戴設備市場的嵌入式微控制器(圖2)。基於Freedom E310的HiFive1相容Arduino的RISC-V開發套件採用SiFive的E31 CPU Coreplex,是一款高性能32位元RV32IMAC內核,能夠以超過320MHz的頻率運作(圖3)。

圖2 採用RISC-V ISA的E300開源32位元MCU家族。

圖3 HiFive1 RISC-V開發套件。

SiFive還將RISC-V指令集用於據稱是世界上最小嵌入式處理器內核。S2內核IP家族是一個可配置內核,可以小到只具有13,500個邏輯閘(在RV32E 32位元版本狀況下)。S21 64位元嵌入式內核具有獨立指令和資料匯流排,以及兩組緊密整合的記憶體(TIM),這使SoC能夠擁有一個始終開啟的低功耗32位元CPU,可與高階64位元CPU結合使用,當某些應用需要更高性能時(例如語音啟動智慧型設備),該CPU可以開啟。這種開發配置有助於滿足機器學習和物聯網連接設備日益成長之需求,其中即時載荷已經產生了對邊緣處明顯增強的嵌入式智慧之巨大需求。

RISC-V的開源特性已經為Kendryte、efabless和low RISC等新創公司開闢了SoC設計,但更多主流晶片提供商也在使用該技術。Microsemi(現為Microchip一部分)已經為SiFive生產了一些開發板,而NXP則擁有自己的RISC-V晶片。Andes Technology和Greenwave也開發了基於ISA的多種IC。Faraday Technology已將ISA用於ASIC平台,目標是下一代邊緣人工智慧(AI)和物聯網SoC的設計和批量生產。其彙集了RISC-V內核IP整合和SoC設計驗證,以及全功能參考設計套件,其中包括即時作業系統(RTOS)和周邊設備驅動程式,所有這些都採用55nm制程,適用於電池供電的邊緣設備。這突顯了硬體製造商可以在標準ISA基礎上實現差異化。Faraday Technology在其平台中整合有動態電壓和頻率調節(DVFS)、功率模式切換和快速系統喚醒等功能,也可以安全地整合軟體庫和驅動程式,以確保晶片在實現特定的介面、感測和電源管理功能時能夠無縫工作。

RISC-V ISA可與各種工具共同使用

RISC-V ISA的另一個優勢是它能夠與各種工具一起使用。Microsemi在其FPGA產品中使用了ISA,其中包括Express Logic的ThreadX、華為LiteOS和Micrium µC/OS-II等多種嵌入式作業系統。主機板包括RTG4開發套件和PolarFire評估套件等,其中還包括Microsemi和Olimex的除錯硬體鑰匙(Debug...