先進製程

SEMI:整合產官學關鍵能量 喜迎半導體新黃金50年

SEMICON Taiwan 2020 Hybrid 25日圓滿落幕

SEMICON Taiwan國際半導體展於23日於南港展覽館一館正式登場,推出全新線上SEMICON Taiwan 2020 Hybrid平台,以虛實整合方式同步展出線上線下多場精彩活動。SEMI國際半導體產業協會於22日展前記者會宣布將擴大半導體產業永續發展計劃,從政府、產業、人才三面向,打造更緊密強大的台灣半導體產業聚落。在計劃第一階段將聚焦人才培育主題,並由SEMI與104資訊科技簽署MOU合作交流備忘錄,期許未來一起共同孕育台灣半導體產學頂尖人才。

為推動台灣半導體產業以長遠、具體的方式策略性成長,活動中邀請到中華民國經濟部工業局局長呂正華、日月光半導體總經理暨執行長吳田玉、台灣半導體產業協會常務理事暨鈺創科技股份有限公司董事長暨執行長盧超群與104資訊科技獵才招聘事業群資深副總經理晉麗明等政府產業代表出席,凝聚產官學研力量,以國家之力打造台灣半導體全面升級,在5G、AI新時代中鞏固國際產業關鍵地位。

憑藉現有優勢,台灣半導體產業在世界站穩腳步

日月光半導體總經理暨執行長吳田玉表示:「台灣半導體產業相較其它世界強國,擁有相對完整的產業供應鏈,在此優勢下,面對後疫情時代的各種變數與挑戰,除了與時俱進的產業鏈發展、生產彈性及遠距溝通技術的加強,台灣也應持續推動相關政策調整與人才培育,以更加穩固自身半導體產業競爭力,持續走在全球競賽的前端,發展永續共赢的未來。」

台灣半導體產業協會常務理事暨鈺創科技董事長暨執行長盧超群也對台灣今年走過疫情的半導體市場表現表示讚賞:「因為疫情所帶動的零接觸經濟連帶促成了半導體產業的諸多商機。台灣受疫情影響小,又因在製程技術及IC設計的領先發展鞏固了國際產業關鍵地位,我們一方面仍應審慎以對,另一方面則要全力把握此等商機,快速投入資源,帶動整體產業技術提升,與世界各國加速合作!」

中華民國經濟部工業局局長呂正華對未來也展現信心:「半導體產業是台灣重要經濟命脈,政府各部門會積極偕同SEMI與產業代表一同整合各方資源並推動跨界合作,以打造台灣成為半導體先進製程中心做為核心目標。」

SEMI全球行銷長暨台灣區總裁曹世綸指出:「台灣半導體藉由不斷突破的技術能量以及強大採購動能,持續帶動整體產業成長,過去10年有高達7次是全球最大半導體設備投資區域,未來10年的投資動能也有望朝先進製程布局。若能掌握既有核心優勢訂定長遠發展計劃、佈建在地完整產業生態系,將有機會搶佔亞太半導體中心,推動國家經濟成長、提升台灣整體競爭力。」

人才為推動產業持續成長的關鍵 SEMI與104攜手強化產學人才培育

高科技的人才資源為推動技術研發的基礎要素,半導體產業卻面臨嚴峻的人才斷層危機。面對近幾年國家人才長期不足及外流的挑戰,SEMI在今日會上宣布與104資訊科技簽署合作備忘錄(MOU),期望攜手一同規劃長期人才培育發展合作方案,透過強化產學技術合作提升國家競爭力。104資訊科技獵才招聘事業群資深副總經理晉麗明提到:「104資訊科技與SEMI首次針對半導體人才共同出版《半導體產業與人才白皮書》,希望針對台灣半導體人才建立完整、有策略性的培育發展方向。」

此外,SEMICON Taiwan多年舉辦「人才培育特展」,在展會中除了多場主題論壇規劃外,另舉辦人才媒合、一對一面試等系列活動,助力學生在未來職涯道路上掌握先機。

串聯線上線下 SEMICON Taiwan 2020 Hybrid平台展出半導體智慧未來

SEMICON Taiwan 2020國際半導體展於本月23日至25日在南港展覽館一館圓滿落幕。今年展會聚焦「先進製程」、「智慧製造」與「綠色製造」三大主題,展示半導體上下游產業鏈最尖端創新的技術。為了讓無法親自到場的海外觀眾一同參與年度半導體盛宴,全新虛實整合「SEMICON Taiwan 2020 Hybrid」平台,除了提供虛擬展館的參觀體驗外,部分熱門論壇與活動也開放線上直播觀看;另可透過1對1即時訊息與展商進行交流、創造更多合作機會,此平台於9月23日正式上線。

每年眾所注目的大師論壇(Master Forum)邀請台積電董事長劉德音、鴻海科技副董事長李傑、意法半導體總裁暨執行長Jean-Marc Chery等企業領袖,共同剖析AI及5G科技趨勢下的機會與挑戰。另外,展區亮點「高科技智慧製造特展」,結合智慧製造解決方案展出多元應用可能,為產業打造智慧製造與資安國際交流平台。針對引領產業前瞻技術的「異質整合」專區,則以實際應用角度展示遠傳5G多元應用、聯發科技IC設計以及日月光互動智慧城市SiP封裝解決方案平台等呈現技術解方;展區中的「化合物半導體創新應用館」將展示Jaguar新一代電動車I-PACE以及遠傳電信5G基地台,完整呈現化合物半導體製造產業鏈至系統應用端的樣貌。

2020年是SEMI成立50周年,同時也是SEMICON Taiwan第25周年,象徵半導體產業進入下一個發展階段的重要里程碑。展望未來,SEMI表示將繼續以產業永續、企業成長、人才發展為目標,為產官學三方暢通合作橋梁,結合政府、協會及企業能量打造完整半導體產業聚落,提升台灣國際競爭力。

台積電正式宣布 有意於美國設立先進晶圓廠

台積電今(15)日宣布在與美國聯邦政府及亞利桑那州的共同理解和其支持下,有意於美國興建且營運一座先進晶圓廠。

此座將設立於亞利桑那州的廠房,將採用台積電的5奈米製程技術生產半導體晶片,規劃月產能為20,000片晶圓,將直接創造超過1,600個高科技專業工作機會,並間接創造半導體產業生態系統中上千個工作機會。

該晶圓廠將於2021年動工,於2024年開始量產。台積電預估,2021年至2029年,該公司在此專案上的支出(包括資本支出)約120億美元。

台積電表示,這座先進晶圓廠不僅能使該公司為客戶和夥伴提供更好的服務,也為台積公司提供了更多吸引全球人才的機會。此專案對於充滿活力及具有競爭力的美國半導體生態系統來說具有重要的策略性意義,它使具業界領先地位的美國公司能於美國境內生產其最先進的半導體產品,同時又能受惠於世界級的半導體晶圓製造服務公司及其生態系統的地理鄰近性。

台積電期待與美國當局及亞利桑那州於此專案上繼續維持鞏固的夥伴關係,此專案需要台積公司大量的資本和技術投資,而美國強健的投資環境及其優秀的人才使得此專案及未來於美國的投資對台積公司來說極具吸引力。

美國採行具前瞻性的投資政策為其半導體技術營運創造出具全球競爭力的環境,此環境對於本專案的成功至關重要。這也使台積電對此項投資及未來與其供應鏈夥伴投資的成功皆充滿信心。

台積公司目前在美國華盛頓州卡馬斯市設有一座晶圓廠,並在德州奧斯汀市、加州聖何西市皆設有設計中心。此座位於亞利桑那州的廠房將成為台積公司在美國的第二個生產基地。

電晶體密度提升速度減緩 摩爾定律越走越艱辛

引領半導體產業向前邁進的摩爾定律(Moore’s Law),近年來明顯遇到瓶頸。記憶體、處理器等使用先進邏輯製程生產的晶片,均已很難按照摩爾定律預期的速度,實現每兩年電晶體數量翻倍。

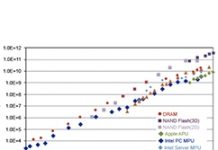

研究機構IC Insights整理英特爾(Intel)、美國半導體產業協會(SIA)等半導體公司、產業組織的資料,發現不管是DRAM、NAND Flash、CPU或GPU,這些使用最先進邏輯製程的晶片,都已經先後遇上電晶體數量成長速度放緩的問題。

以NAND Flash為例,雖然目前業界已普遍轉向3D結構,但NAND Flash的密度在2012年以後,每年成長速度就只有30~35%。英特爾CPU的電晶體數量,在2010年以前的平均成長速度還有40%,但此後的成長速度則只剩下一半。

蘋果的A系列應用處理器算是比較特別的例外,自2013年以來,A系列應用處理器的電晶體數量成長速度,還能維持在每年40%以上。

滿足高效/低成本需求 Chiplets市場蓄勢待發

人工智慧(AI)、車聯網、5G等應用相繼興起,且皆須使用到高速運算、高速傳輸、低延遲、低耗能的先進功能晶片。為此,晶圓代工、封裝業者除了持續朝先進製程(5奈米、3奈米)邁進外,也開始研發新一代製程技術以突破摩爾定律瓶頸,而Chiplets可實現更小更緊湊的運算系統結構,因此備受矚目,眾多半導體廠已相繼投入,相關產品也紛紛問世。

高效/低成本是Chiplets崛起關鍵

益華(Cadence)產品市場總監孫自君(圖1)表示,人工智慧與5G快速興起,相關應用陸續浮現,成為推動半導體產業未來成長的重要動力。這些應用皆需採用高速運算、高速傳輸、低延遲、低耗能的先進功能晶片。不過,製程微縮技術變得愈來愈困難,例如為了因應各式AI應用,晶片需更高的運算效能,這使得處理器核心數量、所搭配的記憶體容量、I/O數目都急速增加,要整合的元件數量越來越多,即便是使用先進製程,要將晶片尺寸更進一步縮小仍是十分吃力。

圖1 益華產品市場總監孫自君表示,晶片小型化不僅複雜且成本昂貴。

孫自君進一步說明,即便成功小型化之後,仍還有許多要素須考量,例如功耗、散熱等。小型化意味著將各種元件整合在一起,進行運算時所產生的熱能要如何有效的散熱是一大關鍵,因為熱會影響元件電性能力;另外,要達到更好的運算效率,也意味著功率損耗愈多。換言之,晶片小型化要兼具效能、體積、低功耗、散熱等多種要素,要在這麼小的空間實現這麼多(或是做更多)的事情,難度很高;若再從IP的角度思考,要將各式各樣的IP(如記憶體IP、微控制器IP、類比線路IP等)整合在一起,接著進行各種組合試算和驗證,同樣也是要花費許多時間。所以,晶片微縮過程可說既精密又複雜,也使得造價變得更加昂貴。

孫自君指出,業者都是追求獲利,而如何降低成本是最基本的考量,隨著晶片微縮變得越來越複雜、成本也越來越高,業者也會開始思考,究竟是不是所有晶片都需要小型化,畢竟不是所有公司都有能力投入,也不是所有應用都需要非常高的運算效能。也因此,IC設計業、晶圓代工、封裝業者轉向發展晶片小型化外的製程技術,Chiplets的概念及方式也因而開始受到關注。

工研院產科國際所分析師楊啟鑫表示,Chiplets屬於業界因為摩爾定律面臨瓶頸所做的技術替代方案,更早則是源於1970年代誕生的多晶片模組。小晶片是指由多個同質、異質等較小的晶片組成大晶片的概念。先進製程成本急速上升,是故以小晶片方式以提高良率及降低晶片成本。小晶片可以減少晶片設計時程,加速晶片Time to market時間。

楊啟鑫補充,電子終端產品朝向高整合趨勢發展,對於高效能晶片的需求持續增加,然而,隨著摩爾定律逐漸趨緩,在持續提升產品性能過程中,如果為了整合新功能晶片模組而增大晶片面積,將提高先進製程大晶片成本和面臨低良率問題。而不同於SoC晶片,將大尺寸的多核心設計分散到較小的小晶片設計更能滿足現今的高效能運算處理器。此彈性的設計方式可以讓晶片功能分散到以不同製程技術生產的個別小晶片中,提升設計靈活性、更好的良率及節省成本優勢。

換言之,讓高效能晶片使用最先進製程製造,其他則使用符合經濟效益的製程製造(如I/O晶片、記憶體晶片)。從原來設計在同一個SoC中的晶片被分拆成許多不同的小晶片分開製造再加以封裝或組裝,故稱此分拆之晶片為小晶片Chiplets。

總結來說,Chiplets有著三大好處。首先,採用7nm、5nm甚至3nm等先進製程設計SoC的成本相當高昂,特別是模擬電路、I/O等愈來愈難以隨著製程技術縮小;而透過Chiplets則可以克服此一挑戰,因Chiplets是將電路分割成獨立的小晶片,並各自強化功能、製程技術及尺寸,最後整合在一起。此外,基於Chiplets還可以使用現有的成熟晶片降低開發和驗證成本。

接著,Chiplets可以滿足規模較小、較具成本考量的產品。如同前面所述,先進製程SoC造價昂貴,對於許多業者而言,其公司規模及產品銷售量並不足以支撐先進製程的成本;因此,Chiplets遂成為一種切實可行且具吸引力的方式。

至於第三個好處便是,與使用先進製程、從頭開發SoC相比,Chiplets可以加快產品上市時間,越快推出產品,這就意味著可以越早占領市場,提高潛在收入與競爭優勢。

孫自君補充,當然,除此之外,Chiplets還有著IP重用(IP Reuse)、靈活設計、低成本訂製等特點。特別是IP Reuse,目前像是藍牙、Wi-Fi都已有成熟、完整的IP,若是要將這些IP也都採用先進製程,就必須重新開IP,將IP換成5nm、3nm,接著再付一次IP授權費,以及再付費給晶圓代工業者,再加上後續的驗證、PCB板測試等,這花費的時間和成本太大;也因此,Chiplets的出現對IP Reuse起了很大的作用。

半導體業加快Chiplets產品腳步

顯而易見,在製程微縮技術只有少數幾家晶圓代工、IC製造業者可發展的情況下,異質整合(Heterogeneous Integration Design Architecture System, HIDAS)成為IC晶片的創新動能,Chiplets便趁勢崛起,成為半導體產業熱門話題,IC設計業者、IP供應商、晶圓代工廠等也開始加速產品布局。

英特爾/AMD產品競出

英特爾(Intel)日前所發布的Intel Stratix 10 GX 10M FPGA便是採用Chiplets設計(圖2),以達到更高的元件密度和容量。該產品是以現有的Intel Stratix 10 FPGA架構及英特爾先進的嵌入式多晶片互連橋接(EMIB)技術為基礎所設計,運用了EMIB技術融合兩個高密度Intel Stratix 10 GX FPGA核心邏輯晶片(每個晶片容量為510萬個邏輯單元)以及相應的I/O單元。

圖2 英特爾近期發布的Stratix 10...

半導體業大者恆大 2019資本支出集中率再攀高

產業研究機構IC Insights發表主要半導體公司2019年和2020年的資本支出預測,2019年排名前五位的公司(三星、英特爾、台積電、SK海力士和美光)在半導體產業資本支出中所占的比重將達到68%的歷史新高,超過2013年和2018年創下的67%高點。回顧1994年,前五名支出僅占產業總支出的25%,因此大公司增加其資本支出比重的趨勢一直沒有減弱,再次證明半導體產業大者恆大的走向。

2019年排名前五位的半導體廠商資本支出所占的比重將達到68%的歷史新高。

三星和台積電2019年第四季與整年度資本支出顯示,兩家公司在年初時的支出都相對較低,然後在第二季支出增加到了較為適度的水平。此外,兩家公司在第三技法說會中都宣布,計劃將第四季的資本支出增加到創紀錄的水準。

台積電計劃將2019年第四季的資本支出較第三季增加64%至51.47億美元。這將是該公司季度支出的歷史新高,比2014年第一季度的37.99億美元的歷史記錄高出36%。台積電TSMC 7奈米(nm)製程的需求非常強勁,預計該製程將占2019年第四季營收的33%。目前,其大部分投資將針對7奈米和5奈米技術的的新增產能。

另一家半導體大廠三星則宣布了計劃在2019年四季創下其半導體支出的單季新高記錄,該季大部分資本支出專用於建立記憶體設備,以滿足中長期需求。三星2019年第四季資本支出預計達79億美元,與第三季相比,成長81%。比該公司在2017年第四季的單季最高支出68.77億美元高出15%。

對於2019年全年,三星的半導體資本支出預計為199億美元,較2018年的支出下降8%。然而,該公司2017、2018和2019年的半導體集團資本支出總額預計為658億美元,較同期第二大支出的英特爾多53%。此外,三星在2017~2019年的658億美元半導體資本支出將是同期所有中國本土半導體廠商總支出308億美元的兩倍多。無論是台積電或三星半導體,想要在產業中保持領先從來就不是件簡單的事,包括更多資本與研發都是必要的投資。

釐清翹曲程度 IC SMT早夭異常迎刃而解

先進製程零件材料堆疊複雜為翹曲主因

為什麼翹曲導致後續可靠度問題,近期發生頻率這麼高呢?主要原因來自於越來越多廠商,在開發先進製程的晶片;而先進製程晶片,是由非常多不同材質、不同功能的晶片堆疊起來。例如MCM多晶片模組、系統級封裝與Fan-in/Fan-out等,這樣的元件使用的材料相當複雜且多元,堆疊在一起時,因材質本身熱膨脹係數不同(CTE)就會產生翹曲(圖1)。

圖1 先進製程晶片元件或多或少都會有翹曲現象,變形量符合IPC規範控制在一定程度內,都不會影響後續元件上板品質。

資料來源:左圖為iST;右圖為Akrometrix

除了晶片元件本身會發生翹曲外,晶片透過表面黏著技術(SMT)結合到電路板時,因晶片與電路板CTE不同,翹曲的狀況就會加劇。而當翹曲超過一定的幅度,就會造成SMT的焊接品質不良,也影響後續的可靠度測試結果。也因此,如何妥善安排這些溫度特性不同的材料依序堆疊,在加熱與散熱時不會互相影響,是相當嚴苛的技術挑戰。

在5~10年前,翹曲幅度控制在6~8mil以內,都還不至於影響後續SMT等製程;然而這幾年先進製程的材料種類複雜且反覆堆疊,受到溫度影響後的變形量已比5~10年前的樣品來的嚴重。根據宜特板階可靠度實驗室發現,隨著未來接腳數越來越多,晶片上板時,使錫膏(Solder Paste)與錫球可以接合順利所使用的治具鋼板(Stencil),厚度就會越來越薄(圖2),繼續維持在6~8mil的翹曲幅度,是否能夠像早期不至於影響SMT製程品質,令人堪憂。

圖2 左圖為傳統PCB,鋼板因接腳數較少,錫球用的不多,相對鋼板不需要太薄;右圖表示隨著先進製程的元件接腳數變多,錫球需要較多,鋼板就需要較薄。

資料來源:iST

PCB翹曲過大易導致空焊與短路

當然,也不能將所有的問題放在零件身上,因為PCB也會有翹曲的狀況。原先以為PCB厚度只要超過1.6mm,PCB本身發生翹曲的機率會較小,但實則不然。宜特板階可靠度實驗室曾經有個經典案例,IC上板至PCB時,以為只是IC零件有翹曲問題(圖3),但做了一連串的SMT製程參數調整之後,依舊發現空焊與短路問題,最終發現原因,不只是IC有翹曲,PCB也有翹曲,且翹曲變形量過大造成SMT異常。

圖3 左圖為哭臉變形元件使用哭臉鋼板;右圖為笑臉變形元件使用笑臉鋼板

資料來源:iST

除此之外,空焊短路還不是最嚴重的問題。更嚴重的是翹曲後的焊點,將會呈現拉伸與擠壓的形狀,完美的焊點應該是接近「球型」,而翹曲將導致焊點呈現「瘦高」或「矮胖」形狀,這些「非球型」的焊點,容易產生應力集中而斷裂,使得後續在可靠度驗證中,出現早夭現象的機率提高。

透過SMT解決翹曲方式,一是透過修改鋼板治具開孔大小,針對間距較大的地方給予較多的錫膏;二是透過鋼板治具抑制零件的變形。

修改SMT鋼板治具開孔大小治標不治本

然而這兩種解法必須多次驗證才能找出SMT最佳條件,若無法有效解決翹曲問題,可能得退回設計階段找尋其他材料來取代,曠日廢時。因此,若能在SMT前,取得晶片與PCB翹曲相關資訊。將可事半功倍。宜特板階可靠度實驗室使用相關量測翹曲的設備,可以針對元件與PCB來模擬翹曲的程度,再去調整SMT的參數設定,確保SMT過程中有良好的焊接品質;如此可避免因不良焊接品質導致影響可靠度驗證以及不必要的成本開銷。

翹曲量測的原理,是應用樣品上的參考光柵和它的影子之間的幾何干擾產生摩爾雲紋分布圖,進而計算出各圖元位置中的相對垂直位移,並可應用於模擬SMT回流焊溫度和操作環境條件、同時捕捉一個完整的歷史翹曲位移表現。而量測分析的速度非常快,約半小時就可得知元件在不同溫度的變形量,也能模擬溫度循環的環境,協助客戶與可靠度測試進行搭配,觀察產品在哪個溫度會達到最大的變形量, 並能在測試中思考如何改善與預防。

總結來說,在宜特板階可靠度實驗室觀察中,翹曲的問題勢必會持續存在,我們無法控制材料的特性,但如果透過篩選的方式,找出翹曲方向相同的零件與PCB,我們認為這不僅不會降低可靠度的壽命,也能協助IC設計業者找到完美翹曲比例,達到1+1>2的價值。

(本文作者為宜特科技零組件暨板階工程部經理)

強化先進製程技術 新材料運用蓄勢待發

物聯網、工業自動化、人工智慧、自動駕駛、5G通訊等應用對晶片性能要求越來越高,為此,除了半導體技術、架構須持續演進外,材料也是推動半導體先進製程的其中一項關鍵。為此,半導體材料供應商如英特格(Entegris) ,便致力投入先進材料測試、發展,並提供半導體生態系統一貫的解決方案,協助晶圓代工、封裝等業者因應各種挑戰。

英特格資深首席科學家鄭君飛表示,要強化晶片效能,不外乎就是從三大面向著手,分別是製程、架構和材料。製程方面就是不斷朝微縮化發展,像是從16、14奈米一直邁進到7奈米、5奈米等;而架構則是從Planar到FinFET,再轉向GAA發展。然而,當製程、架構開始遇到瓶頸(如技術、成本)而難以有效增強晶片性能時,便可從材料著手。

鄭君飛說明,簡而言之,為了迎接這些挑戰,不同時期有不同策略。在個人電腦時代仰賴微縮技術,因為裝置也越來越小;到了行動裝置時代則導入新的材料增加效能,以延續摩爾定律。到了今天這個時代,不只需要微縮技術,更仰賴3D技術以及新的架構。過程中,材料技術不斷演進,且應用的材料本質也開始改變。為此,英特格也不斷嘗試新材料於半導體製程的研發。

英特格資深首席科學家鄭君飛表示,英特格的使命是運用科學為基礎提供解決方案,協助半導體客戶在先進製程上應對各種挑戰。

像是在閘極全環(GAA)結構導入鍺(Ge)。英特格指出,在GAA結構中,可能需要用到多個堆疊的奈米線,才能在特定的體積下提供足夠的開啟電流以獲得高速效能。而鍺的電洞遷移率高於矽,因此可以提升P型金氧化半導體(PMOS)電晶體速度,有利在5奈米下的製程實現減少耗電、提升性能的目標。

除了嘗試在GAA架構導入鍺外,英特格也嘗試了將導線材料從銅轉成鈷的測試。當電晶體體積縮小,傳統的銅(Cu)導線將會到達微縮下限,特別是當製程走到10奈米以下時,銅線電阻會迅速增加;而若果改用可適用較薄阻障層的鈷(Co)金屬,則可規避掉這個問題。當鈷金屬導體體積變大,接觸電阻就會跟著變小。

鄭君飛表示,在先進半導體製程導入新材料,目前仍是在測試階段,雖說已可確認這些新材料有助於先進半導體製程發展,但仍有許多挑戰待克服,像是可靠性、如何量產、價格等。英特格未來會持續投入相關研究,運用科學為基礎提供解決方案,協助半導體客戶在先進製程上應對各種挑戰。

鄭君飛也說,在半導體先進製程中,需要新的金屬材料去提高阻抗與可靠度,當金屬材料改變時,下游製程,像是如何清洗都須要一併改變,因此,半導體製程中導入新的材料絕對不是一個簡單的過程。因此,該公司也會提供半導體生態系統一貫的解決方案,像是汙染控制、晶圓運送/儲存、化學品安全等。

降低先進製程設計成本 默克提DSA方案

人工智慧、自駕車、大數據、物聯網等科技趨勢正急速推動著電子產業的發展,未來對功能更強大的IC晶片的需求將非常可觀,為此,半導體持續朝先進製程發展;而為有效降低多重曝光的成本,默克(Merck)提出定向自組裝(DSA)解決方案,以加速半晶片微型化技術發展。

默克全球半導體事業體負責人暨執行副總裁Anand Nambiar表示,摩爾定律逐漸走向極限,為打造更高性能的晶片,半導體製程持續走向微型化發展,然而,這些製程技術的出現,雖說可以再進一步提高晶片性能,但也代表半導體製程與結構更趨複雜,成本也會隨之上升。像是5奈米的曝光步驟就會比7奈米多,也因此所花費的時間和成本也會更高;若再搭配EUV,其成本更是可觀。也因此,為有效降低多重曝光的成本及時間,默克便提出DSA創新解決方案。

默克全球半導體事業體負責人暨執行副總裁Anand Nambiar指出,半導體製程持續走向微型化發展,卻也使晶片結構更加複雜及成本提高。

據悉,DSA 牽涉了一些不同的材料,其中最重要的是所謂的塊狀共聚合物(BCP),這是由兩股不同聚合物以端對端交聯而成。這些BCP能夠在特定條件下,沿著導電結構自行排列為一致的形狀,形成了未來電腦晶片的極精細電晶體和印刷導電體的基礎。

Nambiar指出,簡而言之,DSA材料提供合乎成本效益的圖案化解決方案,可用於製作更先進的晶片尺寸。根據比利時微電子研究中心(Imec)研究顯示,採用DSA解決方案,可有效降低約20%的成本。

Nambiar進一步說明,DSA應用非常廣泛,不僅是可用於傳統邏輯晶片的先進製程,其餘像是記憶體、感測器等也可應用此一技術。舉例來說,目前記憶體堆疊層數不斷增加,從以往的32層增加到128,甚至未來還要達到256層,這樣的製程都需要多重曝光的步驟;而DSA便可在其中扮演關鍵角色,在有效降低整體成本同時,也可助力高性能晶片的設計。

晶片微縮難度高 半導體製程技術日新又新

簡化製程 EUV扮關鍵要角

艾司摩爾(ASML)資深市場策略總監Boudewijn Sluijk(圖1)表示,VR/AR、自動駕駛、5G、大數據及AI等,持續推動半導體產業發展,為滿足各式應用、資料傳輸,以及演算法需求,晶片效能不斷提高的同時,還須降低成本,而極紫外光(EUV)在先進製程中便扮演關鍵的角色。

圖1 ASML資深市場策略總監Boudewijn Sluijk表示,自動駕駛、5G、AI等新應用推升晶片性能發展。

Sluijk指出,過往採用ArFi LE4 Patterning或是ArFi SAQP進行曝光的話,要實現7nm、5nm,須經過許多步驟。例如用ArFi LE4 Patterning需要4個光罩、4次曝光;用ArFi SAQP需要6個光罩、9次曝光,而EUV只需1個光罩、1次曝光(圖2)。採用EUV技術不但可有效簡化製程,加快產品設計時程,也因為曝光次數明顯減少,因而可有效降低成本,滿足晶片設計高效能、低成本的需求,因此,市場對於EUV的需求有增無減。

圖2 EUV技術可有效減少曝光次數,進而降低成本。

資料來源:ASML

據悉,ASML的EUV系統現在可用於7nm生產,滿足客戶對可用性、產量和大量生產的需求。截至2019第二季季末,半導體界已經有51個EUV系統被建置(包含NXE:33xx、NXE:3400B),而該公司在2019年的銷售目標為30台EUV。

據悉,ASML目前已出貨11台EUV極紫外光系統,而在第二季再度接獲10台EUV極紫外光系統的訂單,顯示市場對於EUV設備的需求相當強勁。因此,ASML的出貨計畫將著重於2019年下半年和第四季,而2019年的整體營收目標維持不變。

然而,隨著晶圓產能不斷增加,ASML也持續推出生產力更高的EUV設備。Sluijk透露,目前EUV系統在晶圓廠客戶端每天生產的晶圓數量超過1,000片,而ASML持續強化EUV微影系統「NXE:3400C」的量產效能,不僅在ASML廠內展示每小時曝光超過170片晶圓的實力,在客戶端實際生產記憶體晶片的製造條件下,也成功達到每天曝光超過2,000片晶圓的成果,甚至達到2,200片的紀錄。另外,ASML也計畫在2020上半年推出生產力更高的設備,將NXE:3400C的生產率提升至>185wph。

除提升設備生產量之外,因應未來先進節點,ASML也計畫推出全新EUV設備,名稱為EXE,不僅擁有新穎的光學設計和明顯更快的平台,且數值孔徑更高,為0.55(High-NA),進一步將EUV平台延伸至3nm節點以下,擴展EUV在未來先進節點中的價值。

Sluijk說明,此一產品將使幾何式晶片微縮(Geometric Chip Scaling)大幅躍進,其所提供的分辨率和微影疊對(Overlay)能力比現有的NXE:3400高上70%。EXE平台旨在實現多種未來節點,首先從3奈米開始,接著是密度相近的記憶體節點。另外,EXE平台有著新穎的光學設計,並具備更高的生產力和更高的對比度,以及更高的生產量,每個小時>185wph,且Reticle Stage比NXE:3400快上4倍;Wafer Stage比NXE:3400快上2倍。

Sluijk指出,該公司的EUV平台擴展了客戶的邏輯晶片和DRAM的產品路線圖,透過提供更好的分辨率、更先進的性能,以及逐年降低的成本,EUV產品將會在未來十年到達一個經濟實惠的規模。

滿足晶片設計PPAC需求 蝕刻/沉積技術不容小覷

科林研發(Lam Research)副總裁Yang Pan(圖3)認為,在高級節點,最重要的趨勢是垂直縮放(Vertical Scaling)以滿足「功率-性能-面積-成本(Power Performance Area Cost, PPAC)」的需求,特別是記憶體和邏輯晶片;垂直縮放過去5年徹底改變了NAND產業,目前3D NAND的出貨量多於平面NAND(Planar NAND)。垂直縮放的實現須透過沉積和蝕刻中的High Aspect Ratio(HAR)製程實現,而這是該公司所擅長的。

圖3 Lam...

結合雲端高運算/低成本/靈活特性 先進製程IC設計複雜度驟降

多元新興應用(AI、5G等)崛起,使得IC不僅要高效能,同時還要小體積、低功耗,這也使得IC設計的複雜度與時間大增。要達到這些條件,IC設計時所需的運算資源是過去的數倍,面對高運算、成本效益的考量,加上為了加快IC設計時程,半導體產業開始結合雲端技術,將雲作為IC設計平台,雲端技術用來輔助IC開發的契機也因而湧現。

台積電推雲端聯盟引領IC設計上雲風潮

台積電在2018年宣布首度在開放創新平台(Open Innovation Platform, OIP)上提供「虛擬設計環境(Virtual Design Environment, VDE),協助客戶靈活運用雲端運算環境,充分使用台積電的OIP設計基礎建設,安全地在雲端進行晶片設計。

OIP VDE是台積電與OIP上最新成立的「雲端聯盟」的創始成員合作,包括亞馬遜雲端服務(AWS)、益華電腦(Cadence)、微軟Azure(Microsoft Azure)以及新思科技(Synopsys)的合作成果,在雲端提供RTL-to-GDSII的數位設計以及schematic capture-to-GDSII的客製化設計能力。

OIP VDE裡的數位設計以及客製化設計流程,皆於雲端運算的環境上,結合製程技術檔(Process Technology File)、製程設計套件(Process Design Kit, PDK)、基礎矽智財(Foundation IP),以及設計參考流程(Reference Flows)等的OIP晶片設計輔助資料檔,並通過了充分的測試。

同時,為了降低客戶首度採用雲端的門檻,並且確保客戶獲得充分的技術支援,Cadence與Synopsys將扮演單一窗口的角色,協助客戶架設VDE並且提供第一線的支援。

台積電技術發展副總經理侯永清表示,雲端無所不在,並且會全面影響未來晶片設計的進行。台積電是第一家與設計生態環境夥伴與雲端服務公司合作提供雲端設計解決方案的專業積體電路製造服務公司。OIP VDE提供客戶彈性、安全,透過矽晶認證的雲端設計解決方案,能夠幫助他們按照需求有效地擴充運算設備,進而加速下一代系統晶片的上市時間。

而台積電在2018年推出OIP雲端聯盟後,也持續擴增其規模,添加更多合作夥伴,像是明導國際(Mentor)便成為新的聯盟生力軍,拓展此一平台生態系統的規模。

台積電指出,Mentor已成功通過台積電的認證成為雲端聯盟的新成員,其於雲端保護矽智財的程序皆符合台積電的標準。此外,台積電驗證了Mentor Calibre實體驗證電子設計自動化解決方案,能夠有效地藉由雲端運算的擴展性加速完成晶片實體驗證。

侯永清指出,自從台積電率先成立雲端聯盟後,已經看到越來越多的晶片設計業者採用雲端解決方案。因此,我們更進一步擴大雲端聯盟的規模,並且深化夥伴關係。看到不同規模的客戶在利用台積電的先進製程進行設計時,藉由雲端運算來提高生產力。目前已經有客戶採用雲端聯盟的解決方案完成7奈米的產品設計定案。此外,台積電也利用雲端來進行5奈米的開發,以更快速地提供記憶體、標準元件庫、以及電子設計自動化設計基礎架構給客戶,幫助客戶取得競爭優勢,更快的將產品上市,並且達到更高的品質。

降成本/高運算需求增雲端方案趁勢起

晶片設計日趨複雜是推動雲端設計的主要動力之一。Cadence雲端業務開發副總裁Craig Johnson指出(圖1),每種應用領域各有其需要解決的獨特問題。此外也有一些是關於改用先進製程節點、提升產能以及符合嚴苛時程要求等共通挑戰。像是5G這樣的領域追求對於整合極限的突破,因此從事此類設計的公司最為積極採用先進製程技術。這些業者需要製程所能提供的性能及處理能力,相應而來的問題是最新製程節點通常需要成熟時間,而在此過渡時期可能出現意料之外的狀況。至於AI設計的應用在於提供高度客製化的高性能晶圓,因此數量上持續成長,這為過去視為合併至多功能裝置的半導體產業帶來新的機會。

圖1 Cadence雲端業務開發副總裁Craig Johnson指出,雲端已受到越來越多的關注,而Cadence也推出各式雲端產品組合因應市場需求。

整體而言,雲端已受到越來越多的關注,已有許多企業正在評估研擬雲端策略。雲端資源吸引人之處在於能夠利用幾乎無限的運算資源,大幅提高產能並且加快產出時間,而毋須購入以約4年作為最大限度使用投資回報率的衡量標準。此外,企業可以選擇將其IT焦點從硬體的管理轉移到應用程式的管理。這些任務的區分可更趨明確,提升支出效益。

Cadence台灣區總經理宋栢安(圖2)則說,如今IC設計開始朝雲端發展,有幾個重要因素。首先是上述提到的,晶片設計愈來愈複雜的情形。隨著AI、5G和物聯網(IoT)等新興應用崛起,晶片的設計複雜度、難度明顯增加,而在難度大增的情況下,IC設計和分析所需的運算能力也越來越多。另一個原因則是為了因應短期而大量的設計需求,比如說當IC設計公司接到的案子是要在一個月內完成,但沒有這麼強大的系統因應晶片設計時所需的大量驗證與運算時,便可以租用雲端方案,採用雲端業者的高運算系統進行IC設計。

圖2 Cadence台灣區總經理宋栢安說明,雲端技術不僅提供高運算方案,也可因應短期且大量的產品設計需求。

像是新創晶片設計公司 SiFive已採用OIP VDE平台完成28奈米製程的單晶片設計。此設計架構由SiFive與Cadence於微軟Azure運算雲端平台上聯手完成,搭載SiFive自行開發的64位元多核開放原始碼指令集架構(Multi-Core...